# Contribution à la fiabilisation des interconnexions 3D dans le cadre du développement des capteurs photographiques

Stephane Moreau

#### ▶ To cite this version:

Stephane Moreau. Contribution à la fiabilisation des interconnexions 3D dans le cadre du développement des capteurs photographiques. Sciences de l'ingénieur [physics]. Université Grenoble Alpes (UGA), 2024. tel-04524276

# HAL Id: tel-04524276 https://cea.hal.science/tel-04524276

Submitted on 28 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# HABILITATION À DIRIGER DES RECHERCHES

Présentée par

# **Stéphane MOREAU**

préparée au sein du **CEA-LETI** proposée par le comité HdR **Électronique**, **Électrotechnique**, **Automatique** et **Traitement du signal** (**EEATS**) de l'Université de Grenoble Alpes

# Contribution à la fiabilisation des interconnexions 3D dans le cadre du développement des capteurs photographiques

Habilitation soutenue publiquement le "12/01/2024", devant le jury composé de :

#### M. Olivier THOMAS

Professeur, Université Aix-Marseille, Président

#### M. Alain BRAVAIX

Professeur et Directeur de Recherche, ISEN Yncréa Méditerranée Toulon, Rapporteur

#### M. Roland FORTUNIER

Professeur, Ecole Centrale de Lyon, Rapporteur

#### M. Guillaume PARRY

Maître de conférences hors classe, Grenoble INP, Rapporteur

#### **Mme Hélène FREMONT**

Professeur, Université de Bordeaux, Examinateur

#### M. Eric WOIRGARD

Professeur, Université de Bordeaux, Examinateur

#### Remerciements

« "Il n'est pas d'hiver sans neige, de printemps sans soleil, et de joie sans être partagée." »

Proverbe serbe

On ce moment charnière de ma carrière, je suis rempli d'une profonde gratitude envers ceux qui ont contribué à mon parcours académique et professionnel. Permettez-moi de prendre un instant pour exprimer mes sincères remerciements.

Tout d'abord, je tiens à adresser mes plus vifs remerciements aux rapporteurs Alain BRAVAIX, Roland FORTUNIER et Guillaume PARRY pour avoir consacré leur temps et leur expertise à évaluer mon travail avec rigueur et bienveillance. Leurs commentaires perspicaces ont été essentiels pour cette étape cruciale de ma vie académique.

Je souhaite également exprimer ma reconnaissance envers le président du jury, Olivier THO-MAS, pour sa capacité à guider les débats et pour m'avoir motivé à m'engager dans la démarche d'H.D.R. Un remerciement spécial va à Hélène FREMONT pour avoir accepté de diriger plusieurs thèses que je proposais, mais surtout pour m'avoir, elle aussi, encouragé dans la démarche de soutenir cette H.D.R. et d'avoir assumé le rôle de tutrice dont la guidance éclairée a été un phare dans la réussite de cette épreuve. Sa sagesse, son soutien et sa confiance en moi ont été des moteurs dans les moments difficiles.

À Éric WOIRGARD, je suis reconnaissant pour le trait d'union qu'il représente entre ma soutenance de thèse et celle d'H.D.R.!

Je souhaite également exprimer ma gratitude envers mes collègues du CEA-LETI, dont la collaboration et le partage de connaissances ont été des piliers essentiels de mon développement professionnel. Leur soutien constant et leurs encouragements ont contribué de manière significative à ma croissance en tant que chercheur.

À mes chers (anciens) étudiants, je vous adresse mes remerciements les plus chaleureux. Votre curiosité, votre engagement et votre enthousiasme ont été une source constante d'inspiration pour moi. Travailler avec vous a été une expérience enrichissante, et je suis reconnaissant pour les échanges stimulants que nous avons eus ensemble.

Enfin, je ne saurais terminer sans exprimer ma profonde reconnaissance envers mes proches. Leur soutien indéfectible et leur patience infinie ont été le socle sur lequel j'ai pu construire mes ambitions académiques et professionnelles. Leur présence à mes côtés a été ma plus grande source de force et de motivation.

À vous tous, je vous adresse mes plus sincères remerciements. Vos contributions ont façonné mon parcours et ont fait de cette étape un moment inoubliable; soutenir le jour de son anniversaire encore plus! Puissions-nous continuer à travailler ensemble vers de nouveaux horizons et à partager de nouvelles réussites.

| Texte rédigé | avec l'aide | de ChatGP! |

|--------------|-------------|------------|

| Tonte rearge | aree i arac | ac chatch. |

# Table des matières

|    | Rem   | nerciements                                                                         | i         |

|----|-------|-------------------------------------------------------------------------------------|-----------|

|    | Tabl  | e des matières                                                                      | iii       |

| In | trodu | action générale                                                                     | 1         |

| 1  | _     | loitation de la troisième dimension dans les circuits intégrés : origine, statut et |           |

|    | _     | blématiques d'un point de vue interconnexions et fiabilité                          | 4         |

|    | 1.1   | Courte histoire des interconnexions : de l'optimisation matériau à l'optimisation   | 5         |

|    |       | de l'architecture                                                                   | 5         |

|    |       | 1.1.1 La voie de l'architecture comme axe d'amélioration                            | 6         |

|    | 1.2   |                                                                                     | 10        |

|    | 1.2   |                                                                                     | 10        |

|    |       |                                                                                     | 11        |

|    |       |                                                                                     | 12        |

|    |       |                                                                                     | 12        |

|    | 1.3   | Notions de robustesse et de fiabilité pour les interconnexions électriques des cir- | _         |

|    |       |                                                                                     | 14        |

|    |       |                                                                                     | 15        |

|    |       |                                                                                     | 15        |

|    |       |                                                                                     | 17        |

|    |       | 1.3.4 Analyse de défaillance                                                        | 28        |

|    | 1.4   | La fiabilité des interconnexions 3D                                                 | 30        |

|    | 1.5   | Conclusion                                                                          | 32        |

| 2  | L'av  | vènement de l'intégration 3D dans les capteurs photographiques                      | 34        |

|    | 2.1   |                                                                                     | 35        |

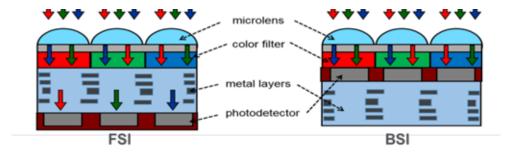

|    | 2.2   | Du F.S.I. au B.S.I. et de l'intégration 2D à l'intégration 3D                       | 36        |

|    | 2.3   | Conclusion                                                                          | 39        |

| 3  | Con   | tribution à l'amélioration de la robustesse et de la fiabilité du TSV               | <b>41</b> |

|    | 3.1   | Modes de défaillance de la brique TSV                                               | 12        |

|    | 3.2   | TSV et électromigration                                                             | 14        |

|    |       | $\cdot$                                                                             | 14        |

|    |       |                                                                                     | 15        |

|    |       |                                                                                     | 16        |

|    |       | 3.2.4 Évolution temporelle de la résistance, analyses de défaillance & analyses     | 1.6       |

|    |       | A                                                                                   | 16<br>10  |

|    |       |                                                                                     | 19<br>52  |

|    | 3.3   | 3.2.6 Loi d'extrapolation                                                           | , _       |

|    | ٥.٥   |                                                                                     | 55        |

|    | 3.4             | 3.3.1 Réalisation du banc de test                                                   | 55<br>57<br>62<br>64<br>69 |

|----|-----------------|-------------------------------------------------------------------------------------|----------------------------|

|    |                 |                                                                                     |                            |

| 4  |                 | tribution à l'amélioration de la robustesse et à la fiabilité des interconnexions à | 71                         |

|    | <b>base</b> 4.1 | de collage Cu/SiO <sub>2</sub>                                                      | 71<br>72                   |

|    | 4.1             | Du collage direct au collage hybride                                                | 73                         |

|    | 4.3             | Sensibilité à l'électromigration                                                    | 75<br>75                   |

|    | 7.5             | 4.3.1 Ère pré-industrielle                                                          | 75<br>75                   |

|    |                 | 4.3.2 Ère industrielle                                                              | 77                         |

|    |                 | 4.3.3 Étude de la corrélation entre temps à défaillance et volume de cuivre déplacé |                            |

|    | 4.4             | Sensibilité à la diffusion du cuivre                                                | 87                         |

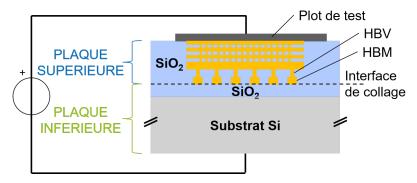

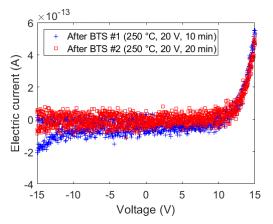

|    |                 | 4.4.1 Caractérisations BTS-TSV                                                      | 87                         |

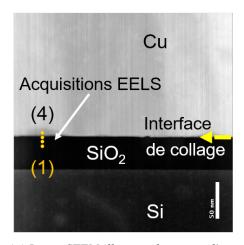

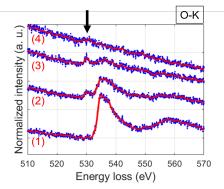

|    |                 | 4.4.2 Caractérisation EELS de la zone de désalignement, à l'interface de collage    | 91                         |

|    |                 | 4.4.3 Fiabilité diélectrique                                                        | 93                         |

|    | 4.5             | Conclusion                                                                          | 98                         |

| _  |                 |                                                                                     |                            |

| 5  |                 | imulation numérique comme aide à la compréhension de l'analyse défaillance          | 100                        |

|    | 5.1             | Simulation numérique et diffusion du cuivre à l'interface de collage                | 101                        |

|    |                 | 5.1.1 Modèles et équations associées                                                | 101<br>102                 |

|    |                 | <ul><li>5.1.2 Comparaison en 1D des 2 modèles</li></ul>                             | 102                        |

|    | 5.2             | Simulation numérique et interaction puce/boîtier                                    | 102                        |

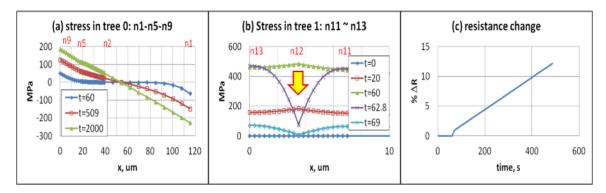

|    | 5.3             | Modélisation numérique et phénomène d'électromigration                              | 107                        |

|    | 3.3             | 5.3.1 Échelle locale & modélisation numérique de la dégradation par électromi-      | 107                        |

|    |                 | gration                                                                             | 107                        |

|    |                 | 5.3.2 Échelle circuit & modélisation numérique de la dégradation par électro-       |                            |

|    |                 | migration                                                                           | 109                        |

|    | 5.4             | Conclusion                                                                          | 112                        |

| C  | m alma          | ion cónórolo et norcacetivos de recherche                                           | 114                        |

| C  | oncius          | ion générale et perspectives de recherche                                           | 114                        |

|    |                 |                                                                                     | _                          |

| Bi | bliogi          | caphie caphie                                                                       | I                          |

|    |                 |                                                                                     |                            |

| A  |                 | F                                                                                   | XXI                        |

|    | A.1             | État civil                                                                          | XXII                       |

|    | A.2             | Parcours académique                                                                 | XXII                       |

|    | A.3             | Parcours professionnel                                                              | XXII                       |

|    | A.4             | Encadrement                                                                         | XXIII<br>XXIII             |

|    |                 |                                                                                     | XXIV                       |

|    |                 | A.4.2 Post-docs                                                                     | XXIV                       |

|    |                 | A.4.4 Publications et encadrements                                                  | XXV                        |

|    | A 5             | Rayonnement scientifique et actions à l'international                               | XXV                        |

|    | 11.0            | A.5.1 Publications marquantes                                                       | XXV                        |

|    |                 | A.5.2 Collaborations internationales                                                | XXV                        |

|    |                 | A.5.3 Insertion dans des réseaux                                                    | XXVI                       |

| A.5.4 | Invitations             | XXVI  |

|-------|-------------------------|-------|

| A.5.5 | Conférences et journaux | XXVII |

# Introduction générale

Le mémoire scientifique fait la synthèse d'un certain nombre de travaux de recherche que j'ai eu l'occasion de mener ou co-encadrer au sein du CEA-LETI dans le domaine de la fiabilité de l'intégration 3D entre 2008 et 2023. Ce document est organisé en 5 chapitres. Les résultats de ces travaux sont issus en grande partie des différentes thèses co-encadrées et également de projets de recherche en partenariat avec des industriels. La très grande majorité de ces travaux de recherche a été valorisée dans des articles de revues et de conférences internationales.

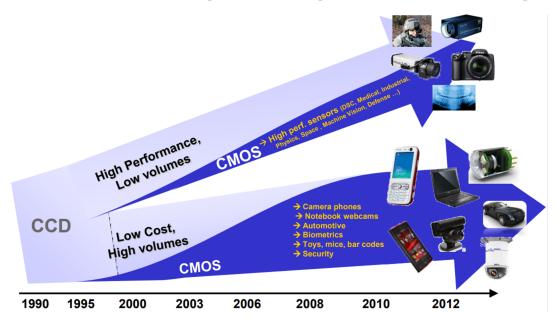

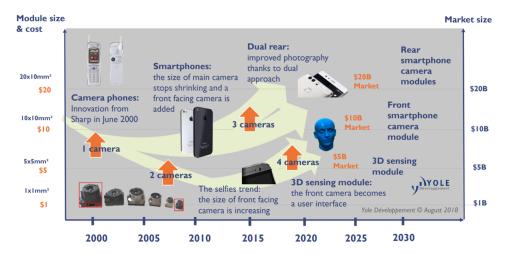

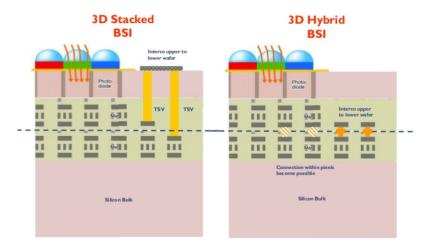

Les deux premiers chapitres sont des chapitres introductifs afin de contextualiser mon activité de recherche. Le chapitre 1 traite de l'exploitation de la troisième dimension dans les circuits intégrés. Ce chapitre retrace les grandes étapes de l'évolution des interconnexions des circuits intégrés au travers des changements des matériaux constitutifs, du passage d'une intégration planaire (2D) à une intégration tridimensionnelle (3D), accompagnée de l'arrivée de son lot de nouvelles interconnexions. Pour terminer, un certain nombre d'éléments relatifs à la robustesse/fiabilité des interconnexions, thème central de ce mémoire, seront apportés (vocabulaire, concepts...) car nécessaires à une lecture sereine des chapitres 3 à 5. Le chapitre 2 retrace succinctement les événements marquants de l'évolution du capteur photographique depuis le film « argentique » au capteur photographique numérique intelligent. Le capteur photographique numérique se trouve être l'application sous-jacente ayant nécessité les recherches présentées, de manière non-exhaustive, dans ce mémoire.

Les chapitres 3 à 5 constituent des chapitres de résultats d'études réalisées en propre ou que j'ai co-encadrées.

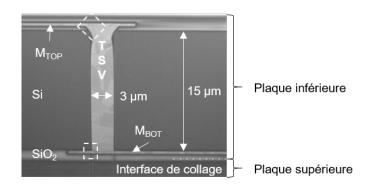

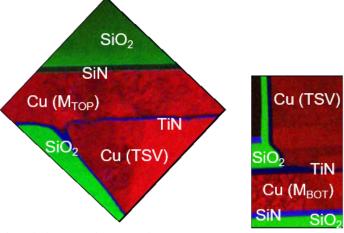

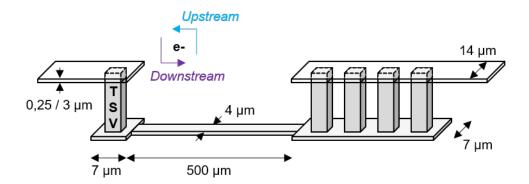

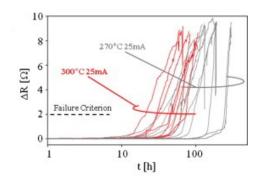

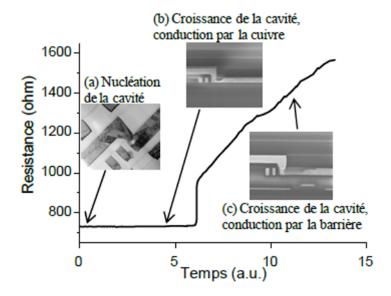

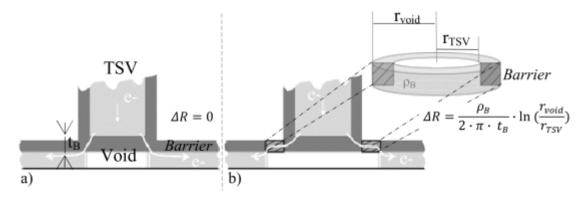

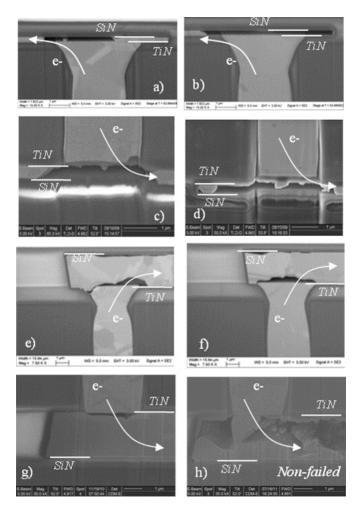

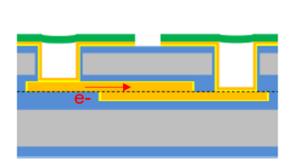

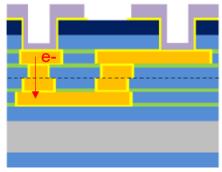

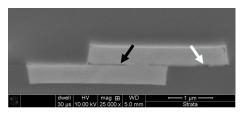

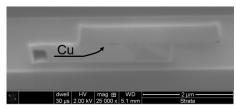

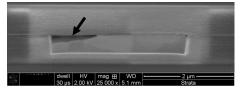

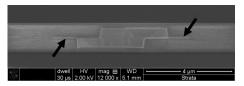

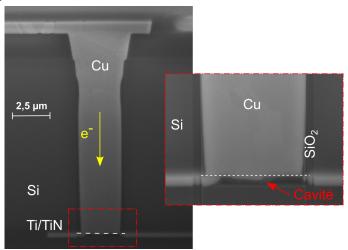

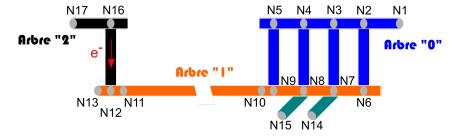

Le chapitre 3 aborde la robustesse et la fiabilité des vias traversant le silicium ou *Through Silicon Via* (TSV), figure de proue de l'intégration 3D-packaging. Après une succincte description des potentiels risques de défaillance de ces objets ou associés à ces objets, le chapitre traite principalement de la dégradation par électromigration du TSV-last Haute Densité. L'électromigration correspond de manière simpliste au déplacement d'atomes dans un conducteur induit par un flux d'électrons. Outre la localisation de la défaillance en fonction du sens de polarisation, la loi d'extrapolation des performances aux conditions normales d'utilisation est déterminée ainsi qu'un modèle analytique permettant de décrire l'évolution temporelle de la résistance électrique de la structure sous test. Ces résultats « post-mortem » sont confrontés à des résultats issus d'essais d'électromigration menés dans un microscope électronique à balayage pour obtenir une corrélation entre les cinétiques de la dégradation électrique et de la dégradation physique.

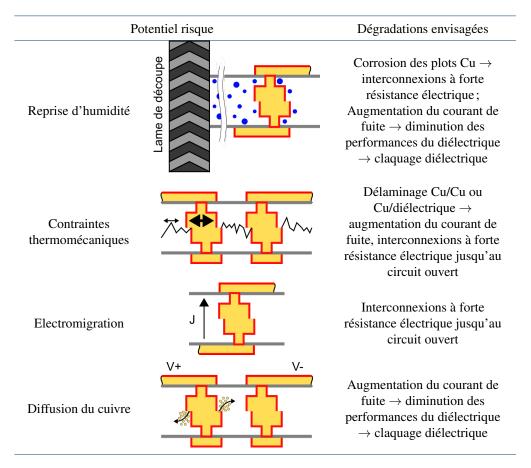

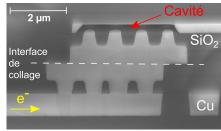

Le chapitre 4 change d'objet d'étude. On passe du TSV à une interconnexion à base de collage hybride. A l'image du chapitre précédent, le chapitre débute sur une succincte description des potentiels risques de défaillance de ce nouveau type d'interconnexion. Par la suite, des études relatives à une dégradation par électromigration ou par diffusion du cuivre dans la matrice oxyde environnante sont présentées.

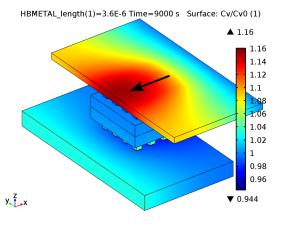

Le dernier chapitre (chapitre 5) est une rapide mise en lumière de l'emploi de la simulation numérique dans le contexte de ces études de robustesse/fiabilité. Ce sujet est traité selon 3

thématiques : la diffusion du cuivre dans l'intégration collage hybride, les contraintes thermomécaniques consécutives à l'interaction puce-boitier ou encore l'électromigration.

Ce mémoire ne déroge pas à la règle, il se termine par une partie « conclusion et perspectives ». Une courte conclusion rappelle les thèmes discutés et les principaux résultats obtenus. Le diplôme d'Habilitation à diriger des Recherches (HdR) sanctionnant la capacité à diriger des études scientifiques mais aussi à définir ces études, à aller chercher des financements pour les mener à bien..., la sous-partie « perspectives de travail » s'attellera à exposer des pistes de recherche ainsi que les moyens de les financer. Ce travail s'appuie bien évidemment sur les résultats présentés au gré des chapitres « résultats » mais aussi par l'analyse des orientations prises par la micro-électronique internationale et mes aspirations personnelles.

Exploitation de la troisième dimension dans les circuits intégrés : origine, statut et problématiques d'un point de vue interconnexions et fiabilité

| $\alpha$ |    |    |    | •  |   |

|----------|----|----|----|----|---|

| •        | Λľ | nn | ทก | ır | Δ |

| 17       | w  |    | па |    | C |

| 1.1 | Courte histoire des interconnexions : de l'optimisation matériau à l'optimisation de l'architecture |

|-----|-----------------------------------------------------------------------------------------------------|

|     | 1.1.1 La voie matériau comme axe d'amélioration                                                     |

|     | 1.1.2 La voie de l'architecture comme axe d'amélioration 6                                          |

| 1.2 | Les interconnexions de l'intégration 3D                                                             |

|     | 1.2.1 La bille de brasure, l'ancêtre des interconnexions 3D 10                                      |

|     | 1.2.2 Le via traversant le silicium                                                                 |

|     | 1.2.3 La ligne de redistribution des signaux électriques                                            |

|     | 1.2.4 Le collage moléculaire ou collage direct                                                      |

| 1.3 | Notions de robustesse et de fiabilité pour les interconnexions électriques                          |

|     | des circuits intégrés                                                                               |

|     | 1.3.1 Test de vie accélérée                                                                         |

|     | 1.3.2 Analyse statistique                                                                           |

|     | 1.3.3 Mécanismes et modes de dégradation des interconnexions électriques . 17                       |

|     | 1.3.4 Analyse de défaillance                                                                        |

| 1.4 | La fiabilité des interconnexions 3D                                                                 |

| 1.5 | Conclusion                                                                                          |

"un point de vue volontairement simpliste, le terme « interconnexion », appliqué au domaine de la micro-électronique, correspond à une ligne de métal à faible résistivité électrique (ou à conductivité électrique élevée) reliant différentes fonctions d'un circuit intégré (C.I.). Dans un cas strictement idéal, les interconnexions n'engendrent aucun délai de propagation du signal, prennent une place négligeable par rapport à la zone active/aux zones actives, sont bon marché et toujours fonctionnelles. L'expérience acquise depuis l'avènement de la micro-électronique ( $\sim$  60 ans) renvoie une réalité bien différente! L'enjeu perpétuel des interconnexions consiste à atteindre des valeurs de délai de propagation du signal ( $\tau = R \times C$ ), de dimensions, de coût et de fiabilité qui constituent un compromis acceptable pour leur mise en œuvre dans les circuits intégrés.

Ce chapitre se propose de retracer les grandes étapes de l'évolution de ces interconnexions au travers des changements des matériaux constitutifs, du passage d'une intégration planaire (2D) à une intégration tridimensionnelle (3D), accompagnée de l'arrivée de son lot de nouvelles interconnexions. Pour terminer, un certain nombre d'éléments relatifs à la robustesse/fiabilité des interconnexions, thème central de ce mémoire, seront apportés pour faciliter la lecture des chapitres suivants.

N. B.: la problématique des interconnexions étant très vaste (au niveau transistor, au niveau puce, au niveau boitier, au niveau carte électronique, etc.), dans ce document, nous nous limiterons à celles relatives au niveau « puce ».

# 1.1 Courte histoire des interconnexions : de l'optimisation matériau à l'optimisation de l'architecture

#### 1.1.1 La voie matériau comme axe d'amélioration

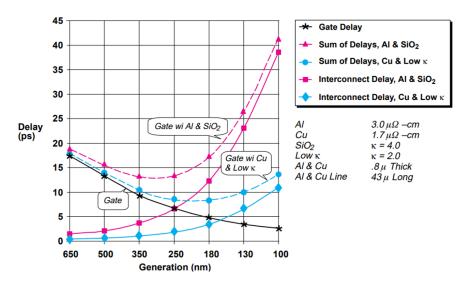

Depuis la création du premier circuit intégré (C.I.), en 1958 par Jacques Kilby, l'aluminium (Al) ou l'un de ses alliages (AlSi, AlCu) était le matériau principal des lignes d'interconnexions et l'oxyde de silicium (SiO<sub>2</sub>), le matériau d'isolation (matériau diélectrique) pour séparer ces dernières. L'avènement des circuits hautement intégrés (*Very Large Scale Integration*, VLSI) ont mis en lumière des limitations associées à la brique « interconnexion ». La limitation majeure concerne le délai de propagation du signal électrique  $\tau$  qui, à ces technologies avancées (250 nm et suivants), devient prépondérant devant le délai induit par la commande de la grille d'un transistor (cf. figure 1.1).

De ce constat, les industriels, IBM en tête en 1997 [IBM2011], ont été contraints de se tourner vers un nouveau matériau, le cuivre, pour les raisons suivantes :

- résistivité électrique plus faible que celle de l'aluminium; -35 % (respectivement 17 et 28.10<sup>-9</sup> Ohm.m) pour une interconnexion de même longueur, épaisseur et largeur;

- conductivité thermique plus importante autorisant une dissipation thermique plus importante;

- meilleure résistance au vieillissement par électromigration;

- meilleures propriétés thermomécaniques garantissant notamment une meilleure tenue aux contraintes de cisaillement et donc aux ruptures adhésives.

Cependant, l'introduction du cuivre a nécessité une complète revisite du procédé de fabrication. Très schématiquement, il a fallu passer de la gravure soustractive des métaux au remplissage additif de tranchées ou de trous avec du cuivre. Ce nouveau procédé de réalisation des interconnexions a pris le nom de procédé « damascène » en rapport avec le mode de fabrication des épées et couteaux à Damas (Syrie), au Moyen-Âge.

FIGURE 1.1 – Comparaison des contributions associées aux transistors et aux interconnexions en fonction de l'évolution des nœuds technologiques [source : ITRS - Technology Needs, 1997 Edition].

A cela s'ajoute le fait que le cuivre diffuse, sous forme atomique ou ionique, très facilement dans de nombreux matériaux de la micro-électronique annihilant tous les bénéfices de ce changement de matériau. Ainsi, il a fallu mettre en place des barrières pour garantir la fiabilité des circuits intégrés à interconnexions en cuivre.

En parallèle de ce changement, le diélectrique « conventionnel » a lui aussi évolué pour limiter l'explosion de ce délai de propagation du signal avec la réduction dimensionnelle des interconnexions. La composante capacitive de ce facteur peut être minimisée en passant à des matériaux à faible permittivité diélectrique ou low-k en anglais. Pour cela, le matériau diélectrique est rendu plus ou moins poreux en fonction des besoins. Le but étant de tendre vers une valeur de constante diélectrique relative ( $\varepsilon_r$ ) de 1. Les appellations low-k,  $ultra\ low$ -k (ULK),  $extreme\ low$ -k (ELK) voire  $air\ gap$  sont alors employées respectivement lorsque les constantes diélectriques relatives sont autour de 3, 2,5 et en-dessous de 2,5 voire proches de 1 dans le cas de l' $air\ gap$ . Cet exercice est d'autant plus difficile que plus la quantité de porosité s'accroît, plus le matériau diélectrique présente une tenue mécanique faible donc une fragilité accrue.

#### 1.1.2 La voie de l'architecture comme axe d'amélioration

Ces principales restrictions technologiques relatives aux interconnexions ont joué et jouent encore un rôle déterminant sur les performances des circuits intégrés actuels et futurs. Ces limitations avaient pour conséquence de freiner l'augmentation de la densité d'intégration, rendant cette stratégie industrielle dite *More Moore* plus coûteuse et donc avec un avenir incertain. Or, les circuits électroniques actuels ont des spécifications de plus en plus avancées, essentiellement pilotées par les applications grand public (applications portatives, calcul « haute performance », automobile électrique et/ou autonome...). Les spécifications électriques et environnementales de ces produits sont principalement dictées par une augmentation significative des performances et de la fonctionnalité des circuits. Ainsi, sans volonté de juger la dynamique de création d'un nouveau produit électronique, celui-ci se doit d'offrir toujours plus de puissance de calcul, d'être plus compact, de consommer moins d'énergie et cela pour un tarif identique à la génération précédente voire même plus faible. Du fait de la concurrence internationale, la phase de conception s'effectue souvent à marche forcée pour garantir un délai de mise sur le marché le plus court possible. En bout de chaine, le client final, consciemment ou non, s'attend à découvrir plus de fonctions qu'attendu. On a ainsi vu apparaître des fonctionnalités diverses intégrées sur une même puce, incluant

soit des technologies similaires, soit des technologies hétérogènes. Ces systèmes « tout-en-un » sont plus connus sous les appellations anglophones *System-on-Chip* (SoC) et *System-in-Package* (SiP) [Georgel2008]. Ils doivent être compris comme étant deux systèmes d'intégration complémentaires. Leur important développement leur fait jouer un rôle prépondérant dans les applications grand public actuelles. Néanmoins, les systèmes sur puce (SoC) se trouvent limités par leur grande complexité de conception, une des principales problématiques actuelles de la démarche de progression *More Moore*, et les systèmes en boîtier (SiP) doivent faire face à une mise en boîtier (*packaging*) de plus en plus complexe à réaliser et donc coûteuse, ce qui constitue la limite principale des systèmes hétérogènes de la démarche *More than Moore*.

Cependant, malgré les efforts fournis, les limites physiques de ces deux voies d'évolution approchent. Pour dépasser ce problème, un nouveau mode de conception des puces électroniques a émergé depuis une quinzaine d'années même si le concept est bien plus ancien [Lau2011, Kada2015]: l'utilisation de la troisième dimension.

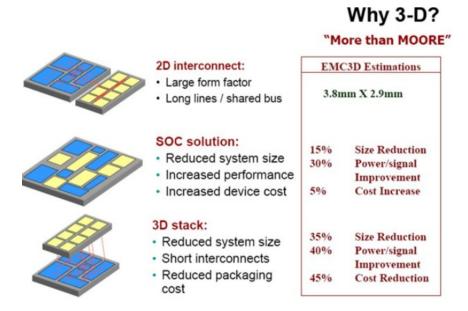

L'intégration 3D consiste, dans sa version la plus perfectionnée, en l'empilement de circuits intégrés hétérogènes, c'est-à-dire des circuits intégrés présentant des technologies et des fonctionnalités différentes. Cette nouvelle architecture/intégration a été avant tout développée afin de réduire l'encombrement du circuit final, de diminuer la longueur des interconnexions et ainsi limiter les pertes par effet Joule et par conséquent les délais de transmission en comparaison d'un circuit 2D équivalent [Rousseau2009]. Pour illustrer ces propos, reprenons des estimations (cf. figure 1.2) présentées dans la feuille de route 2009 de l'ITRS pour l'assemblage et le packaging sur la base d'une intégration 2D présentant une surface de 3,8 mm × 2,9 mm [ITR2009]. Ainsi, on pourrait s'attendre, par le passage à une intégration 3D, à une réduction de 35 % de la surface du nouveau circuit intégré, une amélioration de 40 % d'un point de vue puissance du signal et même une réduction de 45 % du coût de la mise en boîtier. Bien évidemment, la réalité est un peu plus complexe...

FIGURE 1.2 – Avantages d'un passage d'une intégration planaire (2D) à une intégration verticale dite intégration 3D. Source : [ITR2009].

Si l'intégration 3D n'a pas été appliquée plus tôt, c'est qu'elle nécessite un investissement initial colossal pour développer les nouveaux procédés de fabrication qu'elle requiert. En effet, il est nécessaire de développer de nouveaux procédés et de nouvelles technologies pour assurer les connexions qui permettent une communication électrique verticale entre chaque puce. Citons à ce propos, les vias traversant le silicium (*Through Silicon Vias*, TSV), les microbilles ou équivalents (pilier de cuivre, micro-insert, *stud bump*), le collage hybride et par extension la couche de

Chapitre 1. Exploitation de la troisième dimension dans les circuits intégrés : origine, statut et problématiques d'un point de vue interconnexions et fiabilité

redistribution du courant (ReDistribution Layer, RDL).

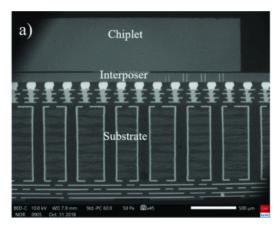

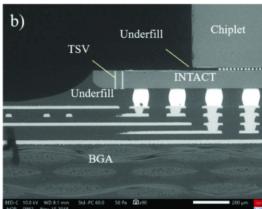

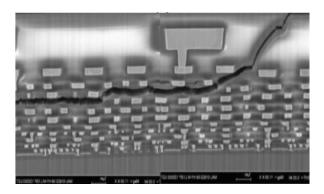

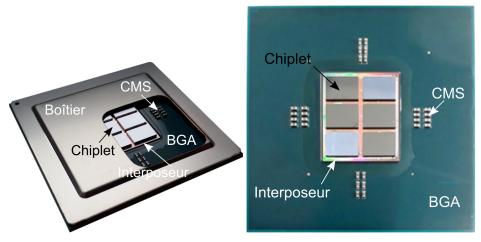

La figure 1.3 présente une partie de ces interconnexions dans le cadre d'un <u>Interposeur Actif</u> (IntAct) développé pour les besoins du « calcul haute performance » [Coudrain2019]. Cet objet, issu des travaux du programme 3D de l'IRT Nanoelec, illustre parfaitement la complexité d'un assemblage 3D et notamment ses différentes échelles : du transistor (nanomètre) à la bille de brasure (centaine de micromètres) en passant par le TSV (micromètre). Même si en première approche, un béotien pourrait croire qu'il suffit de percer des trous dans les puces, de les remplir de métal pour avoir une conduction électrique face avant/face arrière et de coller des puces entre elles pour aboutir à cette fameuse intégration 3D, la réalité est évidemment tout autre. Il faut en effet maîtriser un nombre très conséquent de paramètres pour garantir la fabrication d'un tel assemblage ainsi que ses performances électriques, thermiques... et au final sa fiabilité.

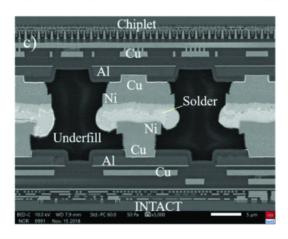

FIGURE 1.3 – Prototype d'interposeur actif ou IntAct, issu des travaux du programme 3D de l'IRT Nanoelec, pour les applications de type « calcul haute performance ». IntAct illustre la complexité d'un assemblage 3D et ses différentes échelles : a-b) puce multi-processeurs (épaisseur : 600 µm) reportée sur un interposeur actif fin (100 µm), lui-même reporté sur boîtier à matrice de billes (Ball Grid Array, BGA). TSV (diamètre : 10 µm, hauteur : 80 µm), micro-piliers de cuivre (10 µm de diamètre) et billes de brasure (80 µm de diamètre) c) zoom à l'interface puce/interposeur actif et notamment les micro-piliers de cuivre, le BEoL de la puce et de l'interposeur actif. Source : [Coudrain2019].

#### 1.2 Les interconnexions de l'intégration 3D

#### 1.2.1 La bille de brasure, l'ancêtre des interconnexions 3D

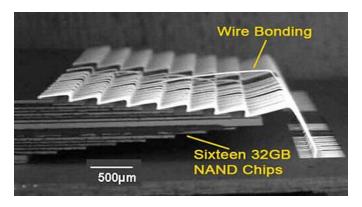

Même si le TSV a apporté une rupture technologique et transparaît actuellement comme l'interconnexion emblématique de l'intégration 3D, reconnaissons que les microbilles ou leurs équivalents sont les premières interconnexions autorisant l'empilement vertical de puces même si le câblage filaire permet de réaliser de belles choses comme illustré sur la figure 1.4.

FIGURE 1.4 – Exemple de câblage filaire avancé réalisé par Toshiba dans le cadre d'une mémoire NAND de 64 Go présentant 16 puces empilées, amincies à 30 µm. Source : [Handy2010].

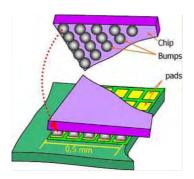

L'avènement de la technologie de report dite *flip chip* a été une étape importante de cette miniaturisation. Cette technologie, de soudage collectif de billes de brasure (cf. figure 1.5), a permis aux concepteurs de puces d'augmenter le nombre d'entrées/sorties (E/S) en les distribuant sur toute la surface de la puce par rapport à la technologie de liaison par fil qui n'utilisait que sa périphérie. L'utilisation de toute la surface de la matrice a permis de réduire la taille de la matrice et en même temps d'augmenter sa fonctionnalité.

FIGURE 1.5 – Illustration schématique de la technologie flip chip. Source : [Pedder2010].

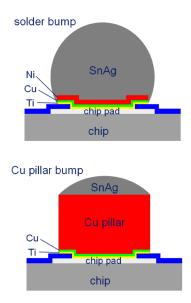

Cette technologie a bien évolué en 60 ans d'existence. Cette évolution peut-être divisée en 2 générations. La première génération a généralement un pas d'interconnexion supérieur à 40 µm et correspond, peu ou prou, à la bille de brasure de l'emblématique *Controlled Collapse Chip Connection* ou C4 d'IBM (cf. figure 1.6, schéma du haut). La deuxième génération, nommée usuellement pilier de cuivre, a été développée pour obtenir des pas d'interconnexion inférieurs à 40 µm (cf. figure 1.6, schéma du bas). La forme du pilier permet un rapport élevé entre la hauteur et le diamètre du pilier, permettant ainsi un pas d'interconnexion très serré même lorsque les hauteurs des cylindres sont importantes. Parfois, un capuchon de soudure est formé sur le sommet du pilier pour aider à la connectivité avec la puce à reporter. La capacité de dissiper la chaleur est un autre avantage de cette technologie, ce qui en fait de bons candidats pour les applications hautes performances. La hauteur du pilier peut varier de 5 à 100 µm pour un diamètre de 10 à

100 μm voire plus. La plupart des piliers actuellement en production ont une hauteur supérieure à 20 μm [AMK2019, CHI2022, SHI2022, SPI2022].

FIGURE 1.6 – Schéma de principe (haut) d'une bille de brasure et (bas) d'un pilier de cuivre. Source : [Ebersberger2008].

Ainsi, on voit très bien que le pilier de cuivre n'est que le petit frère des billes de brasure et que le premier étage de la fusée *intégration 3D*!

#### 1.2.2 Le via traversant le silicium

Le second étage de cette fusée est le via traversant le silicium, figure de proue emblématique de l'intégration 3D. Cet élément n'est pas une idée récente puisqu'il est au cœur du brevet américain n°3044909, datant du 23 octobre 1958, du prix Nobel de Physique de 1956, Wiliam Shockley [Lau2011]. A l'époque, on ne parlait encore que de trou dans le silicium et l'idée n'intervenait pas dans le contexte d'un empilement de circuits (intégration 3D).

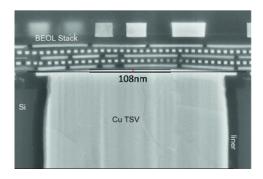

Le via traversant le silicium, plus connu sous l'acronyme anglophone TSV pour *Through Silicon Via* est une interconnexion qui relie électriquement le BEoL de la face avant et la couche de redistribution des signaux électriques (*Redistribution Layer*, RDL) de la face arrière. Sa hauteur est donc égale à l'épaisseur de silicium de la puce qui est elle même définie en fonction de l'application finale. Elle varie de quelques micromètres pour en atteindre quelques centaines.

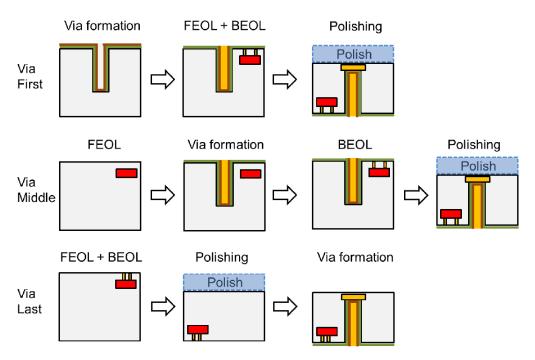

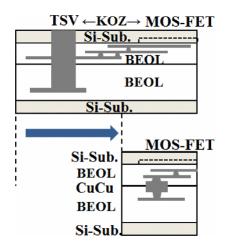

Trois voies d'intégration sont généralement définies et illustrées schématiquement à la figure 1.7 [Malta2014,Gambino2015] : via-first, via-middle et via-last. La première intègre les TSV avant le FEoL, la seconde après le FEoL mais avant le BEoL, et la dernière après le FEoL et le BEoL. Le choix d'un schéma d'intégration dépend du cahier des charges du produit final. L'approche TSV-first n'est plus considérée comme une option viable en raison de limitations inhérentes, principalement, à la résistance électrique du TSV ainsi fabriqué. En effet, cette approche nécessite l'utilisation de polysilicium comme conducteur en raison des exigences de compatibilité avec les procédés de fabrication du FEoL et les températures élevées que le TSV doit pouvoir supporter pendant ces étapes de fabrication. Pour contrer cet effet, des vias à large diamètre (> 100 µm) sont fabriqués limitant de fait les applications aux MEMS ou encore à certains capteurs photographiques. Le choix entre une approche TSV-last et une approche TSV-middle est réalisé essentiellement en fonction des contraintes applicatives du futur circuit intégré desquelles vont découler des contraintes en terme de densité d'interconnexions et valeur de résistance par interconnexion.

FIGURE 1.7 – Illustration des 3 voies d'intégration du TSV : via-first, via-middle ou via-last. Ces voies se distinguent par la chronologie de fabrication du TSV (grand pilier rectangulaire orange) eu égard à la fabrication du FEoL (rectangle rouge) et du BEoL (petits piliers oranges). Source : [Singulani2014].

#### 1.2.3 La ligne de redistribution des signaux électriques

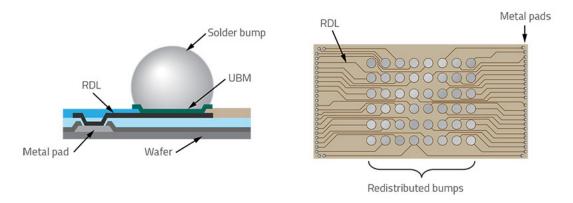

Le corollaire de cette densification a été le développement d'un nouveau niveau métallique, en surface des puces, afin d'assurer une redistribution des signaux entre les niveaux enfouis et les TSV et/ou les micro-billes/piliers de cuivre (cf. figure 1.8). La couche de redistribution ou *Redistribution Layer* (RDL) en anglais joue ce rôle.

FIGURE 1.8 – Schéma de principe d'une ligne de redistribution ou RDL, vue en coupe (gauche) et de dessous (droite). Source : [Lepedus2018].

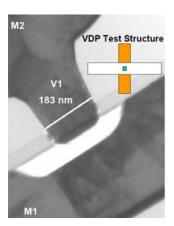

#### 1.2.4 Le collage moléculaire ou collage direct

La technologie TSV bien que mature semble limitée à son tour pour répondre aux exigences les plus sévères en terme de densité d'intégration du fait de son encombrement relativement important même si de nouveaux développements avec des amincissements extrêmes des substrats pourraient

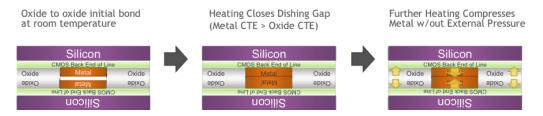

changer la donne [Jourdain2020]. A cela s'ajoute le fait que le remplissage métallique du TSV est complexe et nécessite un solide savoir-faire. Pour surmonter ces limitations, les acteurs du milieu ont commencé à chercher d'autres solutions. Un premier pas en avant vers une nouvelle façon d'empiler des puces a été la technologie ZiBond® développée par Ziptronix (maintenant XPeri), une variante du collage direct oxyde-oxyde qui met en jeu un procédé plaque à plaque basse température (150-300 °C). La seconde évolution a été de combiner le collage direct oxyde-oxyde local avec du collage direct métal-métal local, plus communément appelée aujourd'hui « collage hybride », afin d'obtenir une connexion électrique entre une plaque supérieure et une plaque inférieure. Cela a amené à la technologie DBI®, pour *Direct Bond Interconnect*, en 2005 (cf. figure 1.9). La technologie a été transférée sous licence à des clients industriels et académiques, citons à ce titre Sony, Omnivision, le Fermilab, l'institut Fraunhofer EMFT...

FIGURE 1.9 -« Collage hybride » selon le procédé  $DBI^{\otimes}$  de la société XPeri. Source : [von Trapp2018].

En parallèle, des instituts de recherche ont développé leur propre technologie :

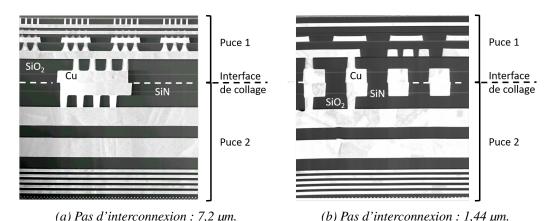

- L'IMEC a opté pour un collage Cu/SiCN. Celui-ci permet d'abaisser la température du recuit de collage et potentiellement empêcher la diffusion du cuivre à l'interface de collage en cas de désalignement. La seconde particularité est l'utilisation de plots de différentes tailles. Les plots de la puce supérieure sont plus petits que ceux de la puce inférieure afin de garantir un contact total malgré le désalignement intrinsèque. Un pas d'interconnexion record de 720 nm a été atteint par cet institut de recherche [Beyne2017].

- Le CEA-LETI associé à STMicroelectronics a commencé à développer le collage hybride en 2008 [Di Cioccio2008]. Les derniers travaux publiés font état d'un pas d'interconnexion de 1,44 μm [Jourdon2018, Ayoub2020]. Plus d'informations seront données au chapitre 4.

# 1.3 Notions de robustesse et de fiabilité pour les interconnexions électriques des circuits intégrés

Le passage du stade de la preuve de concept à un produit commercialisable est conditionné non seulement par la réalisation maîtrisée des différentes étapes technologiques mais également la gestion des nouvelles contraintes générées par ces nouvelles interconnexions notamment d'un point de vue robustesse ou fiabilité.

Pour illustrer ces propos, prenons 3 exemples :

- 1. La réalisation du TSV nécessite l'amincissement des puces qui entraîne la diminution de leur rigidité mécanique. Cet amincissement a également des conséquences d'un point de vue thermique, puisque la quantité de silicium pour dissiper la chaleur générée par le fonctionnement du circuit se réduit. De très nombreux phénomènes de dégradation étant thermiquement activés, se pose un problème de robustesse/fiabilité.

- 2. Ce même TSV, du fait de son empreinte physique, génère des contraintes thermomécaniques qui peuvent perturber le fonctionnement des dispositifs actifs (FEoL) situés à proximité en changeant la mobilité des porteurs des composants MOS. Si ce fait est avéré, il est nécessaire de définir des zones d'exclusion (*Keep out Zone*, KOZ) autour de ces TSV sous peine d'avoir de mauvaises performances électriques et potentiellement un problème de robustesse/fiabilité.

- 3. Le collage hybride quant à lui, du fait du désalignement, inhérent à la précision d'alignement des équipements (200 nm à ±3σ pour une approche plaque à plaque), présente, a priori, une faiblesse d'un point de vue diffusion du cuivre des interconnexions dans la matrice oxyde environnante. Le cuivre étant connu pour être néfaste à la fiabilité des oxydes se pose en conséquence la question de la robustesse/fiabilité du collage hybride de ce point de vue.

Ainsi, ce qui pourrait passer pour de petites évolutions technologiques, peut avoir des conséquences plus ou moins importantes en termes de robustesse/fiabilité et doivent donc être évaluées et quantifiées de ce point de vue.

Qu'entendons-nous par fiabilité? Même si tout le monde emploie le terme « fiabilité » de nos jours, ce terme est souvent utilisé de manière inappropriée. Clarifions les choses en donnant une définition. L'agence française de normalisation ou AFNOR définit la fiabilité comme « l'aptitude d'une entité à accomplir une fonction requise, dans des conditions données, pendant un intervalle de temps donné » [AFN1988]. Naturellement, découlent de cette définition plusieurs notions comme le profil de mission, la défaillance et ses corollaires que sont la durée de vie et le critère de défaillance.

La défaillance est définie simplement comme étant la « cessation de l'aptitude d'une entité à accomplir une fonction requise » [AFN1988].

Une bonne illustration de cette notion de fiabilité est cette annonce de recrutement de la SCNF de 2009 (cf. figure 1.10) où l'on retrouve les notions de profil de mission (1 train toutes les 2 min), de durée de vie (100 ans) et en conséquence de fiabilité et de critère de défaillance.

FIGURE 1.10 – Fiabilité et annonce de recrutement à la S.N.C.F. Source : [COOLTURE2009].

Le critère de défaillance consiste donc au franchissement d'une limite par l'état du système considéré. Il peut s'agir d'un état de ruine de la structure correspondant à une défaillance phy-

sique, on parle alors de dégradation catastrophique, ou d'un état correspondant en fait à un fonctionnement dégradé mais encore acceptable. Le critère de défaillance est fixé arbitrairement ou est fonction du cahier des charges du futur produit par exemple.

Comme indiqué peu avant, l'utilisation du terme fiabilité est souvent galvaudée. Par exemple ce mot est employé en lieu est place des termes « qualification » ou « robustesse ». La norme JE-DEC JEP148B [JED2014] définit respectivement ces 2 termes comme : « processus consistant à démontrer qu'une entité est capable de satisfaire ou de dépasser les exigences spécifiées » et « capacité à fonctionner correctement ou à ne pas tomber en panne dans des conditions d'application et de production variables ». De manière grossière, la fiabilité permet de déterminer des durées de vie quant aux 2 autres, il ne s'agit que de savoir si l'on passe avec succès des tests normatifs.

#### 1.3.1 Test de vie accélérée

Les tests de vie accélérée (*Accelerated Life Test*, ALT) sont des essais de vieillissement d'un objet (structure de test comme futur produit) en le soumettant à des conditions (température, tension, irradiation, fréquence de vibration, pression...) au-delà de ses conditions normales d'utilisation aussi bien en termes d'amplitude que de fréquence de sollicitation. En effet, dans des conditions normales d'utilisation, si un C.I. doit pouvoir fonctionner 10 ans sans connaître de défaillance, il n'est pas envisageable, principalement pour des raisons de vitesse de mise sur le marché mais également de coût (mobilisation d'un banc de test, d'un local...), de mener des essais de vieillissement pendant 10 ans afin de confirmer une telle fiabilité. Pour répondre à la question, des essais de vieillissement accélérés sont menés avec une ou plusieurs variables d'accélération.

Les méthodes d'essai accélérées peuvent être « qualitatives » ou « quantitatives ».

- 1. Les tests qualitatifs accélérés (*Highly Accelerated Life Test*/HALT, *Highly Accelerated Stress Test*/ HAST...) sont principalement utilisés pour révéler les modes de défaillance probables de l'objet d'étude afin que, par exemple, les ingénieurs « produit » puissent améliorer la conception du produit.

- 2. Les tests quantitatifs de vie accélérée (Quantitative Accelerated Life Test, QALT) sont conçus pour produire les données nécessaires à l'analyse des données de vie accélérée. Cette méthode d'analyse utilise des données de vie obtenues dans des conditions accélérées pour extrapoler, via une loi d'accélération, une fonction de densité de probabilité estimée (Probability Density Function, PDF) pour l'objet en question dans des conditions normales d'utilisation.

En conséquence, un test accéléré de durée de vie permet de répondre aux types de questions suivants :

- A quel moment cet objet devrait-il présenter une défaillance?

- Quel est l'effet de telle ou telle variable d'accélération sur la durée de vie d'un produit?

- Quels sont les paramètres qui maximisent la durée de vie du produit?

Le facteur d'accélération ne doit cependant pas être trop important car :

- l'invariance du facteur de forme (un seul mécanisme de défaillance) doit être conservée,

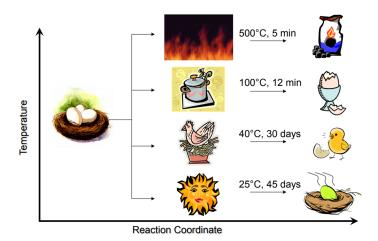

- on ne doit pas engendrer de mécanismes de défaillances que l'on ne verrait pas aux conditions normales d'utilisation, comme illustré à la figure 1.11.

#### 1.3.2 Analyse statistique

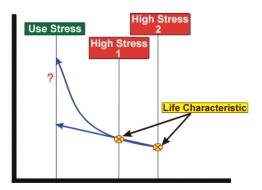

Les statisticiens, les mathématiciens et les ingénieurs ont développé des modèles de relation « durée de vie-contrainte » qui permettent à l'analyste d'extrapoler une fonction de densité de

FIGURE 1.11 – *Illustration du risque d'accélération dans une étude quantitative de vie accélérée. Source : [Sorensen2015].*

probabilité aux conditions normales d'utilisation à partir de données de vie obtenues à des niveaux accrus de contraintes (cf. figure 1.12). Ces modèles décrivent le cheminement d'une durée de vie particulière de la distribution, appelée usuellement durée de vie caractéristique, d'un niveau de contrainte à un autre. Pour la distribution de Weibull et la la distribution log-normale, la valeur de cette durée de vie caractéristique est obtenue respectivement à 63,2 % et 50 % de dégradation. Toute la difficulté est de choisir la bonne distribution statistique pour décrire la répartition des dégradations puisqu'elle conditionne à la fois l'extraction de la durée de vie caractéristique mais également l'extrapolation aux conditions normales d'utilisation.

FIGURE 1.12 – Illustration de l'extrapolation par un modèle de relation « durée de viecontrainte » des performances aux conditions normales d'utilisation à partir de données issues d'essais de vie accélérés. Source : [ReliaSoft Corporation2015].

Le praticien doit choisir une relation durée de vie-contrainte qui correspond au type de données analysées. Les relations « durée de vie-contrainte » disponibles incluent à titre d'exemples les modèles d'Arrhenius, d'Eyring et de loi de puissance inverse. Ces modèles sont conçus pour analyser les données avec un type de contrainte (par exemple, la température, l'humidité ou la tension). Alternativement, les relations température-humidité et température-contrainte non thermique sont des modèles combinés qui sont utilisés pour analyser les données avec deux types de contraintes (par exemple, température et tension, température et humidité).

Il est important de noter que nombre de ces relations ou modèles sont dits phénoménologiques, c'est-à-dire qu'ils expriment mathématiquement le résultat de l'observation d'un phénomène sans s'attarder à sa signification fondamentale. C'est principalement pour cette raison que la recherche des lois statistiques sous-jacentes, la vérification de l'indépendance des variables d'accélération, le cas échéant, ne sont souvent pas connues et/ou traitées. Comme l'écrivait le statisticien George

Box, « tous les modèles sont faux, mais certains sont utiles » [Box1976, Box1987]! L'aphorisme reconnaît ainsi que les modèles statistiques/scientifiques sont toujours en deçà des complexités de la réalité mais peuvent toujours être utiles. Pour illustrer ce fait, à titre d'exemple, prenons la loi de Black propre aux dégradations par électromigration qui est une relation durée de vie-contrainte de type température-contrainte non thermique (température-courant électrique, cf. paragraphe 1.3.3). De nombreuses études ont montré très rapidement son incapacité à décrire finement de nombreux résultats expérimentaux mais malgré ce constat, depuis 50 ans, cette loi est utilisée de par sa facilité de mise en œuvre.

#### 1.3.3 Mécanismes et modes de dégradation des interconnexions électriques

En premier lieu, clarifions les termes « mécanisme » et « mode défaillance » pour lever toute ambiguïté. Ainsi, la norme NF X60-011 [AFN1981], bien que obsolète, définissait ces 2 expressions de la manière suivante :

- Mécanisme de défaillance : processus physiques, chimiques ou autres qui conduisent ou ont conduit à une défaillance,

- Mode de défaillance : effet par lequel une défaillance se manifeste.

Ci-après sont présentés de manière succincte et non exhaustive les mécanismes de défaillance et les modes de dégradation associés aux interconnexions 3D.

#### Electromigration

L'électromigration étant le mécanisme de dégradation au cœur de ma thématique de recherche, volontairement la partie introductive qui lui est consacrée et plus conséquente que pour les autres mécanismes.

**Historique** L'électromigration est un mécanisme de transport de matière observé dans les métaux traversés par de fortes densités de courant. Ce phénomène est décrit pour la première fois en 1861 par un chercheur français, M. Gérardin. Mais ce n'est qu'à la fin des années 1960 qu'un réel tournant est marqué avec l'apparition des premiers circuits intégrés, dont la durée de fonctionnement n'est que de quelques semaines. L'électromigration y est identifiée comme la cause de la défaillance des interconnexions en aluminium qui transportent des densités de courant pouvant aller jusqu'à  $1 \ MA/cm^2$  [Blech1966]. A titre d'exemple, les câbles métalliques conventionnels transportent des densités de courant de l'ordre de  $1 \ kA/cm^2$  [DIN2013]. Le phénomène d'électromigration y est totalement négligeable; leur utilisation est en fait limitée par l'auto-échauffement par effet Joule, pouvant entraîner la fusion des lignes. Dans le cas des interconnexions des circuits intégrés, l'auto-échauffement n'est plus un problème car la chaleur peut se dissiper via le silicium. Par contre, à ce niveau de densité de courant, l'électromigration devient le mécanisme de défaillance dominant.

Depuis 70 ans, avec la diminution constante de leur section, les interconnexions sont soumises à des densités de courant croissantes et donc une sensibilité accrue à la dégradation par électromigration. Ce phénomène de dégradation fait l'objet de nombreuses études. Celles-ci se concentrent sur la compréhension de la cinétique de dégradation et sur le développement de procédés de fabrication permettant d'améliorer la fiabilité des lignes métalliques. Du point de vue des procédés de fabrication, deux améliorations majeures sont ainsi intervenues. La première est l'utilisation de l'alliage AlCu, en remplacement de l'aluminium pur, ce qui a grandement amélioré la durée de vie des interconnexions. L'incorporation d'une faible quantité de cuivre (jusqu'à ~4 % atomique) [Tao1991, Shih1995] a permis de limiter la diffusion par les joints de grains qui sont le principal chemin de diffusion pour l'aluminium. En 1997, un changement radical intervient avec l'introduction du cuivre par IBM [IBM2011]. Comme vu précédemment (cf. partie 1.1.1, p. 5) ce choix est notamment justifié par une meilleure conductivité électrique, comparé à l'aluminium,

mais aussi à sa meilleure résistance à la dégradation par électromigration et ainsi augmenté la durée de vie des lignes métalliques [Alam2005].

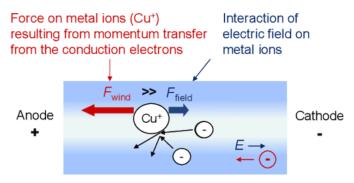

Physique de l'électromigration Le champ électrique appliqué à une interconnexion pendant le fonctionnement du C.I. polarise le mouvement net des ions métalliques dans la direction du flux d'électrons (c'est-à-dire de la cathode à l'anode). Ce flux net d'atomes est causé par l'électromigration, qui peut être décrite comme l'auto-diffusion des ions métalliques en réponse à un champ électrique. Le flux atomique est principalement le résultat de deux forces d'entraînement opposées : la force du vent électronique déplaçant les ions dans la direction du flux d'électrons et une force contraire qui pousse les ions dans la direction opposée (cf. figure 1.13).

FIGURE 1.13 – Illustration des forces en jeu dans le phénomène d'électromigration. Deux forces agissent sur les ions métalliques qui composent le réseau du matériau d'interconnexion. L'électromigration est le résultat de la force dominante, c'est-à-dire du transfert de la quantité de mouvement des électrons qui se déplacent dans le champ électrique appliqué. Source : [Lienig2018b].

Le flux atomique (J) peut être décrit par l'équation suivante, dans un problème unidimensionnel (1D) :

$$J = -\frac{DC}{k_B T} \times \left( Z^* e E - \Omega \frac{d\sigma_H}{dx} \right)$$

(1.1)

D étant la diffusivité thermique atomique  $(m^2/s)$ , C, la concentration atomique  $(1/m^3)$ ,  $k_B$ , la constante de Bolzmann (eV/K), T, la température (K),  $Z^*$ , la charge effective apparente (sans unité), e, la charge élémentaire  $(A \times s)$ , E, le champ électrique (V/m),  $\Omega$ , le volume atomique  $(m^3)$  et  $\sigma_H$ , la contrainte hydrostatique (Pa).

L'électromigration est bel et bien un problème de fiabilité car pouvant conduire à une défaillance des interconnexions. Les défaillances se produisent sur des sites de divergence de flux atomique, c'est-à-dire où le flux net d'atomes est non nul. Aux sites où il y a un manque d'atomes métalliques, les contraintes mécaniques locales deviennent de plus en plus de traction, ce qui peut éventuellement conduire à l'apparition de cavités dans l'interconnexion une fois qu'une valeur critique de contrainte de traction est atteinte ( $\sigma_{crit}$ ). Dans le cas d'interconnexions de type BEoL, ces dernières sont entourées de couches de matériaux réfractaires (SiN, SiC, SiCN...). Le courant électrique peut passer à travers ces couches une fois qu'une cavité s'est formée. Du fait d'une résistance électrique supérieure de ces matériaux, un saut de résistance est observé. Cette augmentation peut devenir trop élevée par rapport au cahier des charges « produit », moment auquel l'interconnexion sera alors considérée comme défaillante. A l'extrême, cet état peut conduire à la défaillance par circuit ouvert. Aux sites où il y a une nette accumulation d'atomes, les contraintes locales deviennent de plus en plus compressives, ce qui peut conduire à la formation d'extrusions métalliques. Une défaillance par court-circuit peut se produire si le métal extrudé touche une interconnexion voisine.

Le lecteur soucieux d'en apprendre plus sur la physique de l'électromigration pourra se reporter, par exemple, aux ouvrages suivants : [Ohring1998a, Tan2010c, Doyen2009].

Tests accélérés et extrapolation aux conditions normales d'utilisation Comme décrit précédemment (cf. parties 1.3.1, p. 15 et 1.3.2, p. 15), l'évaluation de la résistance au phénomène d'électromigration passe par des tests accélérés en termes de température et de densité de courant dont les résultats sont ensuite extrapolés aux conditions normales d'utilisation. Cette extrapolation repose très généralement sur la loi empirique issue des travaux de J. R. Black [Black1967]. Ce modèle relie le temps moyen à la défaillance (*Mean Time To Failure*, MTTF) à la température et à la densité de courant de la manière suivante :

$$MTTF = \frac{A}{J^n} \times \exp\left(\frac{E_a}{k_B T}\right) \tag{1.2}$$

où A est une constante déterminée empiriquement, J, la densité de courant électrique  $(A/m^2)$ , n, l'exposant de dépendance à la densité de courant électrique,  $E_a$ , l'énergie d'activation (eV/K) associée à la dégradation par électromigration, les paramètres restants ayant leur signification courante. Il est a noter que, comme mentionné par Black [Black1969], la constante A regroupe la contribution de diverses propriétés physiques telles que la section de la ligne métallique sous test, la résistivité électrique du métal, le libre parcours moyen des électrons et la vitesse moyenne...

Par cette extrapolation, il est possible de déterminer si une technologie d'interconnexion est fiable (cf. définition 1.3, p. 14) et par voie de conséquence si cette dernière requiert une amélioration/optimisation aussi bien d'un point de vue du *design* que d'un point de vue du procédé de fabrication.

Ce modèle empirique permet de déterminer soit le courant d'usage ou le courant maximum pour une durée de vie, une température de fonctionnement et un taux de défaillance donnés. A l'inverse, il est possible de déterminer la température d'usage pour une durée de vie, une température de fonctionnement et un taux de défaillance donnés. Pour obtenir ces grandeurs, un rapport des lois de Black entre conditions cibles et conditions accélérées est employé :

$$\frac{MTTF_{cible}}{MTTF_{acc}} = \left(\frac{J_{acc}}{J_{cible}}\right)^{n} \times \exp\left[\frac{E_{a}}{k_{B}} \times \left(\frac{1}{T_{cible}} - \frac{1}{T_{acc}}\right)\right] \times \exp\left(N\sigma\right)$$

(1.3)

où  $MTTF_{cible}$  étant le temps moyen à la défaillance aux conditions normales d'utilisation,  $MTTF_{acc}$  correspondant au temps moyen à la défaillance aux conditions accélérées.  $J_{acc}$  et  $J_{cible}$  sont respectivement la densité de courant  $(A/m^2)$  en conditions accélérées et en conditions normales d'utilisation.  $T_{acc}$  et  $T_{cible}$  sont respectivement les températures en conditions accélérées et en conditions normales d'utilisation. N est une constante qui permet une mise à l'échelle des temps à la défaillance (passer de 1 à 0,1 % de dégradation par exemple).  $\sigma$  est l'écart-type des temps à la défaillance et les autres paramètres conservent les définitions précédemment données.

Pertinence de loi de Black et de la distribution statistique log-normale Comme mentionné à la fin du paragraphe 1.3.2, tous les modèles présentent des limites dans leur applicabilité. La loi de Black et la distribution statistique sous-jacente, la loi log-normale, n'y échappent pas puisqu'elles n'arrivent pas à décrire un certain nombre de résultats expérimentaux.

La distribution statistique usuellement employée est régulièrement remise en cause or le choix de cette distribution est critique puisqu'elle impacte significativement l'extrapolation de la durée de vie aux conditions normales d'utilisation. Cette constatation est d'autant plus criante aux faibles pourcentages de dégradation comme c'est la règle dans l'industrie. Ainsi, selon les cas pratiques, les distributions statistiques de Weibull [Attardo1971, Basavalingappa2017], d'extremum généralisée [Loupis1995] ou encore « multi-log-normale » (MLN) [Yoh2000] ont pu remplacer la distribution log-normale.

Concernant la loi d'extrapolation, telle que décrite ci-dessus (cf. équation 1.2), il est fait l'hypothèse que [TAN2010b] :

- seuls 2 facteurs d'accélération co-existent pendant un essai d'électromigration : la température et la densité de courant,

- le terme pré-exponentiel est indépendant de la température,

- il n'y a pas d'interaction entre température et densité de courant ou tout autre facteur d'accélération,

- l'énergie d'activation effective est indépendante de la densité de courant ou tout autre facteur d'accélération.

Plusieurs études ont montrées que ces hypothèses n'étaient pas toujours valides et que l'un des biais de ce modèle était, a minima, la non prise en compte de l'effet des contraintes thermomécaniques. En effet, les essais accélérés étant effectués à « hautes températures », les lignes de métal se retrouvent dans un état faiblement contraint d'un point de vue thermo-mécanique, le système étant proche de la température où la contrainte thermo-mécanique est nulle. A contrario, à basse température d'accélération, la contrainte thermo-mécanique est beaucoup plus importante devenant ainsi un facteur d'accélération de la dégradation additionnelle [TAN2010b]. Ainsi, d'un point de vue de l'extrapolation des durées de vie aux conditions normales d'utilisation, en partant de résultats obtenus à « hautes températures », on sous-estime l'accélération thermo-mécanique alors qu'en partant de résultats obtenus à « basses températures », on surestime leur contribution.

Outre cette remarque sur les hypothèses sous-jacentes de la loi de Black, notons également des tentatives régulières pour la reformuler. Un premier raffinement a été de la généraliser c'està-dire de supposer que le facteur de dépendance à la densité de courant n'avait pas de valeur fixe [Blair1971]. Un second raffinement a été apporté par Llyod [Lloyd2007]. Il a ainsi pris le parti de considérer 2 phases dans la dégradation, une étape de nucléation de la cavité et une phase de croissance de cette dernière. Bien que pertinent, ce modèle ajoute de la complexité dans la détermination expérimentale des paramètres associés à ce modèle.

Ces faits sont connus de longue date, mais la loi log-normale et l'équation généralisée de Black restent largement employées de par leur facilité d'utilisation et de mise en œuvre!

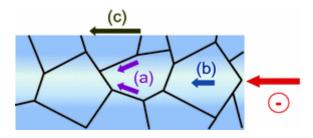

Rôle de l'énergie d'activation, E<sub>a</sub> L'énergie d'activation représente la barrière énergétique contre le procédé de diffusion atomique résultant de l'électromigration. Du fait de la dépendance exponentielle du temps à la défaillance à l'énergie d'activation, une valeur élevée de cette dernière est fortement recherchée. Il a été montré que la valeur de cette énergie est relative aux chemins de diffusion mis en œuvre (cf. tableau 1.1 et figure 1.14). Il est à noter que cette grandeur est une grandeur effective ce qui signifie que sa valeur reflète l'action majoritaire d'un chemin de diffusion même si tous les chemins sont actifs simultanément.

FIGURE 1.14 – Illustration des différents chemins de diffusion dans le matériau métallique d'une interconnexion électrique : (a) joint de grain, (b) diffusion de volume et (c) diffusion de surface. Source : [Lienig2013].

| TABLE 1.1 – Energies d'activation typiques  | pour les divers | chemins de | diffusion | dans | l'alumi- |

|---------------------------------------------|-----------------|------------|-----------|------|----------|

| nium, l'aluminium dopé cuivre et le cuivre. |                 |            |           |      |          |

| Chemin de diffusion | Matériau - Energie d'activation (eV) |             |                 |

|---------------------|--------------------------------------|-------------|-----------------|

|                     | Al                                   | AlCu        | Cu              |

| Massif              | 1,2-1,4                              | 1,2         | 2,2             |

| Joints de grains    | 0,6-0,7                              | 0,7         | 0,88-0,95       |

| Surface/interface   | 0,8                                  | 0,9-1,0     | 0,8-0,9         |

| Référence           | [Lloyd1999]                          | [Lloyd1999] | [Hau-Riege2004] |

Rôle de l'exposant de la dépendance à la densité de courant, n Il a été établi par des études sur les interconnexions à base d'aluminium que la défaillance limitée par la croissance de cavité est représentée par un exposant de densité de courant de 1, tandis que la défaillance limitée par la nucléation de la cavité est représentée par un exposant de 2. Ces concepts sont également valables pour des interconnexions à base de cuivre où des corrélations ont été établies entre les valeurs de n et des analyses de défaillances [Hau-Riege2004].

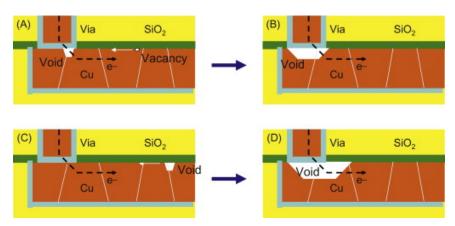

Autrement dit, une défaillance résultant d'une cavité apparaissant directement sous un via peut être limitée par son temps de nucléation (cf. figure 1.15-A-B), alors que celle résultant d'une cavité apparaissant juste en aval de ce via mais ne déconnectant pas électriquement immédiatement ce via peut être limitée par le temps de croissance de cette cavité (cf. figure 1.15-C-D).

FIGURE 1.15 – (A)-(B) Illustration d'une défaillance par électromigration résultant d'une cavité limitée par son temps de nucléation, et (C)-(D) celle résultant d'une cavité limitée par son temps de croissance. Source : [Gambino2012].

L'impact de n sur l'extrapolation de la durée de vie dépend des amplitudes relatives des densités de courant des essais accélérés et aux conditions normales d'utilisation  $(J_{cible}/J_{acc})$ , comme on le voit en reprenant l'équation 1.3  $(MTTF_{cible}/MTTF_{acc})$ . On peut cependant affirmer qu'une valeur plus élevée de n augmente la sensibilité de la densité de courant sur le temps de défaillance extrapolé résultant.

**Rôle du paramètre N** N spécifie le pourcentage de défaillance auquel la fiabilité des interconnexions doit être garantie pour une condition d'utilisation donnée. La valeur de ce paramètre est obtenue en se rapportant au cahier des charges du (futur) « produit ». Une valeur de N plus élevée correspond à un pourcentage de défaillance inférieur, et donc à un critère de défaillance plus strict. A titre d'exemples de relation entre N et une loi normale, une extrapolation à «  $2,326 \times \sigma$  » (par identification avec l'équation 1.3, N = -2,326) correspond à un pourcentage de défaillance

cumulée de 1 %, tandis qu'une extrapolation à «  $-3.09 \times \sigma$  » (ou N=-3.09) correspond à un pourcentage cumulé de défaillance de 0.1 %.

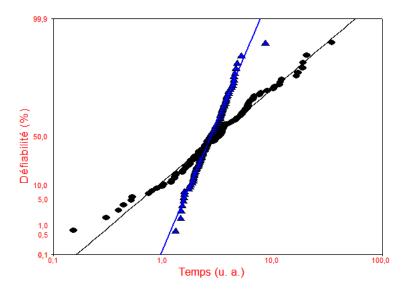

Rôle du paramètre  $\sigma$  Ce paramètre correspond à la pente inverse d'une distribution lognormale et décrit l'étalement ou la dispersion des temps de défaillance. Pour cette raison, il est communément appelé « paramètre de forme ».  $\sigma$  joue un rôle important sur l'extrapolation où, comme on le voit dans l'équation 1.3, une valeur plus élevé de  $\sigma$  conduit à des temps de défaillance extrapolés exponentiellement inférieurs. Cette relation peut être vue graphiquement sur la figure 1.16, qui représente deux distributions avec des temps moyens à la défaillance similaires, mais 2 valeurs du paramètre de forme, où  $\sigma_2 > \sigma_1$ , respectivement courbe avec cercles noirs et courbe avec triangles bleus. L'effet indésirable d'une valeur élevée de ce paramètre devient plus prononcé à des pourcentages de défaillance inférieurs ou à un N plus élevé.

FIGURE 1.16 – Illustration de l'influence du paramètre de forme  $\sigma$  d'une loi log-normale sur la distribution de 100 temps à la défaillance présentant le même temps moyen/médian à la défaillance. La courbe à cercles noirs ( $\sigma = 1$ ) présente un paramètre de forme supérieur à celui de la courbe à triangles bleus ( $\sigma = 0,3$ ).

De nombreux aspects plus ou moins importants n'ont pas été abordés car rappelons-le, l'objectif de ce chapitre n'est pas d'être exhaustif mais d'apporter un minimum d'information pour la compréhension des parties à venir. D'un point de vue électromigration, nous aurions pu aborder le rôle de la microstructure et du métal et de ses alliages, les effets de ligne courte, de réservoir, la non-unicité de la loi log-normale... Pour le lecteur désireux d'approfondir ces connaissances sur ce phénomène de dégradation, nous lui recommandons de se tourner vers les ouvrages ou publications suivantes : [Black1967, Hau-Riege2004, Blech1976, Vairagar2005, Dreyer1993, Hu2007, Arnaud2011, Arnaud2013].

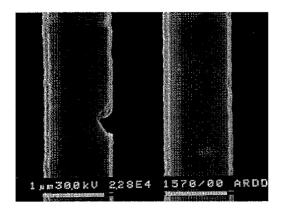

#### Migration sous contrainte

La migration sous contrainte ou *stress migration/stress-induced voiding* (SM/SiV) est un mécanisme de défaillance qui se produit souvent dans la métallisation des circuits intégrés (aluminium, cuivre). Des cavités se forment à la suite de la migration de lacunes provoquée par le gradient de contrainte hydrostatique. Une grande quantité de cavités peut conduire à un circuit électrique ouvert ou à une augmentation de résistance électrique inacceptable qui entravera alors les performances du C.I. (cf. figures 1.17 et 1.18).

Citons à titre d'exemple le cas de la fabrication des interconnexions en cuivre dites « double damascène ». Ce procédé de fabrication laisse le cuivre avec une contrainte de traction importante en raison d'une inadéquation des coefficients de dilatation thermique des matériaux impliqués. La contrainte thermomécanique peut se relâcher avec le temps grâce à la diffusion de lacunes conduisant à la formation de cavités et, finalement, à des défaillances de type circuit ouvert.

FIGURE 1.17 – Exemple de défaut produit par migration sous contrainte dans une ligne d'AlCu. Source : [Kordic1995].

FIGURE 1.18 – Cavité induite par migration sous contrainte dans une structure Van der Pauw réalisé par procédé double-damascène (interconnexion cuivre) après un recuit de 100 h à 150 °C. Source : [Zhang2006].

La loi d'accélération usuellement employée par la communauté pour ce mécanisme de dégradation est donnée ci-après [JED2017] :

$$MTTF = A \times (T_0 - T)^{-n} \exp\left(\frac{E_a}{k_B T}\right)$$

(1.4)

où  $T_0$  (K), température à laquelle la structure est dans un état de contrainte mécanique nul,  $E_a$  (eV), l'énergie d'activation effective, A et n sont des constantes et  $k_B$  et T ont les significations usuelles.

#### Claquage diélectrique dépendant du temps

Le claquage diélectrique dépendant du temps plus connu sous l'acronyme anglo-saxon TDDB (*Time-Dependant Dielectric Breakdown*) est un mécanisme de défaillance typique des oxydes de grille des transistors MOS mais également des oxydes présents entre les niveaux métalliques (*Inter Layer Dielectric*, ILD) ou entre les lignes métalliques (*Inter Metal Dielectric*, IMD) du fait de la réduction des épaisseurs des couches diélectriques et/ou de leur largeur. Cette défaillance a pour

origine le passage d'un courant au travers de l'oxyde susceptible de le dégrader progressivement au point d'aboutir à une rupture localisée.

L'oxyde se détériore à la suite d'une application de longue durée d'un champ électrique relativement faible (comme par opposition à une panne immédiate, provoquée par un fort champ électrique).

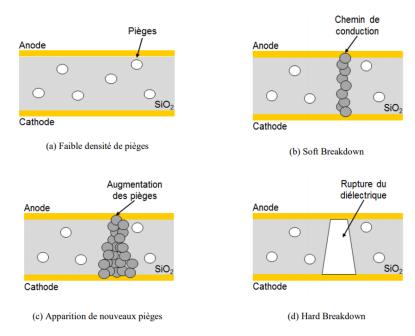

Schématiquement la dégradation induite par le TDDB commence quand des pièges se forment aux bornes de l'oxyde. Cette formation de pièges dépend fortement des conditions de polarisation mais aussi des conditions de fabrication des échantillons. Au début, la densité des pièges est relativement faible et aucun chemin de conduction n'existe (cf. figure 1.19-a). Ensuite, lorsque cette génération de pièges augmente, les pièges produits commencent à se chevaucher formant un chemin de conduction entre l'anode et la cathode, ainsi la dégradation du diélectrique commence. Ce type de dégradation est appelé *Soft Breakdown* (SBD) (cf. figure 1.19-b). Cette dégradation est réversible. Une fois le chemin de conduction formé, de nouveaux pièges sont créés par dégradations thermiques comme le montre la figure 1.19-c. Au final, la conductance augmente de façon brutale, aboutissant à une rupture localisée de l'oxyde, ce type de défaillance est appelé *Hard Breakdown* (HBD) (cf. figure 1.19-d). Au contraire du SBD, le HBD constitue une dégradation catastrophique c'est-à-dire définitive et donc non réversible.

FIGURE 1.19 – Étapes de l'apparition des dégradations au niveau du diélectrique sous contraintes TDDB. Source : [Rousseau2016].

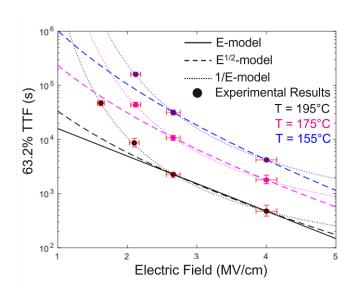

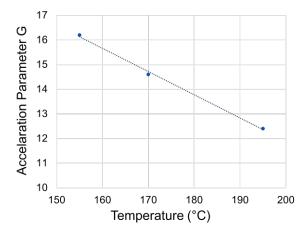

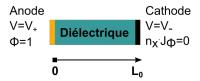

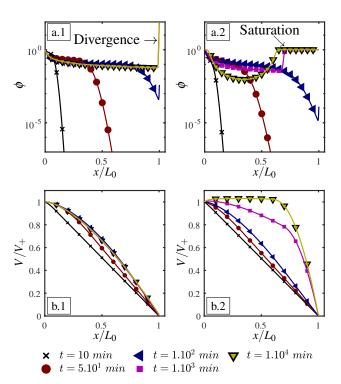

Dans la littérature, 4 mécanismes sont envisagés afin d'expliquer la dégradation du diélectrique et en utilisant ces différents mécanismes, différents modèles de durée de vie ont été proposés même si de manière générique le temps moyen à la défaillance est proportionnel à E<sup>n</sup>, E étant le champ électrique appliqué au diélectrique. Les modèles les plus couramment cités dans la littérature sont les suivants [Chery2014]:

- modèle en E

- modèle en  $\sqrt{E}$

- modèle en loi de puissance

- modèle en 1/E

- modèle de « l'électron chanceux » de J. R. Lloyd

#### **Contraintes résiduelles**

La contrainte mécanique dans les circuits intégrés n'est pas considérée comme un défaut en soi, car elle est une conséquence intrinsèque du procédé de fabrication par la mise en contact de matériaux divers et variés. Néanmoins, la contrainte mécanique a une influence importante sur la génération ou l'aggravation de nombreux défauts tels que les extrusions (hillocks), les fissurations, les contraintes internes, l'électromigration, la migration sous contrainte, la corrosion...

Nous pouvons classer en 2 catégories les contraintes mécaniques :

- 1. Contraintes résiduelles intrinsèques : elles proviennent principalement de la fabrication des circuits intégrés. Exemples : raccord de mailles entre 2 matériaux cristallins, implantation ionique...

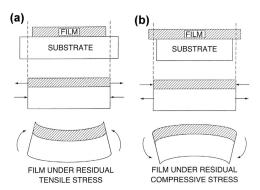

- 2. Contraintes résiduelles extrinsèques ou contraintes thermomécaniques. Elles ont pour origine la différence de coefficient de dilatation thermique (C.D.T. ou en anglais Coefficient of Thermal Expansion, C.T.E.) entre les matériaux en jeu quand ces derniers subissent une variation de température (cf. figure 1.20). Cette dernière pouvant provenir de l'environnement (téléphone satellite utilisé aussi bien dans le Sahara qu'en Antarctique) ou du fonctionnement du composant lui-même (effet Joule).

Ces contraintes résiduelles sont à l'origine des problèmes de fiabilité qui sont regroupés sous l'appellation interaction puce-boîtier ou *Chip-Package Interaction* (C.P.I.) en anglais. Exemples : fissuration du BEoL (cf. figure 1.21) ou « Cu pumping » dans les TSV (cf. figure 1.22)...

FIGURE 1.20 – Illustration du développement d'une contrainte mécanique résiduelle de tension (a) ou de compression (b) dans un film fin selon que le coefficient de dilatation thermique du film  $(\alpha_f)$  est plus ou moins important que celui du substrat  $(\alpha_s)$ . Source : [Ohring1998a].

#### Corrosion

Succinctement, la corrosion est une altération d'un matériau par réaction avec un oxydant. La réaction est accélérée par l'application d'un champ électrique externe car il s'agit d'une réaction électrochimique. Les ions impliqués dans la réaction sont dans ce cas attirés par le champ électrique et migrent d'une région anodique vers une région cathodique. La présence de certains contaminants comme le chlore, ou le fluor accélèrent le phénomène.

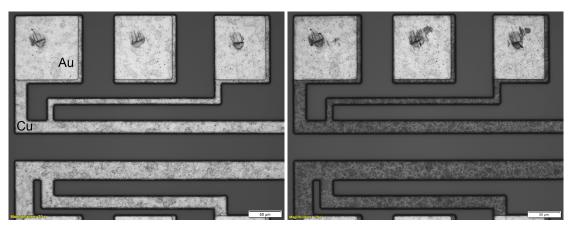

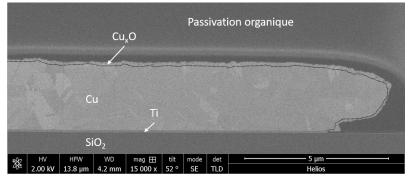

La figure 1.23 présente la corrosion de lignes de redistribution en cuivre suite à un essai de stockage en température (125 °C, 1000 h) malgré une couche organique de passivation. Le noircissement du cuivre est flagrant et est associé à la formation d'un oxyde de cuivre et plus particulièrement de l'oxyde cuivreux ou  $Cu_2O$ .

La loi d'accélération, déterminée empiriquement, couramment employée pour ce mécanisme

FIGURE 1.21 – Fissure traversant le BEoL. Cette défaillance est associée aux contraintes thermomécaniques générées par les billes de brasure qui se répercutent sur les niveaux métalliques sous-jacents. La faible tenue mécanique des oxydes utilisés dans les C.I. avancés (ELK dans le cas présent) peut aboutir à ce type de défaillance. Source : [AMM2017].

FIGURE 1.22 – Gonflement du cuivre du TSV ou Cu pumping. Micrographie montrant la partie supérieure d'un TSV où le cuivre a « gonflé » contraignant le BEoL présent au-dessus. Source : [Radojcic2017].

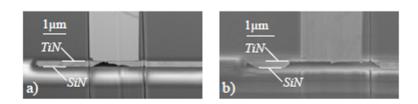

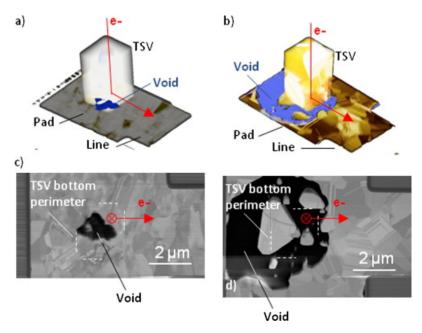

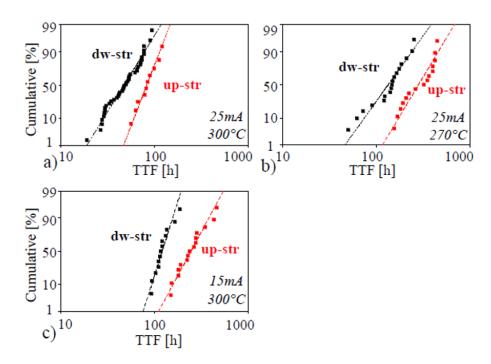

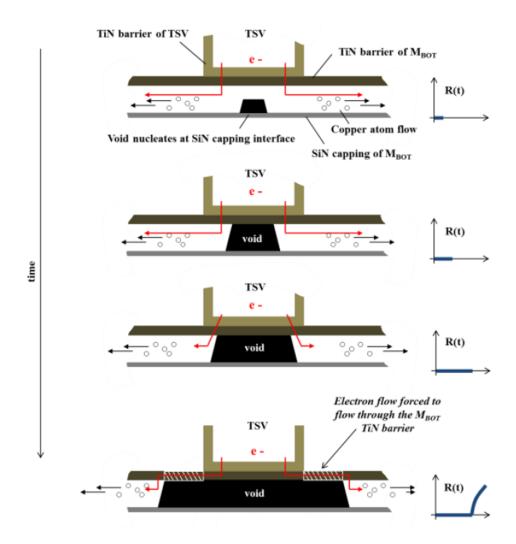

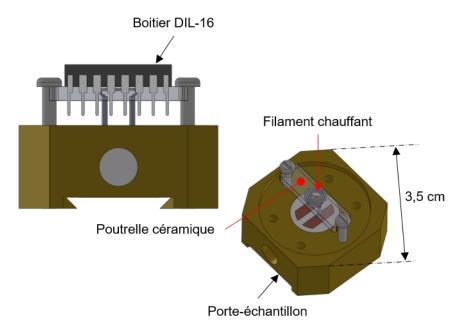

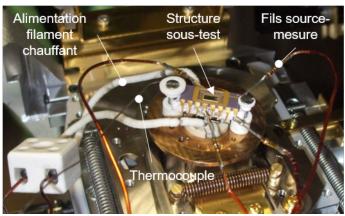

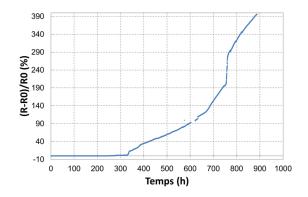

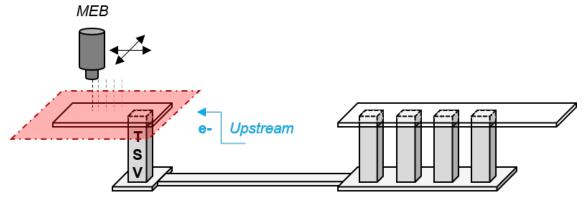

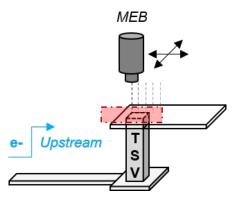

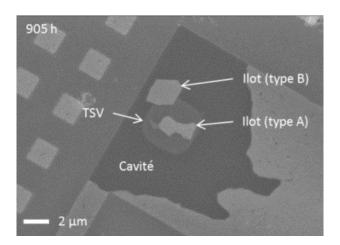

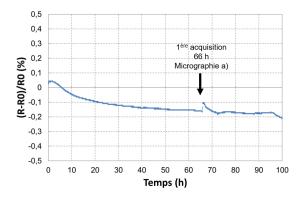

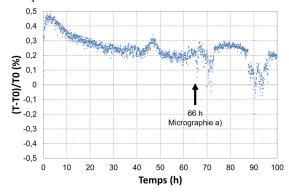

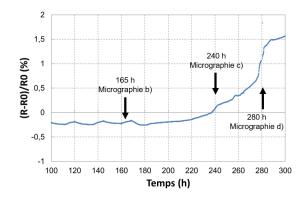

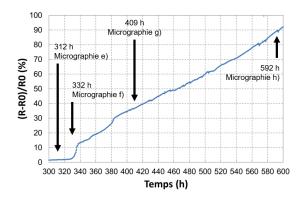

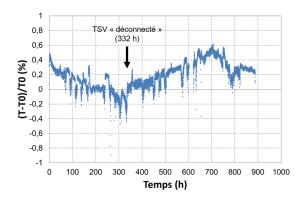

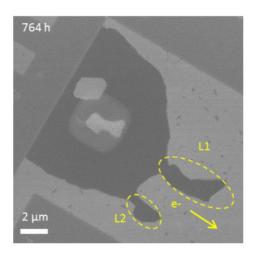

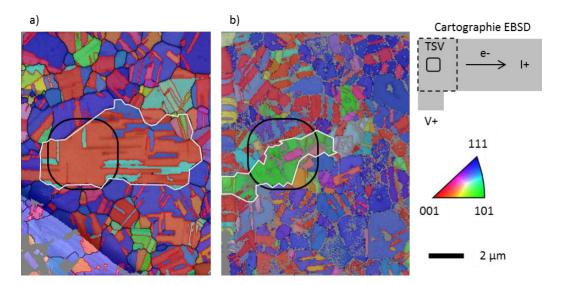

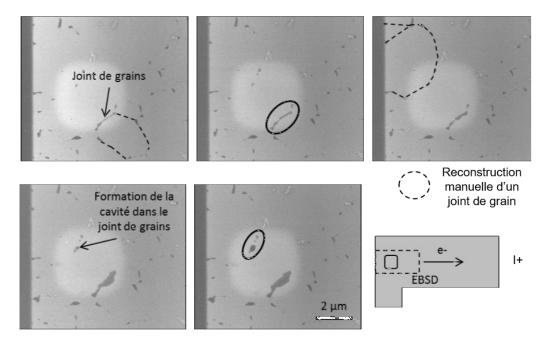

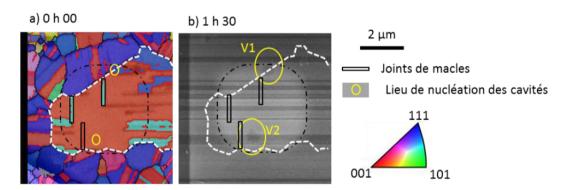

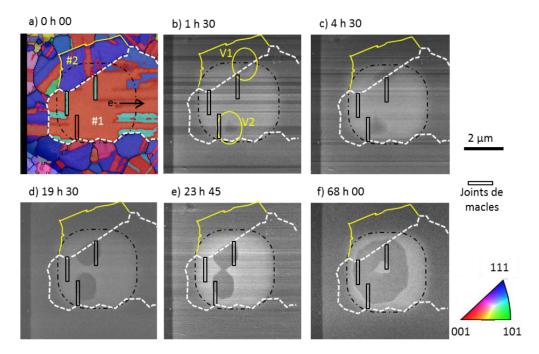

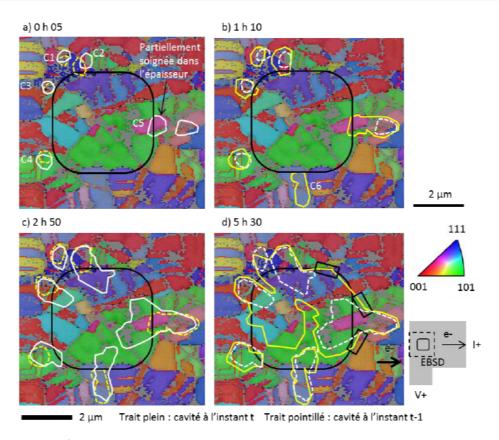

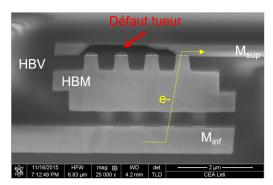

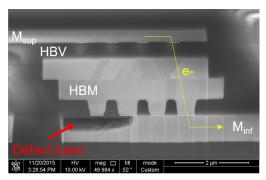

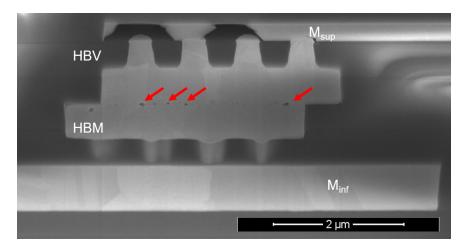

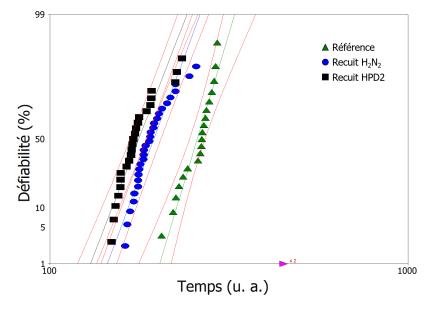

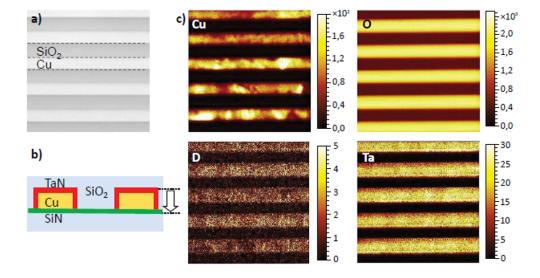

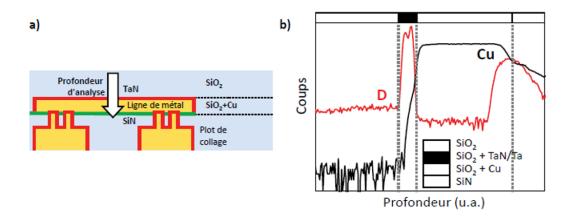

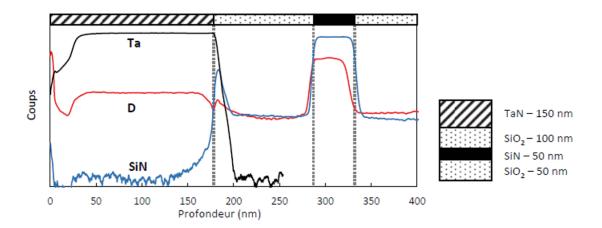

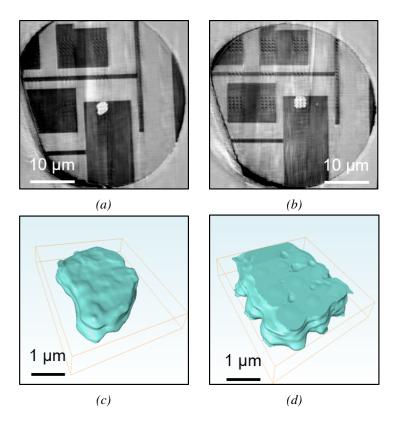

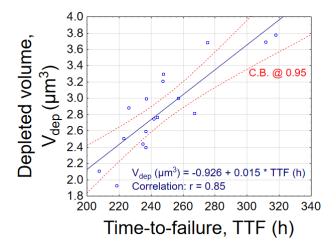

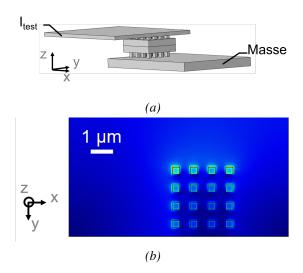

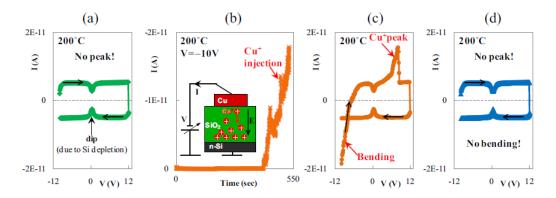

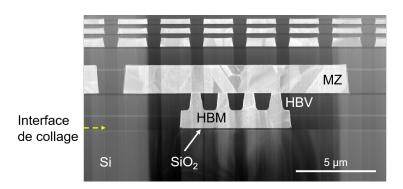

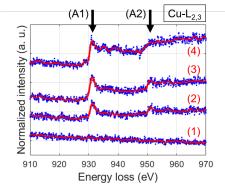

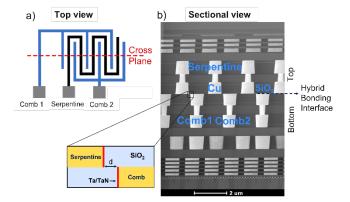

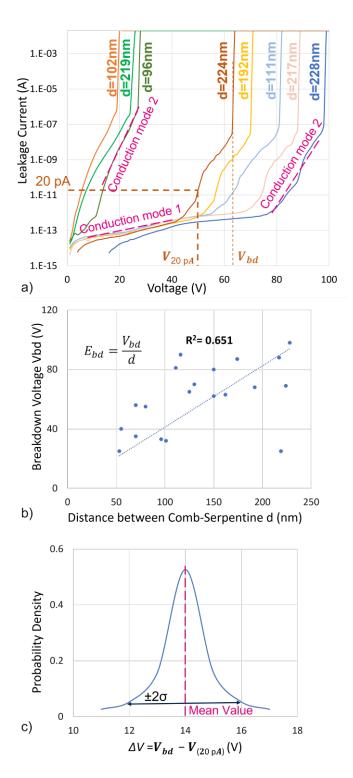

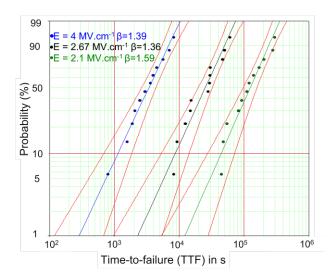

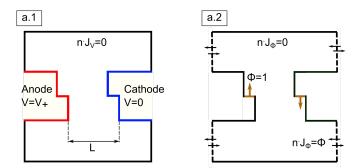

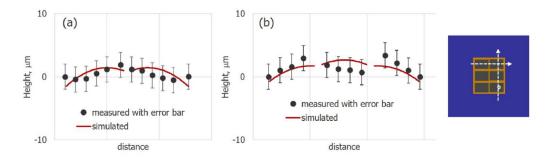

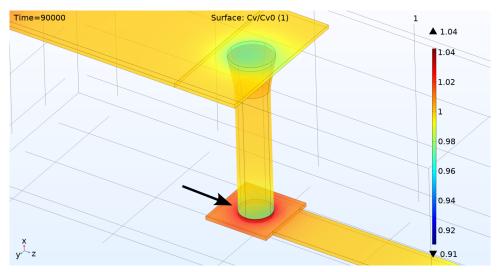

(a) Etat initial. Observation I.R.