## Inductorless multi-mode RF-CMOS low noise amplifier dedicated to ultra low power applications

Thierry Taris, Jennifer Desevedavy, Frederic Hameau, Patrick Audebert,

Dominique Morche

### ► To cite this version:

Thierry Taris, Jennifer Desevedavy, Frederic Hameau, Patrick Audebert, Dominique Morche. Inductorless multi-mode RF-CMOS low noise amplifier dedicated to ultra low power applications. IEEE Access, 2021, 9, pp.83431-83440. 10.1109/access.2021.3085990. cea-04918320

### HAL Id: cea-04918320 https://cea.hal.science/cea-04918320v1

Submitted on 29 Jan 2025  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Received May 17, 2021, accepted May 26, 2021, date of publication June 3, 2021, date of current version June 16, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3085990

# Inductorless Multi-Mode RF-CMOS Low Noise Amplifier Dedicated to Ultra Low Power Applications

THIERRY TARIS<sup>1</sup>, (Senior Member, IEEE), JENNIFER DESEVEDAVY<sup>2,3</sup>, (Member, IEEE), FRÉDÉRIC HAMEAU<sup>3</sup>, (Member, IEEE), PATRICK AUDEBERT<sup>3</sup>, (Member, IEEE), AND DOMINIQUE MORCHE<sup>3</sup>, (Senior Member, IEEE)

<sup>1</sup>IMS Laboratory, University of Bordeaux, 33405 Talence, France <sup>2</sup>Orange, 69003 Lyon, France <sup>3</sup>CEA-Leti, 38054 Grenoble, France

Corresponding author: Thierry Taris (thierry.taris@ims-bordeaux.fr)

**ABSTRACT** This work presents and analyses the design of a multi-mode Low Noise Amplifier (LNA) dedicated to 2.4 GHz Wireless Sensor Network (WSN) applications. The proposed inductorless LNA, implemented in a 28 nm FDSOI CMOS technology, is based on a common-gate configuration imbedded with a common-source stage to boost the overall transconductance of the circuit. The LNA is specifically designed, and optimized, to address three modes of operation. The reconfiguration is performed through current tuning, combined with switching the back gate of the amplification transistors. The proposed implementation allows the figure of merit (FOM) to be maintained constant in the different modes of operation. In the low power mode, the LNA only consumes 350 uW. It achieves a voltage gain ( $G_v$ ) of 16.8 dB and a noise figure (NF) of 6.6 dB. In the medium performance mode, the gain and the NF are respectively improved to 19.4 dB and 5.4 dB, the power consumption is 0.9 mW. In the high-performance mode, the gain is maximum, 22.9 dB, and the noise figure is minimum, 3.6 dB, for a power consumption of 2 mW. The linearity represented by the input referred third-order intercept point (IIP3) is constant, close to -16 dBm. The reported LNA occupies only 0.0015 mm<sup>2</sup>.

**INDEX TERMS** RF low power, low noise amplifier, inversion coefficient.

#### I. INTRODUCTION

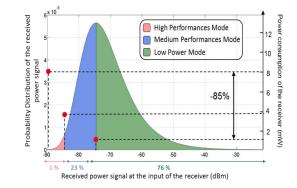

At the edge of the Internet Of Things (IOT) deployment, the implementation of Wireless Sensor Networks (WSN) has to address two challenges: the energy saving and the low-cost development. In a wireless sensor node, 70% of the power consumption is generally dedicated to the radiofrequency (RF) module [1]. More specifically, 60% of the power dedicated to the receiver (Rx) part of an RF module is consumed by the frequency synthesis and the RF amplification, thus compromising the node's lifetime [2]. To address this issue, a channel-aware solution is proposed in [3]. Based on the IEEE802.15.4 standard and a given scenario of WSN deployment, the probability distribution of the received power signal is derived in Fig. 1. The lifetime of a node can be multiplied by a factor of 5 if the receiver front end (RFFE) features three modes of operation, with the specifications

**FIGURE 1.** Probability Distribution of the received power signal at a wireless sensor node [3].

reported in Table 1 [3]. Focusing on the amplification stage, the investigations derive a set of specifications for the Low Noise Amplifier in each mode of operation. This paper aims to implement such multi-mode LNA.

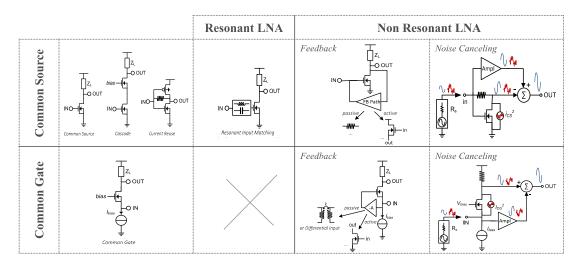

FIGURE 2. LNA architecture basics.

|      | Mode                    | Low<br>Power | Medium<br>Performance | High<br>Performance |  |

|------|-------------------------|--------------|-----------------------|---------------------|--|

|      | P <sub>sens</sub> (dBm) | -75          | -85                   | -90                 |  |

| RFFE | Usage (%)               | 76           | 23                    | 1                   |  |

| R    | P <sub>DC</sub> (mW)    | <1.2         | <4                    | <8                  |  |

|      | S <sub>11</sub> (dB)    | <-10         | <-10                  | <-10                |  |

| P    | NF (dB)                 | 7            | 5                     | 3                   |  |

| LNA  | G <sub>V</sub> (dBv)    | 15           | 20                    | 25                  |  |

|      | IIP3 (dBm)              | -16          | -16                   | -16                 |  |

|      | P <sub>DC</sub> (mW)    | <0.5         | <1                    | <2                  |  |

TABLE 1. Specifications for multi-mode RFFE and LNA dedicated to WSN.

In Ultra Low Power (ULP) applications, such as WSNs, power saving can be achieved by relaxing the performance in terms of data-rate and sensitivity. Interestingly, a wireless node would scarcely (1% of time) have to achieve a high sensitivity (-90dBm), and most of the time (76% of usage) a sensitivity close to -75dBm as illustrated in Fig. 1. This feature is exploited to relieve the NF and linearity specifications of the LNA as reported in Table 1. Up to now, the design of ULP LNA has only focused on reducing the power consumption for a fixed mode, with no specific consideration for reconfiguration nor multi-mode operation. The purpose of this paper is to address this, by firstly investigating a design guide based on the Inversion Coefficient (IC) to work out a design of LNA suited for each mode of operation.

The back gate of the 28nm FD-SOI technology is further exploited to implement the reconfigurability of the circuit. This technique offers an interesting solution for the switching of analog/RF transistors operating in the sub-threshold region. The last section presents measurement results, and a comparison with the state of the art.

#### **II. LNA CONSIDERATIONS**

LNA basics are first briefly discussed in this section. Afterwards, the proposed topology is introduced, along with the analytic derivations of the input impedance, the noise factor and the voltage gain.

#### A. LNA ARCHITECTURE BASICS

Only two topologies of amplification are exploited in the design of LNA: the common-source configuration (CS), including cascode and current reuse arrangements, and the common-gate configuration (CG). The input matching, which contributes to the voltage gain and the noise figure, can be either of the resonant type or the non-resonant type, as illustrated in Fig. 2. Resonant LNAs embed an LC-based network, which not only achieves input matching, but also voltage pre-amplification. This passive pre-amplification contributes to the reduction of the noise figure (NF) and increases the overall voltage gain (G<sub>v</sub>). Presenting a highly capacitive input impedance, the CS configuration is preferred for the implementation of a resonant LNA. Indeed, the gate to source capacitor is absorbed in the synthesis of the input matching network. A classic solution is the use of a cascode topology with inductive degeneration [4]. Resonant LNAs provide (very) good performance in terms of voltage gain and noise figure [5]. However, they are narrowband due to the limited bandwidth of the LC input matching. In terms of integration, the inductors embedded in the input network require a large area of silicon, preventing the development of highly integrated, and low cost, RFFEs.

To perform the input matching, non-resonant LNAs add a (local) feedback path, in the case of CS configuration, or exploit the natural resistive input impedance, in the case of CG configuration. These techniques do not achieve voltage pre-amplification, which limits the NF performance compared to resonant LNAs. As illustrated in Fig. 2, nonresonant LNA architectures can be classified in two categories. The first one embeds a feedback between the output and the input for the CS configuration, between the input and the gate for the CG configuration. The feedback path can be active or passive. It is usually dedicated to improve the current efficiency [15], or to relax the trade-off between the gain-bandwidth product, the noise figure, and the condition for input matching [17]. The second type of architecture exploits the technique of noise canceling. In this approach, the thermal noise of the main amplification stage is cancelled out by an auxiliary path, which performs out-of-phase processing of the input signal, and in-phase processing of the noise, as illustrated in Fig 2. The technique of noise canceling ensures a flat band behavior of the circuit response over a significant bandwidth [6], but does not guarantee noise input matching. Non-resonant LNAs are particularly suited for wideband operation and can be highly integrated.

Considering the relatively relaxed NF specification and the constraint on the development cost of the targeted application, a solution based on an inductorless, non-resonant LNA is preferred. The noise canceling architecture is not suited for low power applications due to its dual path processing and the conditions required for noise cancelation. The proposed LNA exploits a feedback architecture with an emphasis on current efficiency and reconfiguration capability.

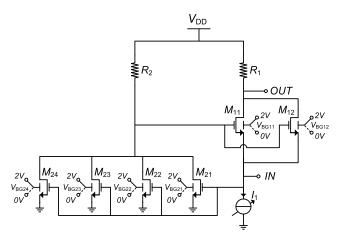

## B. COMMON GATE CONFIGURATION WITH ACTIVE Gm-BOOSTED

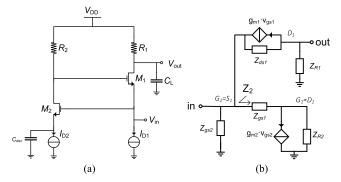

Referring to Table 1, as the linearity (IIP3) is relaxed, and therefore does not require any design effort. However, the voltage gain specification is challenging if we consider the associated  $P_{DC}$ . To overcome this issue, a topology with a high current efficiency is recommended. A simplified schematic of the proposed LNA architecture is presented in Fig. 3(a). The core of the circuit is based on a CG configuration (M<sub>1</sub>, R<sub>1</sub>) whose transconductance is boosted by the voltage gain of the CS stage (M<sub>2</sub>, R<sub>2</sub>). The separate paths of the CS and CG stages are further exploited to adjust the performance of the circuit through bias control. Based on the equivalent schematic proposed in Fig. 3(b), the voltage gain,

FIGURE 3. Active Gm-Boost CG LNA topology (a) equivalent small signal schematic (b).

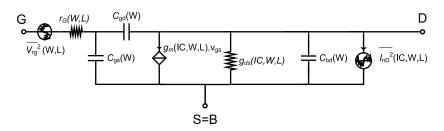

the input impedance and the noise factor are derived in (1), (2) and (3) respectively. For the noise analysis, only the thermal noise contributions are considered. The noise model of the MOS transistor is given in the Appendix.

$$G_{V} = \frac{\left[1 + g_{m1}.Z_{ds1}\frac{(1+g_{m2}.Z_{R2})}{(1+Z_{R2}/Z_{gs1})}\right]}{(1 + \frac{Z_{ds1}}{Z_{R1}})}$$

(1)

$$Z_{in} = \frac{1}{\left[jC_{gs2}\omega + g_{m1}.\frac{(1+g_{m2}.Z_{R2})}{(1+Z_{R2}/Z_{gs1})} + \frac{(1-G_V)}{Z_{ds1}} + \frac{(1+g_{m2}.Z_{R2})}{(Z_{gs1}+Z_{R2})}\right]}$$

(2)

$$\begin{split} F &= 1 + \frac{4}{(1 + g_{m2} |Z_2|)^2 . R_s} \\ & \cdot \left[ \frac{\left[ |Z_2|^2 \left( \frac{1}{R_2} + \gamma_n . g_{m2} + g_{m2}^2 . r_{g2} \right) + r_{g1} + \frac{\gamma_n}{g_{m1}} \right]}{\left[ 1 + g_{m1} |Z_s| \left( 1 + g_{m2} |Z_2| \right) \right]^2} + \frac{1}{R_1} \right] \end{split}$$

With:

$$\begin{split} \frac{1}{Z_{ds1}} &= g_{ds1} + jC_{ds1}\omega \\ \frac{1}{Z_{R2}} &= g_{ds2} + jC_{ds2}\omega + \frac{1}{R_2} + jC_{gd1}\omega \\ \frac{1}{Z_{gs1}} &= j\left(C_{gs1} + C_{gd2}\right)\omega, \\ \frac{1}{Z_2} &= Y_{R2} + Y_{gs1} \\ \frac{1}{Z_{R1}} &= \frac{1}{R_1} + jC_{gd1}\omega + jC_L\omega \end{split}$$

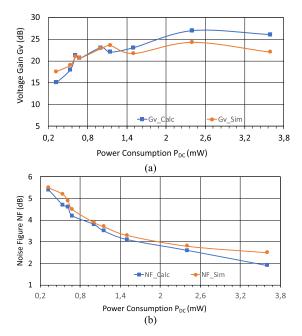

In Fig. 4, the analytic expressions (1), (2) and (3) are compared with Cadence simulations for the design of the 2.4GHz LNA with different power budgets. We first note that the performance is consistent with the expected specifications for each mode. The topology is suited for the targeted application. Furthermore, both the analytical and simulation results exhibit similar responses over an order of magnitude of DC power consumption. The proposed derivations can be further exploited to optimize the design.

#### **III. LNA SYNTHESIS**

To optimize the LNA for different modes of operation, the performance of the circuit is analyzed over a large design space. To address this purpose an algorithmic approach is proposed.

#### A. EKV MODEL AND DESIGN SPACE EXPLORATION

To explore the design space of the Gm-boosted LNA, the EKV model [7], offering a continuous and simple description of the MOS device from the Weak Inversion (WI) to the Strong Inversion (SI) regions, is exploited. In the EKV model, the drain current,  $I_D$ , in saturation mode is defined by the transistor aspect ratio W/L, the Inversion Coefficient (IC) and

FIGURE 4. Comparison of the analytic model and Cadence simulations of the Voltage Gain (Gv) (a) and the Noise Figure (NF) (b) at 2.4GHz in 28nm FDSOI.

the specific current  $I_{spec_{sq}}$  according (4).

$$I_{Dsat} = \frac{W}{L}.I_{spec\_sq}.IC$$

(4)

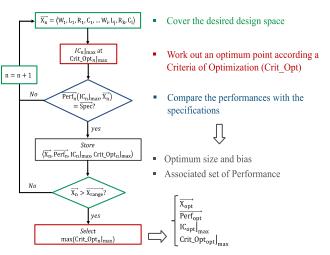

where W and L are, respectively, the gate length and width of the device,  $I_{spec\_sq}$  is a technological parameter, and the IC represents the level of channel inversion. The MOS transistor described with the IC operates in WI when IC<0.1, in the Moderate Inversion (MI) when 0.1 < IC < 10, and in SI when IC>10. The small signal model of a MOS transistor, reported in Appendix [12], is used to exploit the analytic derivations (1), (2) and (3). To explore the design space of the circuit, the algorithm illustrated in Fig. 5 is implemented in MatLab. This algorithm is not specific to the design of LNA, it can be used for any analog/RF circuit described with the IC. It works out a set of dimensions  $(\overrightarrow{X_{opt}})$ , and the associated performance ( $\overrightarrow{Perf_{opt}}$ ), which address a set of specifications ( $\overrightarrow{Spec}$ ) while achieving a maximum amount of optimization criteria (Crit\_Opt).

#### **B. Gm-BOOSTED LNA SYNTHESIS**

The algorithm described in Fig. 5 is used to generate several LNA designs, which address the specifications defined in Tab 1. The algorithm is run for each set of specifications.

The design space is defined as follows:

- IC<sub>i</sub> range is 0.05 to 20 with 10 values per decade

- $R_i$  range is 400 to 1400 Ohm with a step of 100 Ohm

- W<sub>i</sub> range is 10um to 120um with a step of 10um

- Li are limited to 28nm, 45nm and 60nm

- C<sub>L</sub> is fixed to 50fF

FIGURE 5. Algorithm for design space exploration of an analog/RF circuit.

- Crit\_Opt is defined in (5)

$$FOM = \frac{G_V \rfloor_{lin} . BW \rfloor_{GHz}}{P_{DC} \rfloor_{mW} . (F \rfloor_{lin} - 1)}$$

(5)

The FOM (5) is typical of a low power LNA [11]. The linearity, IIP3, is not included, since the targeted performance, -16dBm, is not an issue here. Table 2 reports the dimensions and the associated performance for each configuration. The time required to explore the design space, and to work out the data for each configuration, does not exceed 850 sec (15 min.).

We observe a moderate variation (+15%) in the resistor values, from  $600\Omega$  to  $700\Omega$  for R<sub>1</sub>, and from  $850\Omega$  to  $1000\Omega$ for R<sub>2</sub>. Interestingly the ratio R<sub>2</sub>/ R<sub>1</sub>, close to 1.4, is almost constant over the different design sets. The optimization of the circuit for each mode is more dependent on the width of the transistors (W<sub>M1</sub>, W<sub>M2</sub>), and the associated bias conditions represented by (IC<sub>M1</sub>, IC<sub>M2</sub>). Reconfiguring the LNA performance would focus on adjusting both the drain current and the size of M<sub>1</sub> and M<sub>2</sub>.

#### **IV. IMPLEMENTATION**

Based on the circuit analysis and the first-cut design proposed in section III, the implementation of the LNA is now discussed. More specifically, the strategy of reconfiguration and its consequences on the overall performance are investigated.

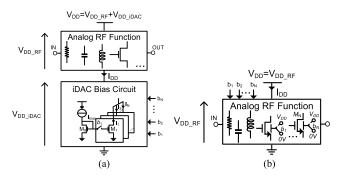

According Table 2, the optimization of the LNA for each mode is mainly supported by adjusting the geometry of  $M_1$  and  $M_2$ , and the associated bias conditions. Hence the implementation of the multi-mode LNA focuses on the tuning of the transistor's width and bias. The reconfiguration of analog/RF circuits is usually steered by current DAC composed of CMOS switches and weighted current mirrors. Stacked with the RF function between the supply rails, Fig. 6(a), the current DAC requires an increase in the nominal supply, and as a consequence, consumes an extra DC power ( $V_{DD \ iDAC}I_{DD}$ ). Interestingly, the FDSOI technology features

TABLE 2. LNA sizing and performance based on algorithm.

|              |                      |       | 1           | 1           |  |  |

|--------------|----------------------|-------|-------------|-------------|--|--|

|              | Mode                 | Low   | Medium      | High        |  |  |

|              | moue                 | Power | Performance | Performance |  |  |

|              | $W_{M1}$ (um)        | 20    | 40          | 45          |  |  |

|              | $L_{M1}$ (nm)        | 28    | 28          | 28          |  |  |

| zes          | IC <sub>M1</sub>     | 0.25  | 0.30        | 0.35        |  |  |

| e Si         | $W_{M2}(um)$         | 30    | 80          | 100         |  |  |

| Device Sizes | L <sub>M2</sub> (nm) | 28    | 28          | 28          |  |  |

| $D_{\rm e}$  | IC <sub>M2</sub>     | 0.4   | 0.3         | 0.4         |  |  |

|              | $R_1(\Omega)$        | 600   | 650         | 700         |  |  |

|              | $R_{2}(\Omega)$      | 850   | 900         | 1000        |  |  |

| ices         | S <sub>11</sub> (dB) | <-10  | <-10        | <-10        |  |  |

| так          | NF (dB)              | 5.8   | 4.5         | 2.8         |  |  |

| Performances | G <sub>V</sub> (dBv) | 15    | 21          | 26.2        |  |  |

| $Pe_{i}$     | P <sub>DC</sub> (uW) | 300   | 850         | 1950        |  |  |

**FIGURE 6.** Principle of circuit reconfiguration with an iDAC (a) back gate switching (b).

an isolated access of transistor back-gates, which can be manipulated under specific bias conditions, further discussed, in order to switch the device on and/or off. This technique does not need to implement any additional circuitry with the RF function, nor any supplemental DC power, as illustrated in Fig. 6(b).

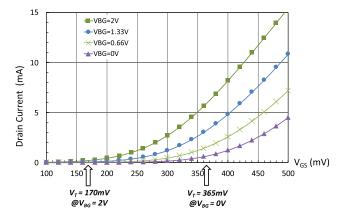

In Fig. 7  $I_D(V_{GS})$  is drawn as a function of the back-gate voltage  $V_{BG}$  of a NMOS transistor, in a 28nm FDSOI technology. Commuting  $V_{BG}$  from 0V to +2V reduces the transistor threshold voltage ( $V_T$ ) from 365mV to 170mV. Hence, a transistor operating in the MI region (0.1<IC<10) with  $V_{GB} = +2V$ , illustrated by square marks in Fig. 7, has its gate to source voltage,  $V_{GS}$ , close to 170mV. If  $V_{BG}$  is grounded (0V), as shown by triangle marks in Fig. 7, the  $V_T$  is shifted to 365mV and the transistor, now operating in the WI region with an IC<0.1, is almost turned off.

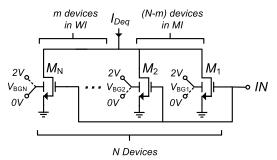

For the 3 designs proposed in Table 2, the transistors operate in the MI region ( $0.25 < IC_{Mi} < 0.4$ ), and can be reconfigured through back-gate control. We first discuss the impact of such a technique on the circuit performance and its implementation. To illustrate this, we consider in Fig. 8, a multi-gate transistor featuring N elementary devices  $M_i$ ,

FIGURE 7. Drain current of a 50 $\mu$ /28nm FDSOI NMOS transistor versus V<sub>GS</sub> as a function of V<sub>BG</sub>.

FIGURE 8. An N-gate common source configuration of a NMOS transistor with a back gate control VBGi.

with the same size  $(W_0, L_0)$ , controlled by the back-gate voltage  $V_{BGi}$ . For the proposed configuration we further assume:

- $M_i$  operates in the MI region at  $IC_{MI}$  if  $V_{BGi} = 2V$ , "on-state"

- $M_i$  operates in the WI region at  $IC_{WI}$  if  $V_{BGi} = 0V$ , "off-state"

- $IC_{MI} \gg IC_{WI}$  -i.e. typ.  $IC_{MI} > 0.2$  and  $IC_{WI} < 0.01$ -m transistors operate in the WI region with 0 < m < (N-1), and at least one transistor operates in the MI region

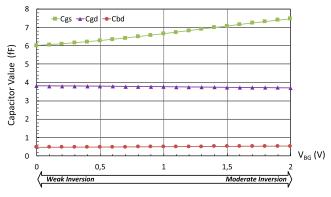

For a given configuration of the back gate control, the small signal model (see Appendix) of the equivalent transistor Mea (Fig.8) depends on the number of devices operating respectively in the MI region and the WI region. The model parameters are derived in Table 3, expressions (6) to (12) accounting for m, the number of transistors operating in the WI region. Since  $IC_{MI} \gg IC_{WI}$ , we can assume that the equivalent inversion coefficient ICeq (6), drain current  $I_{Deq}$  (7), transconductance  $g_{meq}$  (8), and output conductance  $g_{dseq}$  (9), are determined by the number of transistor operating in the MI region (N-m). The parasitic capacitors are defined by the geometry of the device, and are weakly dependent on bias conditions. Indeed, we observe in Fig. 9 a variation of less than 16% of  $C_{gs}$ , 2% of  $C_{gd}$  and 10% of  $C_{bd}$  when the back gate (VBG) of an NMOS transistor ranges from 0V (WI region) to 2V (WI region). The values of Cgseq, Cgdeq and C<sub>dseq</sub> are determined by the total number of parallel devices N.

**FIGURE 9.** Simulated Parasitic Capacitors, Cgs, Cgd, Cbd versus  $V_{BG}$  for an NMOS transistor biased at VGS=300mV and VDS=500mV (W=20 $\mu$ m/L=28nm).

**TABLE 3.** Parameters and metrics of the equivalent N-gate transistor with m devices operating in weak inversion region.

| Param                 | Theoretical expression                                                 | Approx.                                                                       | Eq.  |

|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| IC <sub>eq</sub>      | $= (N - m). IC_{MI} + m. IC_{WI}$                                      | $\approx$ (N – m). IC <sub>MI</sub>                                           | (6)  |

| I <sub>Deq</sub>      | $= [(N - m). IC_{MI} + m. IC_{WI}]. I_{specD}. \frac{W_0}{L_0}$        | $\approx (N - m). IC_{MI}$ $. I_{spec\Box} . \frac{W_0}{L_0}$                 | (7)  |

| $g_{meq}$             | $= (N - m).g_m(IC_{MI}) + m.g_m(IC_{WI})$                              | $\approx$ (N – m).g <sub>m</sub> (IC <sub>MI</sub> )                          | (8)  |

| gdseq                 | $= g_{ds11}(IC_{11}) + g_{ds12}(IC_{12})$                              | $\approx g_{ds11}(IC_{11})$                                                   | (9)  |

| C <sub>gseq</sub>     | $= (N - m).C_{gsMI}(W_0)$<br>+ m.C <sub>gsWI</sub> (W <sub>0</sub> )   | $\approx \mathrm{NC}_{\mathrm{gsMI}}(\mathrm{W}_{0})$                         | (10) |

| C <sub>dseq</sub>     | $= (N - m). C_{dsMI}(W_0)$<br>+ m. C <sub>dsWI</sub> (W <sub>0</sub> ) | $\approx \mathrm{NC}_{\mathrm{dsMI}}(\mathrm{W}_{0})$                         | (11) |

| C <sub>dgeq</sub>     | $= (N - m). C_{dgMI}(W_0)$<br>+ m. C_{dgWI}(W_0)                       | $\approx \mathrm{NC}_{\mathrm{dgMI}}(\mathrm{W}_{0})$                         | (12) |

| Current<br>Efficiency | <u>gmeq</u><br>I <sub>Deq</sub>                                        | $\frac{g_m(IC_{MI})}{IC_{MI}.I_{spec\Box}.\frac{W_0}{L_0}}$                   | (13) |

| Transit<br>Frequency  | $f_{Teq} = \frac{g_{meq}}{2\pi C_{gseq}}$                              | $\frac{\left(1 - \frac{m}{N}\right).g_{_{m}}(IC_{MI})}{2\pi.C_{gsMI}(W_{0})}$ | (14) |

Two metrics are considered to illustrate the impact of the multi-gate configuration with back bias control on the performance of the equivalent transistor: the current efficiency  $(g_m/I_D)$  and the transit frequency  $(f_T)$ .

As long as  $IC_{MI} \gg IC_{WI}$ , the equivalent current efficiency (13) is not affected by the multi-gate configuration. However the transit frequency (14) depends on the ratio between the number of devices operating in the WI (N-m) and MI regions (m):

- if  $(\frac{m}{N}) \ll 1$ ,  $f_{Teq}$  is the same as a single transistor, featuring an aspect ratio  $\left(\frac{W_0}{L_0}\right)$  and a drain current  $I_{Deq}$ .

- if the number of devices m operating in the WI region is not negligible compared to the number of devices

FIGURE 10. Architecture of the proposed multi-mode LNA.

operating in the WI region (N-m),  $f_{Teq}$  is reduced by a factor  $(1 - \frac{m}{N})$ .

The multi-gate configuration is equivalent to a scalable transistor, which steers the DC current and the transconductance. However, the frequency performance  $(f_{Teq})$  of the equivalent transistor is more affected than a standalone equivalent device if the number of devices operating in the WI region (off-state mode), is not negligible compared to the number of devices operating in the MI region (on-state mode). This frequency degradation must be considered for the design of RF circuits.

The architecture of the multi-mode LNA implemented in a 28nm FDSOI CMOS technology is reported in Fig. 10. As discussed in section III, the tuning of the resistor value has a moderate impact on the optimization of the reconfiguration.  $R_1$  and  $R_2$  are respectively fixed to 850 $\Omega$  and 1250 $\Omega$  which respects the ratio condition 1.4. The tuning of the current and the IC is performed by

- the current source  $(I_1)$  and by resizing  $M_1$  throughout  $V_{BG1i}$  in the CG branch.

- the supply voltage  $\left(V_{DD}\right)$  and resizing  $M_2$  throughout  $V_{BG2i}$  in the CS branch.

The current source in the CS branch is removed in order to keep the supply voltage below 1.2V in the high-performance mode. To reduce the mismatch, each branch is implemented with a replica of a unit transistor:  $M_{2i}$  geometry is (30um/28nm), and  $M_{1i}$  geometry is (20um/28nm). The equivalent device sizes and bias conditions for each mode, based on post-layout simulations and accounting for the impact of the multi-gate configuration on frequency performance, are reported in Table 4.

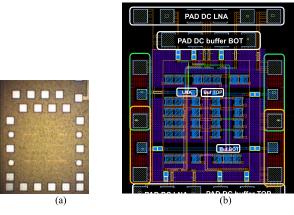

#### **V. MEASUREMENT RESULTS**

A chip micrograph and a layout snapshot are presented in Fig. 11(a) and (b) respectively. The silicon footprint of the multi-mode LNA is only  $0.0015 \text{ mm}^2$ . The implemented circuit includes a buffer based on a source follower. The contribution of the buffer is de-embedded from the reported results.

|                    | Mode                 | Low<br>Power | Medium<br>Performance | High<br>Performance |  |

|--------------------|----------------------|--------------|-----------------------|---------------------|--|

|                    | W <sub>M1</sub> (um) | 20           | 40                    | 40                  |  |

|                    | IC <sub>M1</sub>     | 0.27         | 0.27                  | 0.27                |  |

| lias               | W <sub>M2</sub> (um) | 30           | 60                    | 120                 |  |

| ξP                 | IC <sub>M2</sub>     | 0.32         | 0.32                  | 0.32                |  |

| ze c               | $R_1(\Omega)$        | 850          | 850                   | 850                 |  |

| si:                | $R_2(\Omega)$        | 1250         | 1250                  | 1250                |  |

| ice                | $I_1$ (uA)           | 180          | 360                   | 360                 |  |

| Device Size & Bias | $I_2(uA)$            | 320          | 640                   | 1280                |  |

|                    | V <sub>DD</sub> (V)  | 0.6          | 0.9                   | 1.2                 |  |

TABLE 4. Final LNA sizing based on post-layout simulations.

FIGURE 11. Chip micrograph (a) Layout snapshot (b).

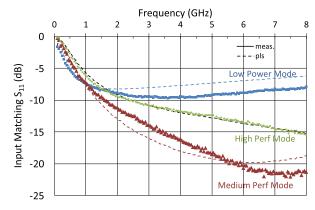

FIGURE 12. Measured and PLS input return loss S<sub>11</sub> for the 3 modes of operation.

The measurement results and the post layout simulations (PLS) of the LNA are presented for the 3 modes of operation. According to (2), the input impedance of the circuit is dominated by the transconductance  $g_{m1}$  of the CG stage (M<sub>1</sub>, R<sub>1</sub>). The equivalent transconductance  $g_{m1eq}$  is changed when switching modes, as is the input matching. The input return loss S<sub>11</sub>, Fig. 12, is kept below -9dB from 1.8GHz to 8GHz in medium and high performance modes, and from 2GHz to 5GHz in low power mode. We observe a very close form between the measurement and PLS results.

In the proposed Gm-boosted topology, most of the gain is achieved through the CS branch  $(M_2, R_2)$ . The voltage gain,

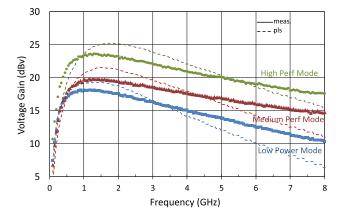

FIGURE 13. Measured and PLS Voltage Gain for the 3 modes of operation.

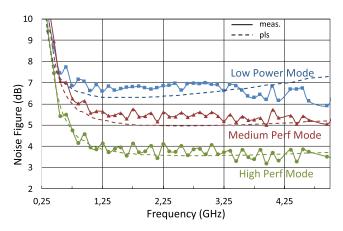

FIGURE 14. Measured and PLS Noise Figure for the 3 modes of operation.

Fig. 13, is obtained from  $S_{21}$  data. In high performance mode, it is 23.6dB at 1.3GHz, in medium power mode it is 19.8dB at 1.6GHz, and in low power mode it is 18.1dB at 1.4GHz. We can observe the impact of the multi-gate configuration on the frequency performance of the circuit. The -3dB cut-off frequencies are respectively 4.35GHz, 5.2GHz and 4GHz. For the 3 modes of operation, the measured peak of Gv almost occurs at the same frequency, but it is 1 to 2 dB lower with respect to the PLS. The measured forms remain consistent with the PLS.

The noise figure (NF), Fig. 14, exhibits a flat response which is typical for inductorless LNAs. The measured performance is in good agreement with PLS. In this topology, the NF is limited by the transconductance of the CG branch, which also adjusts the input matching as previously discussed. The NF is 3.3dB at 3.45GHz in high performance mode, 4.7dB at 4.25GHz in medium performance mode and 5.9dB at 3.95GHz in low power mode. In any mode, the NF ripple does not exceed +0.5dB from 1GHz to 3.25GHz, and is less than 0.8dB from 1GHz to 4.85GHz. The increase of NF for frequencies below 500MHz is due to the gain roll-off, induced by the coupling capacitor at the input of the circuit.

As discussed in the introduction, this LNA is originally dedicated to 2.4GHz WSN applications, and is expected to address the specifications reported in Table 1. In low power

| -                       |            | r          |            |     |     |       |       | -     | -    |      |       |       | -    |       |       |        |

|-------------------------|------------|------------|------------|-----|-----|-------|-------|-------|------|------|-------|-------|------|-------|-------|--------|

| Ref                     | LP<br>Mode | MP<br>Mode | HP<br>Mode | [8] | [9] | [10]  | [11]  | [12]  | [13] | [14] | [12]  | [15]  | [16] | [17]  | [12]  | [18]   |

| Gain<br>(dBv)           | 16.8       | 19.4       | 22.9       | 18  | 15  | 16.8  | 12.3  | 15    | 14.7 | 21.2 | 14.5  | 20    | 23   | 19    | 17    | 20.8   |

| NF<br>(dB)              | 6.6        | 5.4        | 3.6        | 4.2 | 5.2 | 7.2   | 4.9   | 4.7   | 4.8  | 3.5  | 4.6   | 4     | 1.85 | 2.4   | 3     | 2.2    |

| IIP3<br>(dBm)           | -16.4      | -16.8      | -17.2      | -14 | -9  | -16   | -11   | -6.5  | 2    | -2   | -1    | -12   | -2.8 | 8.6   | 7.9   | -11    |

| P <sub>DC</sub><br>(mW) | 0.35       | 0.9        | 2          | 0.2 | 0.2 | 0.3   | 0.4   | 0.55  | 0.6  | 1    | 1.2   | 1.3   | 2.8  | 3.1   | 3.7   | 3.8    |

| BW<br>(GHz)             | 4          | 5.2        | 4.5        | 1   | 2.2 | 5.5   | 2.2   | 2.4   | 2.5  | 2.7  | 2.7   | 2.7   | 1.7  | 2     | 5.8   | 3.5    |

| Techno.<br>(nm)         | 28         | 28         | 28         | 180 | 180 | 28    | 130   | 28    | 180  | 65   | 65    | 130   | 90   | 130   | 28    | 130    |

| Area<br>(mm2)           | 0.0015     | 0.0015     | 0.0015     | 0.3 | 1.5 | 0.001 | 0.005 | 0.005 | 0.4  | 0.05 | 0.005 | 0.006 | 0.03 | 0.007 | 0.005 | 0.0017 |

| FOM<br>(GHz/mW)         | 22         | 21.8       | 24         | 24  | 26  | 29    | 10.8  | 12.5  | 11.2 | 25   | 6.4   | 13.5  | 9.5  | 3.9   | 11    | 15     |

TABLE 5. State of the art of low power inductorless LNAs.

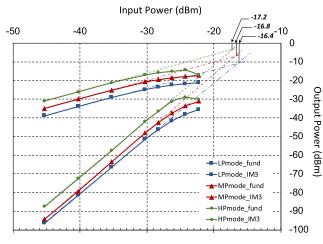

FIGURE 15. Measured IIP3 for the 3 modes of operation.

mode, at 2.4GHz, the voltage gain and noise figure are respectively 16.8dB and 6.6dB. In medium performance mode, they are 19.4dB and 5.4dB, respectively. For these two modes of operation, the LNA addresses the set of specifications. In high performance mode, the voltage gain is 22.9dB, expected at 26dB in theory, and the NF is 3.6dB, expected at 3dB in theory. Based on the investigation proposed in [3], the estimated sensitivity of the receiver in high performance mode is -89.9dBm, expected at -90dBm in theory. We can assume that the LNA addresses the targeted scenario of application in the three modes of operation.

To determine the IIP3, a two tone test with 2.40GHz and 2.41GHz is applied at the input of the LNA. Interestingly, the intermodulation products remain constant over the 3 modes of operation. We observe, Fig. 15, a degradation of only 0.8dB between the LP mode, at -16.4dBm, and the HP mode, at -17.2dBm. The active Gm-boosted configuration is less linear than a single-stage common source, or common gate, topology. Indeed, the distortions generated by the CS stage

83438

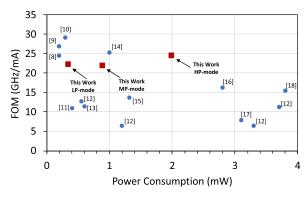

FIGURE 16. FOM comparison for the state-of-the-art references.

$M_{2i}$  in Fig. 10 are directly applied on the gate of  $M_{1i}$ , and further distorted.

Table 5 reports some state-of-the-art inductorless LNAs, except [9], which exploits inductive degeneration. Considering the scenario of application, it only contains some circuits with a power consumption which does not exceed 4 mW. The proposed LNA achieves the highest voltage gain in HP-mode with [16], and among the lowest power consumption (350uW) in LP-Mode with [8]-[10]. We observe the limitation on the power consumption strongly impacts the noise figure, which remains above 4dB for a P<sub>DC</sub> below 600uW [8]-[13]. Interestingly, the noise figure limitation seems to be technology independent. Unlike the bandwidth and the gain-bandwidth, the in-band noise performance does not improve with shrinking technology. As mentioned, an active Gm-boosted configuration remains limited in terms of linearity. The proposed LNA exhibits the lowest IIP3, but it is consistent with the specifications (Table 1) for the case of application.

For the works reported in Table 5, the associated FOM, defined in (5), is represented as a function of the power consumption in Fig. 16. It is important to note that the LNAs

FIGURE 17. Small signal model of a MOS transistor including thermal noise source.

reported so far are optimized for a single bias point. The proposed LNA not only achieves among the best values of the FOM, but it maintains the FOM at a constant level over a large range of power consumption.

#### **VI. CONCLUSION**

In this paper, a multi-mode inductorless LNA is analyzed and implemented in a 28nm CMOS FDSOI technology. The Gm-boosted architecture, featuring a common gate configuration and a common source stage, achieves a high current efficiency, allowing for low power design. To optimize the trade-off between performance and current consumption in each mode of operation, a design algorithm based on the inversion coefficient is used to explore the design space of the LNA. This approach leads to three design configurations which are further combined and implemented. The reconfiguration is performed by adjusting the IC and the size of the transistors through a combination of current steering and back bias switching of some multi-gated transistors. The LNA achieves among the best FOM, between 22 and 24 GHz/mA, reported so far, for inductorless configurations over a large range of power consumption, from 0.35mW to 2 mW. To the knowledge of the authors, none of the circuits reported so far in the literature are capable of such behavior. The measured performance at 2.4GHz addresses the set of specifications defined for a multi-mode RFFE dedicated to WSN applications. In the high-performance mode, the gain is maximal, 22.9dB, and the NF is minimal, 3.6dB. In the low power mode, the LNA only consumes 0.35mW, and still achieves a gain of 16.8dB and a noise figure of 6.6dB. The IIP3 remains constant, close to -16 dBm, in any mode of operation.

#### **APPENDIX**

This appendix introduces the equivalent small signal model of the MOS transistor described with the inversion coefficient according [7], including thermal noise sources reported in Fig. 17.

For the small signal model:

$$\begin{split} g_m\left(IC, W, L\right) &= \frac{G_m\left(IC, \lambda_c\right) . I_{spec} \Box}{U_T} . \frac{W}{L} \\ \text{with} : G_m\left(IC, \lambda_c\right) &= \frac{1}{n} . \frac{\sqrt{(IC.\lambda_c + 1)^2 + 4.IC} - 1}{\lambda_c . (IC.\lambda_c + 1) + 2} \\ g_{ds}\left(IC, W, L\right) &= \frac{IC.I_{spec} \Box}{\alpha_{G_{ds}}.L} . \frac{W}{L} \end{split}$$

$$\begin{split} C_{ij}\left(W\right) &= C_{ij\_W}.W\\ r_{G}\left(W,L\right) &= R_{G\Box}.\frac{W}{L} \end{split}$$

For the noise sources:

$$\begin{split} i_{nd}^{2} & (\text{IC}, \text{W}, \text{L}) = 4kT.\gamma_{n} (\text{IC}) \text{ g}_{\text{m}}. (\text{W}, \text{L}, \text{IC}) \\ v_{r_{g}}^{2} & (\text{W}, \text{L}) = 4kT.r_{G} \end{split}$$

The technological parameters for the 28nm FD SOI CMOS technology from ST are extracted with Cadence. They are reported in the following table:

| Parameter                            | NMOS    |  |  |  |  |

|--------------------------------------|---------|--|--|--|--|

| 1 araineter                          | (svtlp) |  |  |  |  |

| $I_{spec\square}(nA)$                | 930     |  |  |  |  |

| n                                    | 1.55    |  |  |  |  |

| $\lambda_{c}$                        | 0.42    |  |  |  |  |

| C <sub>gs w</sub> (fF/µm)            | 0.46    |  |  |  |  |

| $C_{gd w}(fF/\mu m)$                 | 0.22    |  |  |  |  |

| $C_{bd_w}$ (fF/ $\mu m$ )            | 0.20    |  |  |  |  |

| $R_{G\square}$ (Ohm/m <sup>2</sup> ) | 21.3    |  |  |  |  |

| $\gamma_{ m wi}$                     | 0.87    |  |  |  |  |

#### ACKNOWLEDGMENT

The authors would like to thank M. De Matos, Engineer at IMS Laboratory, for her support in the characterization of the circuit.

#### REFERENCES

- A. Bachir, M. Dohler, T. Watteyne, and K. K. Leung, "MAC essentials for wireless sensor networks," *IEEE Commun. Surveys Tuts.*, vol. 12, no. 2, pp. 222–248, 2nd Quart., 2010.

- [2] M. Raja, X. Chen, Y. D. Lei, Z. Bin, B. C. Yeung, and Y. Xiaojun, "A 18 mW Tx, 22 mW Rx transceiver for 2.45 GHz IEEE 802.15.4 WPAN in 0.18-μm CMOS," in *Proc. Solid State Circuits Conf. (A-SSCC)*, Nov. 2010, pp. 1–4.

- [3] J. Zaini, F. Hameau, T. Taris, D. Morche, L. Q. V. Tran, and P. Audebert, "Channel aware receiver front end for low power 2.4 GHz wireless sensor network: A system level analysis," in *Proc. 14th IEEE Int. New Circuits Syst. Conf. (NEWCAS)*, Jun. 2016, pp. 1–4.

- [4] D. Shaeffer and T. Lee, "A 1.5 V, 1.5GHz CMOS low noise amplifier," IEEE J. Solid-State Circuits, vol. 32, no. 5, pp. 745–759, May 1997.

- [5] H. Satou, H. Yamazaki, K. Kobayashi, T. Mori, and Y. Watanabe, "5.3 GHz 1.6 dB NF CMOS low noise amplifier using 0.11 µ/m technology," in *IEE Radio Freq. Integr. Circuits (RFIC) Syst. Dig. Papers*, Forth Worth, TX, USA, Jun. 2004, pp. 109–112, doi: 10.1109/RFIC.2004.1320541.

- [6] K.-H. Chen and S.-I. Liu, "Inductorless wideband CMOS low-noise amplifiers using noise-canceling technique," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 2, pp. 305–314, Feb. 2012.

- [7] C. C. Enz and E. A. Vittoz, Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power RF IC Design. New York, NY, USA: Wiley, 2006.

- [8] H.-J. Liu and Z.-F. Zhang, "An ultra-low power CMOS LNA for WPAN applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 2, pp. 174–176, Feb. 2017, doi: 10.1109/LMWC.2016.2647382.

- [9] C. J. Jeong, W. Qu, Y. Sun, D. Y. Yoon, S. K. Han, and S. G. Lee, "A 1.5 V, 140μA CMOS ultra-low power common-gate LNA," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2011, pp. 1–4, doi: 10.1109/RFIC.2011.5940634.

- [10] J. Zaini, F. Hameau, T. Taris, D. Morche, P. Audebert, and E. Mercier, "A tunable ultra low power inductorless low noise amplifier exploiting body biasing of 28 nm FDSOI technology," in *Proc. IEEE/ACM Int. Symp. Low Power Electron. Design (ISLPED)*, Jul. 2017, pp. 1–6, doi: 10.1109/ISLPED.2017.8009161.

- [11] M. Parvizi, K. Allidina, and M. N. El-Gamal, "An ultra-low-power wideband inductorless CMOS LNA with tunable active shunt-feedback," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 6, pp. 1843–1853, Jun. 2016, doi: 10.1109/TMTT.2016.2562003.

- [12] G. Guitton, M. De Souza, A. Mariano, and T. Taris, "Design methodology based on the inversion coefficient and its application to inductorless LNA implementations," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 3, pp. 1–11, May 2018, doi 10.1109/TCSI.2019.2914502.

- [13] Z. Li, Z. Wang, M. Zhang, L. Chen, C. Wu, and Z. Wang, "A 2.4 GHz ultra-low-power current-reuse CG-LNA with active G<sub>m</sub> -boosting technique," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 5, pp. 348–350, May 2014, doi: 10.1109/LMWC.2014.2309091.

- [14] Z. Pan, C. Qin, Z. Ye, Y. Wang, and Z. Yu, "Wideband inductorless low-power LNAs with Gm enhancement and noise-cancellation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 1, pp. 26–38, Jan. 2018, doi: 10.1109/TCSI.2017.2710057.

- [15] F. Belmas, F. Hameau, and J. Fournier, "A low power inductorless LNA with double Gm enhancement in 130 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 5, pp. 1094–1103, May 2012, doi: 10.1109/JSSC.2012. 2185533.

- [16] E. Ahmed Sobhy, A. A. Helmy, S. Hoyos, K. Entesari, and E. Sanchez-Sinencio, "A 2.8-mW sub-2-dB noise-figure inductorless wideband CMOS LNA employing multiple feedback," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 12, pp. 3154–3161, Dec. 2011, doi: 10. 1109/TMTT.2011.2169081.

- [17] M. De Souza, A. Mariano, and T. Taris, "Reconfigurable inductorless wideband CMOS LNA for wireless communications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 3, pp. 675–685, Mar. 2017, doi: 10.1109/TCSI.2016.2618361.

- [18] J. Borremans, P. Wambacq, C. Soens, Y. Rolain, and M. Kuijk, "Lowarea active-feedback low-noise amplifier design in scaled digital CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 11, pp. 2422–2433, Nov. 2008, doi: 10.1109/JSSC.2008.2005434.

**THIERRY TARIS** (Senior Member, IEEE) received the master's and Ph.D. degrees from the University of Bordeaux (UB), France, in 2000 and 2003, respectively.

He joined the IMS Laboratory, in 2005, as an Associate Professor of UB, and then the Bordeaux Institute of Technology (Bx-INP), in 2014, as a Professor. Since 2008, he has been enrolled as a coordinator and a scientific contributor for more than 12 European and National projects. He has

published more than 100 articles in international journals and conferences, three best paper awards, and is the co-inventor of six patents. He has led the circuit design group, from 2011 to 2014, at IMS Laboratory. He was an Invited Professor with The University of British Columbia (UBC), Vancouver, BC, Canada, in 2012 and 2014, and the École Polytechnic Federal de Lausanne (EPFL), Lausanne, Switzerland, in 2016. His research interest includes the radio-frequency integrated circuits in silicon technologies. For six years, he has been a Board Member of the ST-IMS joined Lab between the IMS Laboratory and ST-Microelectronics. He is currently developing joint research with NXP. Since 2016, he has been an Expert for the Strategic Business Area (SBA) of the "pôle de compétitivité" Aerospace Valley.

JENNIFER DESEVEDAVY (ZAINI) (Member, IEEE) received the M.Sc. degree in electronics from the Institut National des Sciences Appliquées in Lyon, France, in 2015, and the Ph.D. degree in the design of tunable ultra-low power integrated circuits for the Internet of Things applications from the University of Bordeaux within CEA-Leti, in 2018. Since 2018, she has been working on the development of 5G communication at Orange, France.

**FRÉDÉRIC HAMEAU** (Member, IEEE) received the M.S. degree from the ENSEIRB Engineering School in Bordeaux, France, in 2001. He joined CEA-Leti, Grenoble, France, in 2001, as a Radiofrequency Research Engineer. In 2005, he was involved in the development of ultra-lowpower (ULP) systems on chip, compatible with IEEE802.15.4 standard. In 2012, he was a Technical Leader in the development of an impulse radio ultra-wideband (IR-UWB) SOC compatible with

IEE802.15.4a standard. Since 2014, while he has been still working in the UWB and ULP field, he joins the mmW team working on 28 and 60 GHz design. He has published more than 24 articles in international conferences and journals. And, he is the co-inventor of 11 patents. His research interests include SOC integration in CMOS and FDSOI advanced technology.

**PATRICK AUDEBERT** (Member, IEEE) was born in Digne, France, in 1967. He received the Diploma degree in electronics engineering from the Polytech Institute of Montpellier.

In 1990, he joined the CEA-Leti Laboratory, Center for Innovation in Micro- and Nanotechnology (MINATEC), Grenoble. He was involved in the design of readout integrated circuits for infrared focal plane array into military or space applications or for X-ray medical sensors. In 2002,

he moved to the microsystems interface applications, where he was in charge of development of the electronic and system interface for power management application of microbattery, for MEMS gyrometer sensors and NEMS accelerometer sensors. From 2008 to 2011, he joined brain computer interface project, where he was the Design Leader and he was in charge of analog part of the BCI integrated circuits. Since 2011, he has been working in the radio frequency team, and more specifically in RF ultra-lower applications. He has published more than 30 articles. He holds close to 20 patents in the fields of matrix, sensor interfaces, and ADC or RF architectures.

**DOMINIQUE MORCHE** (Senior Member, IEEE) received the Diploma degree in engineering from the École Nationale Supérieure d'Electricité et de Radioelectricité de Bordeaux (ENSERB), in 1990, and the Ph.D. degree in electronics from the Institut National Polytechnique de Grenoble (INPG), in 1994. His Ph.D. mainly focuses on sigma-delta ADC. From 1994 to 2001, he was employed with France Telecom as a Research Engineer. He has been involved in architecture and design of analog

circuits for telecom application. He is currently working with CEA-Leti. His current research interests include the specification and design of RF architecture for the IoE and 5G systems.