# Demonstration of SiC-on-insulator substrate with Smart Cut<sup>TM</sup> technology for photonic applications

Stéphanie Huet, Sylvain Guerber, Emmanuel Rolland, Bertrand Szelag, Guillaume Gelineau, Alexandre Moulin, Vladimir Prudkovskiy, Nicolas Troutot, Christophe Licitra, Patrice Gergaud, et al.

#### ▶ To cite this version:

Stéphanie Huet, Sylvain Guerber, Emmanuel Rolland, Bertrand Szelag, Guillaume Gelineau, et al.. Demonstration of SiC-on-insulator substrate with Smart Cut<sup>TM</sup> technology for photonic applications. Materials Science Forum, 2024, 1124, pp.67-76. 10.4028/p-Cb7qw4. cea-04752745

### HAL Id: cea-04752745 https://cea.hal.science/cea-04752745v1

Submitted on 24 Oct 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Demonstration of SiC-on-insulator substrate with Smart Cut™ technology for photonic applications

Stéphanie HUET<sup>1,a\*</sup>, Sylvain GUERBER<sup>1,b</sup>, Emmanuel ROLLAND<sup>1</sup>, Bertrand SZELAG<sup>1</sup>, Guillaume GELINEAU<sup>1</sup>, Alexandre MOULIN<sup>1</sup>, Vladimir PRUDKOVSKIY<sup>1</sup>, Nicolas TROUTOT<sup>1</sup>, Christophe LICITRA<sup>1</sup>, Patrice GERGAUD<sup>1</sup>, Sophie BARBET<sup>1</sup>, Mathieu DELCROIX<sup>1</sup>, Simon CARIDROIT<sup>1</sup>, Vincent AMALBERT<sup>1</sup>, Carlos ALONSO-RAMOS<sup>2</sup>, Daniele MELATI<sup>2</sup>, Samson EDMOND<sup>2</sup>, Laurent VIVIEN<sup>2</sup>, Karine MONY<sup>3</sup>, Gérard LAPERTOT<sup>3</sup> and Julie WIDIEZ<sup>1,c</sup>

<sup>1</sup> Univ. Grenoble Alpes, CEA, Leti, F-38000 Grenoble, France

<sup>2</sup> Univ. Paris-Saclay, CNRS, C2N, F-91120 Palaiseau, France

<sup>3</sup> Univ. Grenoble Alpes, CEA, IRIG, PHELIQS, F-38000 Grenoble, France

a <u>stephanie.huet@cea.fr</u> (corresponding author), b <u>sylvain.guerber@cea.fr</u>, c <u>julie.widiez@cea.fr</u>

**Keywords:** SiC-on-insulator (SiCOI), Smart Cut<sup>™</sup>, transferred layer, bow compensation, photonic devices, simulation.

**Abstract.** Silicon-carbide-on-insulator (SiCOI) is a promising platform for photonic integrated circuits. However, the development of this new photonic platform is hindered by the lack of high-quality commercial SiC-on-insulator substrates. In this study, we present a demonstration of the transfer of a single crystalline semi-insulating 4H-SiC thin film on a SiO<sub>2</sub> insulated substrate at 150 mm wafer scale using the Smart Cut<sup>TM</sup> technology. We describe the development of SiCOI substrates and their characterization at each key step of the process. In particular, we provide a detailed study of bow compensation related to the implanted SiC donor substrate. The quality of the transferred SiC layer was investigated as a function of the final annealing temperature applied. The optical indices of the bulk SiC were measured using spectroscopic ellipsometry, and an advanced model has been used to take into account the strong birefringence of the silicon carbide film. Finally, simulations were conducted to design a preliminary set of basic and advanced photonic devices.

#### Introduction

For several years, silicon carbide (SiC) has been identified as a material of choice for many applications in power electronics [1-4] because of its remarkable properties, such as its high physical hardness, exceptional thermal conductivity (480 W.m<sup>-1</sup>.K<sup>-1</sup>), chemical inertia and wide band gap (2.4-3.2 eV). These unique characteristics mean that SiC power semiconductors can increase energy conversion efficiency, withstand higher voltages and currents as well as a higher operating temperature than conventional silicon-based devices [1]. Recent demonstrations show that SiC is a promising material for the realization of quantum and nonlinear photonic circuits [5-8]. Indeed, it combines many interesting optical properties: a wide transparency window (UV to mid-IR), high second and third order optical nonlinearity coefficients ( $\chi(2)$ ,  $\chi(3)$ ), a high refractive index and no two-photon absorption (TPA) at near infrared wavelengths. SiC also exhibits point defects (colored centers) which are promising for Qbit realization due to their long spin coherence time and room temperature operation.

SiC photonics has been explored for some years, with very recent breakthrough demonstrations [22] such as low-loss waveguides, high quality factor resonators, efficient on-chip frequency conversion via  $\chi(2)$  and the integration of single spin Qbits with nanophotonic cavities. This brings

SiC at the forefront of efforts towards a monolithic platform combining quantum and nonlinear photonics [9]. However, these developments are hampered by the lack of commercial SiC-oninsulator (SiCOI) wafers. In fact, the aforementioned demonstrations rely on extremely expensive and experimental SiCOI dies obtained by the bonding and thinning method [9, 10]. While offering better performance in terms of material quality, with the lowest measured optical losses (< 0.38 dB/cm [11, 12]), the bonded SiC layer thickness exhibits high variability across the wafer (in the micrometer range), while being extremely cost ineffective since most of the material is lost. Inspired by the fabrication of silicon on insulator wafers (SOI), SiCOI substrates fabricated with the ion cutting (named also Smart Cut<sup>TM</sup>) method are getting a growing interest. Despite higher material optical losses due to the ion implantation, microrings with reasonable Q-factor of 7.3×10<sup>4</sup> [13, 14] (~7 dB/cm) have recently been demonstrated in academic facilities, leaving room for further improvements. Thus, the good thickness uniformity as well as a limited cost are significant advantages for the realization of future commercial devices. However, the healing of the transferred SiC layer seems to be the key to the future of this technology. Building upon extensive experience and expertise in the Smart Cut<sup>TM</sup> process for fabricating substrates used in power components [15-17, 21] and optical devices [9, 13-14, 18-19, 22], this study seeks to showcase the cost-effective production of high-quality SiCOI wafers.

The paper focuses on the Smart Cut<sup>TM</sup> SiCOI manufacturing process. The key process steps are described, developed and punctuated by detailed characterizations. Building on the work of Rouchier *et al.* [15] and Gelineau *et al.* [16] on transferred SiC substrates for power electronics, we will show how we adapted this fabrication process for photonic applications. In this study, we chose to work with a monocrystalline SiC (mSiC) handle substrate (instead of Si) in order to understand the effects of high-temperature annealing (between 1200°C and 1600°C) on the healing of the transferred SiC layer as well as on its optical properties. This study would not have been possible if we had chosen a Si handle, due to the Si melting temperature of 1410°C as well as the strong CTE difference between Si and mSiC. With a view to industrialization, this handle monocrystalline SiC substrate can be replaced by a polycrystalline SiC one. The second part of this paper will be devoted to the design of the first components and the simulation of guides and resonators.

#### Process flow of SiC-on-insulator substrate

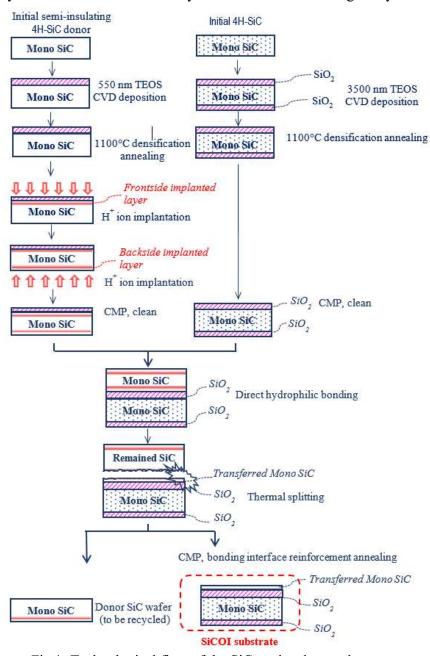

The fabrication process for the SiCOI substrates developed here using the Smart Cut<sup>™</sup> technology is schematized in Fig. 1.

First, semi-insulating donor wafers of high-purity 4H-SiC (N-doped  $\approx 5 \times 10^{11}$  cm<sup>-3</sup>), 150 mm diameter and 500 µm thick (from SICC) and receiver wafers of N-doped ( $\approx 5 \times 10^{18}$  cm<sup>-3</sup>) monocrystalline 4H-SiC 150 mm diameter and 350 µm thick (from DOW CORNING) were used. A protective, electrically insulating layer of silicon oxide is deposited by PECVD (Plasma Enhanced Chemical Vapor Deposition) on the front side of the donor substrate (550 nm) and on both the front and backside of the receiver substrate (3500 nm) to compensate for the important wafer curvature. Then, SiO<sub>2</sub> layers are densified by annealing at 1100°C.

Hydrogen ions (H<sup>+</sup>) are implanted at room temperature (RT) on the front side of the donor substrate through the 550 nm oxide layer. During the implantation step, the substrate is tilted by 7° to minimize the channeling effect. H<sup>+</sup> ion implantation creates a damaged layer below the implanted surface - the so-called "fracture zone" - the depth of which can be controlled according to the implantation energy [9, 17]. After front side H<sup>+</sup> implantation, a curvature compensation technique has been developed by counter hydrogen-implantation on the backside with a fluence inferior to Smart Cut<sup>TM</sup> one (low enough to prevent blistering of the backside of the wafer). This key step was characterized by bow measurements. It is extremely important since such curvature would degrade the bonding quality and complicate the use for future photonic platform processing equipments that work in automatic mode. To ensure a high-quality bonding, we polish the PECVD oxide on both substrates to reduce surface roughness. The two substrates are brought into contact for direct SiO<sub>2</sub>/SiO<sub>2</sub> bonding. Then, the bonded substrates undergo a thermal annealing at a temperature below 1000°C under N<sub>2</sub> to achieve

spontaneous fracture (also called splitting) (Fig. 1) and transfer of a layer of semi-insulating 4H-SiC onto the SiO<sub>2</sub>/SiC receiver substrate. Then, one of the SiCOI substrate has been annealed at 1200°C under N<sub>2</sub> for 1 hr to improve the bonding strength and heal the transferred SiC layer crystal, damaged by ion implantation-induced defects [17]. Another SiCOI substrate has been cleaved into 2×3 cm<sup>2</sup> samples. One was annealed at 1300°C, one at 1400°C, one at 1500°C and one at 1600°C, for 30 minutes. The last sample was left untouched in order to characterize the initial state of the transferred layer. Finally, chemical-mechanical polishing (CMP) is performed (on wafer and on samples) to remove the defect zones induced by ion implantation and to achieve a very low final surface roughness of the transferred mSiC layer. Thickness and uniformity of the transferred layer is monitored by spectroscopic ellipsometry. Surface topography of the transferred layer is characterized by atomic force microscopy (AFM). We also perform wafer warpage measurements at each step. The crystalline quality of the transferred 4H-SiC layer was characterized using X-ray diffraction (XRD).

Fig 1: Technological flow of the SiC-on-insulator substrate

Thus, once the SiCOI substrate obtained, the photonic devices can be defined using e-beam lithography. The patterns are then transferred in the SiC layer using SF<sub>6</sub>/O<sub>2</sub> via reactive ion etching (RIE).

#### Results and discussions

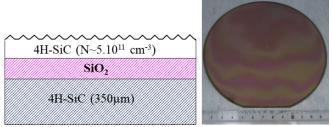

We have produced 150 mm SiCOI wafers with a 400 nm-thick mSiC layer transferred onto a monoSiC receiver substrate using a direct  $SiO_2/SiO_2$  bonding process. Fig. 2 shows a schematic cross-section of the resulting SiCOI substrate and a picture of the wafer after splitting. These substrates are visually of very good quality, with only very few bonding defects and with a thin edge exclusion (< 3 mm).

Fig 2: Picture and cross-sectional scheme of a 6" SiC-on-insulator substrate post splitting.

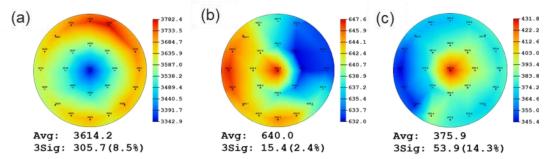

**Thickness measurement.** The thicknesses of the buried oxide layer (Fig. 3(a)) and the mSiC layer (as-transferred Fig. 3(b) and post-CMP Fig. 3(c)) were determined using spectroscopic ellipsometry. The average thickness of the oxide layer measures 3.6  $\mu$ m. The average thickness of the as-transferred 4H-SiC film is 640 nm, exhibiting excellent uniformity (< 2.5%) over the entire wafer surface as illustrated by the 25-point thickness map in Fig. 3(b). After polishing, the wafer's uniformity worsens to 14.3% and the average thickness reduced to 376 nm. As discussed later, an optimal mSiC thickness for optimal optical performance is targeted at 500 nm is. Our ongoing efforts are focused on optimizing the polishing process to minimize material removal and achieve a final thickness of approximately 500 nm.

Fig. 3: 25 points thickness maps of the (a) transferred oxide, (b) as-transferred 4H-SiC and (c) post CMP transferred 4H-SiC layers obtained by spectroscopic ellipsometry.

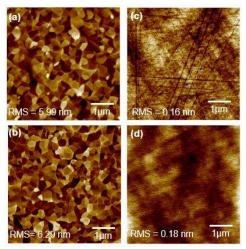

**AFM measurement.** Surface roughness of the transferred 4H-SiC film was measured by atomic force microscopy (AFM) at the center and edge of the 150 mm SiCOI wafer as shown in figures 4(a)-(d). Post splitting, the surface roughness is important at both the edge and the center of the wafer (as shown in Fig. 4(a) and Fig. 4(b), respectively) with a root mean square (RMS) roughness of about 6 nm on a scan of  $5\times5~\mu\text{m}^2$ . To obtain a smoother surface compatible with optical components fabrication, the surface of the SiCOI substrate is optimized by CMP over the entire 150 mm area as shown in Fig. 4(c)-(d). After the CMP step, the RMS roughness value is reduced to 0.16 nm at the wafer edge (Fig. 4(c)) and 0.18 nm at the center (Fig. 4(d)). The final substrates show a very good post-CMP surface finish.

Fig. 4: AFM images of as-transferred 4H-SiC film at (a) substrate edge and (b) center. (b) AFM images of 4H-SiC film post CMP at (c) substrate edge and (d) center.

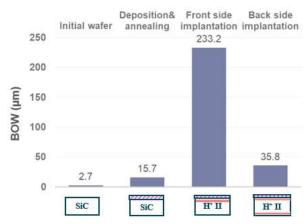

Bow compensation before direct bonding. In its original state, the SiC wafer shows little curvature (Fig.5, "initial wafer"). However, some process steps such as the oxide film deposition nor the ion implantation step can cause bow due to mechanical stress. We monitored the bow of the donor wafer after each step by interferometry. The Fig. 5 shows the results of bow measurements of the donor wafer after 500 nm SiO<sub>2</sub> deposition and annealing, front side H<sup>+</sup> ion implantation and backside H<sup>+</sup> ion implantation. H<sup>+</sup> front side implantation generates a large bow of 233.2  $\mu$ m with which the subsequent bonding step (see Fig. 1) would be difficult to carry out on un-optimized equipments. After backside H<sup>+</sup> implantation at a lower dose than that used for front side implantation (to prevent the donor substrate from blistering on the backside), the bow measurement is 36  $\mu$ m, which is compatible for direct bonding (Fig. 5). Thus, this technique allows to compensate for the strong curvature induced by hydrogen ion implantation in SiC and to return to a low final substrate curvature (< 40  $\mu$ m).

Fig. 5: Bow measurements of the donor wafer as received, after 500 nm SiO<sub>2</sub> deposition and annealing, after front side H<sup>+</sup> ion implantation and finally after backside H<sup>+</sup> ion implantation.

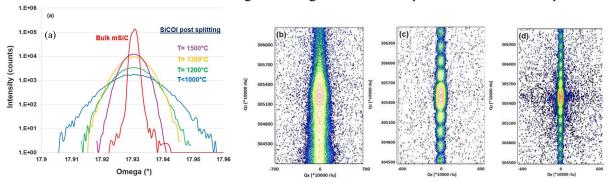

**XRD measurement.** In order to understand the effect of temperature on the crystalline quality of the transferred SiC layer, we carried out high temperature annealing (between 1200°C and 1600°C) on dedicated samples. XRD rocking curves (RCs) were compared between a bulk mSiC reference substrate and SiCOI substrates annealed at different temperatures: after splitting, post 1200°C, post 1300°C and post 1500°C. (Fig. 6(a)). We can see that the full width at half maximum (FWHM) of the RCs is much larger post-splitting and decreases with the application of annealing. However, even after annealing at 1500°C, the FWHM remains higher than that obtained on bulk mSiC. This means that the top mSiC material crystalline quality has not been completely healed even after 1500°C. The

crystal quality of transferred SiC layer was also investigated using XRD Reciprocal Space Mapping (RSM) of the (0004) 4H-SiC Bragg peak established on samples post splitting step (Fig. 6(b)) and post-annealed at  $1200^{\circ}$ C and at  $1500^{\circ}$ C (Fig. 6(c) and Fig. 6(d) respectively). One can immediately assess the important asymmetry in Qz post splitting (Fig. 6(b)) – corresponding to an important strain gradient in the transferred SiC layer. For  $T \ge 1200^{\circ}$ C however, a full relaxation of the crystal is observed, without any deformation gradient. The presence of residual hydrogen in the mSiC transferred layer post-splitting, as confirmed by SIMS analysis [16], is highly likely to be the root cause of the observed non-uniform crystal deformation. Nevertheless, the reasons behind the inadequacy of  $1500^{\circ}$ C annealing for healing the transferred layer and the specific defects implicated remain unclear. To gain deeper insights into this phenomenon, optical assessments of components fabricated on these substrates following annealing at various temperatures will be indispensable.

Fig. 6: (a) The (0004) XRD rocking curves for the bulk monocristalline 4H-SiC, for SiCOI post splitting (T < 1000°C) and for the SiCOI substrates post-annealed at 1200°C, 1300°C and 1500 °C. (b) XRD-RSM of the (0004) 4H-SiC Bragg peak established on samples post splitting step, (c) post-annealed at 1200°C and (d) at 1500 °C.

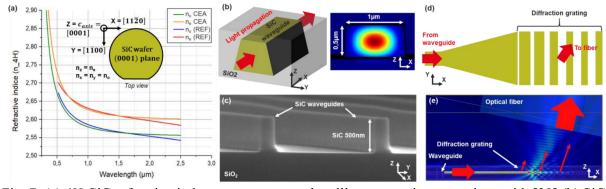

**Development of photonic devices.** First and foremost, the characteristics of the SiC guiding layer must be known in order to design the photonic devices. The optical indexes of the bulk SiC have been measured on a wavelength span from the visible to the near-infrared by ellipsometry. An advanced model has been used to take into account the strong birefringence of the silicon carbide. As shown on Fig. 7(a), the extracted ordinary and extra-ordinary refractive indices are in good agreement with previously reported values [20]. The thickness of the SiC layer has been fixed to 500 nm as a compromise between the waveguide propagation losses, devices compactness and nonlinear properties.

Fig. 7: (a) 4H-SiC refractive indexes measurement by ellipsometry, in comparison with [20] (b) SiC waveguide geometry and the associated modal simulation (electric field magnitude, Lumerical<sup>TM</sup> software from ANSYS [23]). (c) Scanning electron microscope view of fabricated SiC waveguides on SiCOI substrates (d) Chip-fiber coupler geometry and (e) the associated light propagation simulation [23].

Knowing the thickness and refractive index of the guiding layer, the conception of the basic photonic devices can begin with the more fundamental one: the optical waveguide. As shown on Fig. 8(b), the modal behavior of a SiC waveguide with typical dimensions  $(1\times0.5~\mu\text{m}^2)$  has been simulated in order to estimate its optical characteristics (effective optical index, chromatic dispersion, propagation losses, etc.). Using e-beam lithography and a standard etching process, waveguides were patterned and structured on SiCOI substrates as illustrated on Fig. 8(c). Another key component is the chip-fiber coupler which is used to transfer light to/from the small SiC waveguides (typical core size of the order of 100 nm) to/from standard optical fibers (typical core size of about 10  $\mu$ m) which can then be connected to an external light source (laser) or photodetectors. As shown on Fig. 8(d), it consists of an enlarged waveguide coupled to a diffractive grating that will extract the light into free space. Using optical simulations (Fig. 7(e)), its dimensions (period of the grating, width of the structure) can be tuned in order to maximize the waveguide-fiber coupling efficiency.

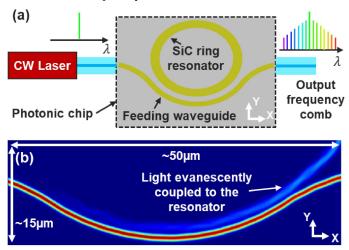

As mentioned in the introduction, by combining (i) a strong nonlinear coefficient  $\chi(3)$ , (ii) a high refractive index and (iii) low propagation losses, the silicon carbide is a material of choice for the realization of efficient optical nonlinear functions [11]. In particular, the generation of stable and intense Kerr frequency combs (ultra-stable multi spectral laser source) is of growing interest due to the vast field of applications [24]. As shown on Fig. 8(a), the light from an external continuous wave (CW) laser is injected to a feeding waveguide that is evanescently coupled to a looping waveguide (ring) that will act as a resonator. By tuning the optical power coupled to the resonator from the feeding waveguide (simulation Fig. 8(b)), an extremely high power density can be reached, which is key to trigger the generation of the frequency comb.

Fig. 8: (a) Principle of the generation of a Kerr frequency comb (multi spectral laser source) using a SiC microring resonator. (b) Simulation of the feeding waveguide – ring light coupling efficiency.

#### **Summary**

This work presents the 150 mm SiCOI substrates fabricated using the Smart Cut<sup>TM</sup> technology. A 400 nm mSiC layer was successfully transferred onto a thick (> 1  $\mu$ m) SiO<sub>2</sub> layer. The SiCOI substrates, obtained through a technologically optimized process involving the use of the Smart Cut<sup>TM</sup> technology and a meticulous bow compensation technique, are devoid of bonding defects, exhibit a final low surface roughness value (< 0.2 nm) and present a thin edge exclusion. XRD measurements show that the transferred mSiC layer post splitting exhibits a significant strain gradient. For T  $\geq$  1200°C, the transferred SiC layer completely loses this deformation gradient and as the annealing temperature increases, the crystalline quality of the layer improves. Thanks to advanced optical simulations, photonic devices will be fabricated on all these SiCOI substrates, enabling us to determine the impact of the quality of the transferred layer on the optical properties of these devices.

As the state of the art of SiCOI substrates made using the Smart Cut<sup>™</sup> technology is with maximum annealing at 1200°C, we should see a significant improvement in optical performance.

#### Acknowledgement

This project has received funding from the Key Digital Technologies (KDT) under Grant Agreement No 101007237. The KDT receives support from the European Union's Horizon 2020 research and innovation programme and Germany, France, Italy, Sweden, Austria, Czech Republic, Spain. Part of this work, performed on the Platform for NanoCharacterisation (PFNC) of CEA, was supported by the "Recherche Technologique de Base" Program of the French Ministry of Research.

#### References

- [1] T. Kimoto *et al.*, Jpn. J. Appl. Phys. 54, 040103 (2015).

- [2] M. Östling *et al.*, 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and ICs, San Diego, CA, USA, 10-15 (2011).

- [3] S. Laferriere *et al.*, "Power SiC: Materials, Devices and Applications 2020", Yole, Market and Technology, (2020).

- [4] X. She et al., IEEE transactions on industrial electronics, vol.64, n°10, 8193-8205 (2017).

- [5] D. D. Awschalom *et al.*, Nature Photonics 12, 516-527 (2018).

- [6] C. P. Anderson et al., Science 366, 1225-1230 (2019).

- [7] B. S. Song et al., Optica 6, 991-995 (2019).

- [8] D. M. Lukin et al., Nature Photonics (2019).

- [9] A. Yi et al., Appl. Phys. Rev. 9, 031302 (2022).

- [10] C. Wang et al., Light Sci. Appl. 10, 139 (2021).

- [11] M. A. Guidry et al., Nat. Photonics 16, 52-58 (2022).

- [12] M. A. Guidry et al., Optica, vol. 7, no 9, 1139-1142, (2020).

- [13] J. Cardenas et al., Optics Letters, vol. 40, No. 17, 4138-4141 (2015).

- [14] Y. Zheng et al., Optics Express, vol. 27, No. 9, 13053-13060 (2019).

- [15] S. Rouchier et al., Mat. Sci. Forum, vol. 1062, 131-135 (2021).

- [16] G. Gelineau et al., Mat. Sci. Forum, vol. 1089, 71-79 (2022).

- [17] L. Di Ciocci et al., Mat. Sci. and Eng. B46, 349-356 (1997).

- [18] Y. Zheng et al., Optics Letters, vol. 44, No. 23, 5784-5787 (2019).

- [19] X. Shi et al., Photonics Research, vol. 10, No. 1, A8-13 (2022).

- [20] S. Wang et al., Laser&Photonics Rev.7, No. 5, 831-838 (2013).

- [21] Letertre et al., Phys. Stat. Sol. (c) 0, No. 7, 2103–2106 (2003).

- [22] H. Ou et al., Materials, 16, 1014 (2023).

- [23] https://www.lumerical.com/, accessed online on 09/2023.

- [24] T. J. Kippenberg et al., Science, 332, 555-559 (2011).