## Normally-OFF 650V GaN-on-Si MOSc-HEMT Transistor: Benefits of the fully recessed gate architecture

Cyrille Le Royer, Blend Mohamad, Jérôme Biscarrat, Laura Vauche, René Escoffier, Julien Buckley, Stéphane Becu, Rémi Riat, Charlotte Gillot, Matthew Charles, et al.

### ▶ To cite this version:

Cyrille Le Royer, Blend Mohamad, Jérôme Biscarrat, Laura Vauche, René Escoffier, et al.. Normally-OFF 650V GaN-on-Si MOSc-HEMT Transistor: Benefits of the fully recessed gate architecture. ISPSD 2022 - IEEE 34th International Symposium on Power Semiconductor Devices and ICs, May 2022, Vancouver, Canada. 2022, 10.1109/ISPSD49238.2022.9813672. cea-04577370

### HAL Id: cea-04577370 https://cea.hal.science/cea-04577370v1

Submitted on 16 May 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Normally-OFF 650V GaN-on-Si MOSc-HEMT Transistor: Benefits of the Fully Recessed Gate Architecture

C. Le Royer<sup>1</sup>, B. Mohamad<sup>1</sup>, J. Biscarrat<sup>1</sup>, L. Vauche<sup>1</sup>, R. Escoffier<sup>1</sup>, J. Buckley<sup>1</sup>, S. Bécu<sup>1</sup>, R. Riat<sup>1</sup>, C. Gillot<sup>1</sup>, M. Charles<sup>1</sup>, S. Ruel<sup>1</sup>, P. Pimenta-Barros<sup>1</sup>, N. Posseme<sup>1</sup>, P. Besson<sup>1</sup>, F. Boudaa<sup>1</sup>, C. Vannuffel<sup>1</sup>, W. Vandendaele<sup>1</sup>, A.G. Viey<sup>1</sup>, A. Krakovinsky<sup>1</sup>, M.-A. Jaud<sup>1</sup>, R. Modica<sup>2</sup>, F. Iucolano<sup>2</sup>, R. Le Tiec<sup>3</sup>, S. Levi<sup>3</sup>, M. Orsatelli<sup>4</sup>, R. Gwoziecki<sup>1</sup>, V. Sousa<sup>1</sup>

<sup>1</sup>CEA, LETI, MINATEC Campus, F-38054 Grenoble, France and Univ. Grenoble Alpes, F-38000 Grenoble, France. cyrille.leroyer@cea.fr

<sup>2</sup> STMicroelectronics, Stradale Primosole 50,95121 Catania, Italy

<sup>3</sup> PDC business group, Applied Materials, Rehovot 76705, Israel

<sup>4</sup>CEA Tech Occitanie, F-31670 Labège, France.

Abstract— In this paper we present a detailed performance status of AlGaN/GaN MOS channel High Electron Mobility Transistors (MOSc HEMTs) with fully recessed gate architecture on 200mm Si substrates. We report a wide range of wafer and package level results. ON state resistance is studied through three aspects: *i*) RoN partitioning with analysis of its four components, *ii*) RoN temperature dependence, *iii*) cumulative dynamic R<sub>ON</sub> under stress. For accurate power assessment we characterize packaged devices and compare the typical figures of merit (gate charge, switching tests) to state of the art references (especially pGaN gate HEMTs). We highlight the benefits offered by this technology for 650V applications, such as very low I<sub>GSS</sub> leakage even at 150°C, and better switching performances, t<sub>d(on)</sub>, t<sub>d(off)</sub>.

Keywords—Power, GaN-on-Si, AlGaN/GaN, MOSc HEMT, fully recessed gate architecture, 200mm Si substrates, ON state resistance, 650V application, packaged devices

#### I. INTRODUCTION

For power transistors [1-11] the three main general requirements are a <u>high breakdown voltage</u>, <u>normally-OFF</u> operation and a <u>low ON state resistance</u> ( $R_{ON}$ ). Wide bandgap materials such as GaN have high critical electrical field, making GaN HEMTs especially adapted to reach the high breakdown voltage requirement. Different approaches have been considered to achieve GaN HEMTs normally-OFF operation. The two most promising concepts are the **pGaN gate** (today's commercial solution [3-4]) and the **recessed gate MOSc-HEMT** [1-2], [8-11], which is the scope of this paper.

In this paper, we first present our latest integration process and new in-line gate cavity characterizations (**Part II**). Then we focus on  $R_{ON}$  studies and on the advantages offered by recessed gate MOSc-HEMT (**Part III**). Finally we extend these analysis to packaged devices (**Part IV**).

#### II. TECHNOLOGY AND DEVICE DESCRIPTION

#### A. Normally OFF Recessed AlGaN/GaN MOSc HEMT flow

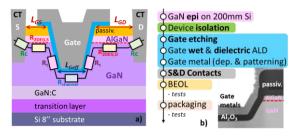

Normally OFF Recessed AlGaN/GaN MOS-HEMTs on 200mm Si substrates are fully fabricated in our clean rooms. The device structure is illustrated in Fig. 1a, and the related process flow is described in Fig. 1b.

Fig. 1. a) Schematics of the fabricated GaN-on-Si MOSc-HEMT with fully recessed gate. The four  $R_{ON}$  components (Fig. 4) are also indicated. b) Summary of the developed process flow for 200mm GaN-on-Si E-mode MOS channel HEMT, with fully recessed gate (+TEM image).

After growth by MOCVD of transition and GaN:C layers on Si the epi stack ends with an unintentionally doped (uid GaN) channel, AlN spacer, AlGaN barrier and in-situ SiN passivation layer. The gate structure is formed by AlGaN/GaN dry etching (fully recessed gate), followed by adapted GaN surface conditioning, dielectric (30nm ALD Al<sub>2</sub>O<sub>3</sub>) and metals depositions. The ohmic source-drain contacts are formed with fullrecess etching and low temperature Ti/Al process. The wafer process finishes with three levels Back-End Of Line (M3) and inline electrical characterizations. After dicing, 30A-650V calibrated transistors are packaged for final electrical assessments

#### B. New in-line 3D characterization method for gate cavity

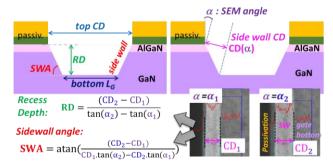

An in line CD-SEM measures 2D distances between edges. For 3D pattern metrology we developed an original and efficient technique based on eTilt SEM imaging [6]. By tilting the primary electron beam, sidewalls of patterns become visible and measurable for single line edges, or for multiple line edge statistics. To deconvolve sidewall angle from pattern thickness variation, two images with different eTilt ( $\alpha_1$ ,  $\alpha_2$ ) were taken on the same target extracting the AlGaN/GaN Edge Width CD (**Fig. 2**).

Fig. 2. Gate cavity in-line measurements. Recess Depth, RD, and Sidewall angle, SWA, are calculated using two off-angle CD-SEM measurements.

This work was funded by the French national program "programme d'Investissements d'Avenir IRTNanoelec" ANR-10-AIRT-05.

This technique was applied to measure the etched gate recess depth (RD) and sidewall angle (SWA) and developed on shortloop wafers with four different etching processes. **Fig. 3** shows an example of sidewall angle values obtained with this technique, and the correlation with bottom CD values. This methodology was validated by different comparisons (RD & SWA from TEM) and **Fig. 3** shows the self-consistency of the technique (top  $L_G$ , bottom  $L_G$ , SWA and RD).

Fig. 3. Illustration of in-line characterizations (SWA vs. bottom  $L_G$ ) from shortloop wafers. Model based SWA calculations show a good matching with the method data points (results from four etch conditions, two wafers per split, 41 dies per wafer, for a given device layout).

This 3D method enables us to analyze the impact of random process induced variations across the wafer and opens new opportunities for fine process/electrical correlation studies.

#### III. DEVICE RESULTS (WAFER LEVEL)

#### A. R<sub>ON</sub> partitioning study

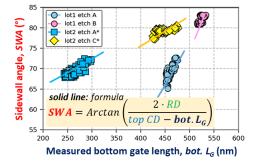

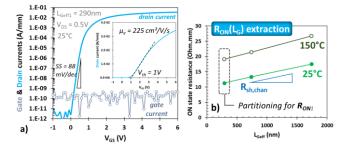

One critical aspect for device optimization is the  $R_{ON}$  minimization. It is thus essential to accurately determine its components (**Fig. 4**:  $R_{ON} = 2.Rc+R_{2DEG}+2.R_t+R_{channel}$  [5,11]) in order to optimize the related modules. TLMs are used to determine contact resistance (Rc) and 2DEG sheet resistance ( $R_{sh,2DEG}$ ). Channel sheet resistance ( $R_{sh,channel}$ ) is obtained from  $R_{ON}(L_{Geff})$  curves measured on transistors with different gate lengths (**Fig. 5**). It is important to point out that the effective gate length  $L_{Geff}$  to consider in recessed-gate structure is the bottom gate length described in **Fig. 2**.

Once these parameters have been extracted, one can apply this method to any device with known layout ( $L_{Geff}$ , W,  $L_{GS}$ ,  $L_{GD}$ ) with the formulas reported in **Fig. 4**. An example of this is shown in **Figs. 5-6**.

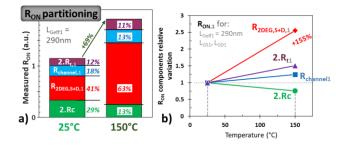

Fig. 4. **a**)  $R_{ON}$  partitioning model (with related modules). **b**) Application of the method for a given device (DUT'1'). The four  $R_{ON}$  contributions are determined for each die of a given wafer.

**Fig. 5a** is an example of  $I_D(V_G)$  characteristics at room temperature with excellent performance: Vth=+1V, SS=88mV/dec. These curves illustrate the intrinsic gain of this architecture with respect to pGaN gate: gate current is very low ( $I_D/I_G>8$  decades in **Fig. 5a**, and ~3 decades for pGaN [3-4]). The extracted low field mobility  $\mu$  (225 cm²/V/s) outperforms most published MOS channel HEMT results (see review [11]). Note that MOSc HEMT technology is capable of supporting large V<sub>G</sub>, such as 20V (not shown here), which outperforms pGaN. Fig. 5b illustrates the linear R<sub>ON</sub>(L<sub>G,eff</sub>) at 25°C and 150°C. For the smallest gate length device, we report the R<sub>ON</sub> partitioning for these two temperatures (Fig. 6a). One can note that the 2DEG resistance is the main contributor to the total R<sub>ON</sub>, and shows the largest temperature dependency (Fig. 6b). Therefore, for the next device generations 2DEG R<sub>sheet</sub> reduction and layout (L<sub>GS</sub>, L<sub>DG</sub>) have to be carefully considered.

Fig. 5. **a)** Measured drain and gate currents (I<sub>D</sub>, I<sub>G</sub>) as function of gate voltage V<sub>GS</sub> in log scale (insert: linear scale for I<sub>D</sub>) at 25°C. **b)** Typical R<sub>ON</sub>(L<sub>G,eff</sub>) curves at 25°C and 150°C: Measured R<sub>ON</sub> (at V<sub>GS</sub>=+6V, V<sub>DS</sub>=+0.5V) is plotted as function of effective bottom gate length L<sub>Geff</sub>.

Fig. 6. **a**) Example of  $R_{ON}$  partitioning at two temperatures (cf. Fig. 6). For a given device (with fixed L<sub>G</sub>, W, L<sub>GS</sub>, L<sub>GD</sub>) we determine the four  $R_{ON}$ components using the method described in Fig. 5. **b**) Illustration of the temperature relative impact on the four  $R_{ON}$  components (for the 290 nm  $L_{Geff}$  device partitioning, Fig. 6a).

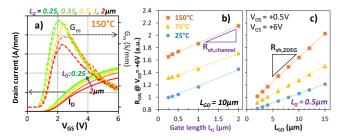

#### B. Advantages of MOSc HEMT R<sub>ON</sub> temperature behaviour

The considered architecture with fully recessed-gate MOSc-HEMT has the advantage of a smaller  $R_{ON}$  temperature coefficient compared to pGaN gate technology. This is detailed and explained in **Figs. 7-8**. We study the influence of temperature on  $R_{ON}(L_G)$ and  $R_{ON}(L_{GD})$  in **Fig. 7**.  $R_{ON}(L_G)$  has a constant slope while  $R_{ON}(L_{GD})$  has a temperature dependent slope (**Fig. 7b-c**).

Fig. 7. **a)**  $I_D(V_{GS})$  measurements with corresponding transconductance  $G_m(V_{GS})$  curves, for different gate lengths  $L_G$  at 150°C and  $V_{DS}$ =+0.5V. **bc)** Impact of gate length  $L_G$  and  $L_{GD}$  on the On state resistance  $R_{ON}$  (extracted at  $V_{GS}$ =+6V) at 25°C, 75°C and 150°C (slopes =  $R_{sh,channel}$  and  $R_{sh,2DEG}$ , see Fig. 2, Fig. 5).

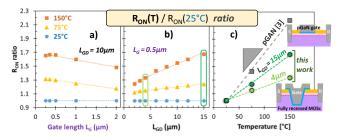

The channel resistance is less sensitive to temperature compared to the 2DEG resistance. **Fig. 8** shows  $R_{ON}(T)/R_{ON}(25^{\circ}C)$  (which is linear with temperature) measured for two  $L_{GD}$  values and a comparison with pGaN data [3-4]. The higher pGaN  $R_{ON}(150^{\circ}C)/R_{ON}(25^{\circ}C)$  ratio value (2.2) is explained by the fact that the major  $R_{ON}$  contribution is the 2DEG (no  $R_{channel}$ , no  $R_{l}$ ) which exhibits a dramatic temperature dependence (2.55 in **Fig. 6b**).

Fig. 8. Impact of gate length  $L_G$  (**a**) and of  $L_{GD}$  (**b**) on the  $R_{ON}$  ratio at 75 and 150°C (relative to 25°C), ie. normalized Ron at 25°C. **c**) Impact of temperature on  $R_{ON}$  ratio (and comparison with pGaN gate).

#### C. Dynamic RON

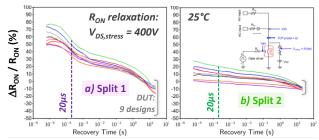

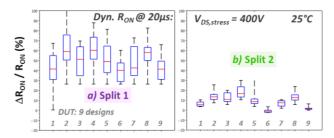

Another aspect in  $R_{ON}$  studies that needs to be considered is current collapse due to stress. That is why we show dynamic  $R_{ON}$ results at room temperature: **Fig. 9** shows  $\Delta R_{ON}/R_{ON}$  as a function of recovery time (after a  $V_{DS} = +400V$  stress) for nine different DUT layout designs (**Fig. 10** at 20µs). We include in these figures an example of comparison between two technological processes: this illustrates that there is a wide process window for performance optimization.

Fig. 9. R<sub>ON</sub> relaxation transient ( $\Delta R_{ON}/R_{ON}$  vs. recovery time, up to 10s) at 25°C for nine layout designs and two technological gate splits (one wafer per split). Insert: Set-up principle. On state conditions: I<sub>D</sub>=0.5A, V<sub>GS</sub>=+6V, pulse time = 175µs; stress: t<sub>stress</sub> = 10s, V<sub>DS</sub> = 400V, V<sub>GS</sub> = -2V.

Fig. 10. Box plots for dynamic  $R_{ON}$  measurements at 25°C for a 20µs recovery time (Fig. 10). Nine different layout designs from two technological gate splits (one wafer per split) are compared (left, right).

#### IV. PACKAGED DEVICES

Once the selected power transistors have been packaged (TO247 as a first test vehicle), we conducted additional static and dynamic electrical tests for 650V applications.

#### A. Blocking mode, dynamic R<sub>ON</sub>, capacitances

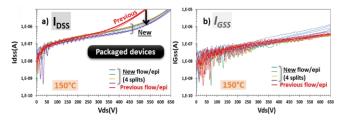

We measured blocking modes characteristics  $I_{DSS}$  and  $I_{GSS}$  at 150°C (**Fig. 11**:  $I_{DSS}$  and  $I_{GSS}$ ) for two versions of the process integration. Note that similar measurements have been conducted at the wafer level, with identical conclusions. The  $I_D$  reduction (for an unmodified  $I_G$ ) indicates that the carrier path of the drain leakage current is vertical. One can note that epi and flow optimizations have enabled to improve performance. Moreover this MOS HEMT technology presents similar  $I_{DSS}$  values to pGaN performance for much lower  $I_{GSS}$  (0.4µA vs. 1mA [3], at  $V_{DS}$ =+600V).

Fig. 11. Blocking mode ( $V_{GS} = -2V$ ,  $V_{DS}$ : 0 to 650V, step 6.5V) measured on packaged past and **new** devices (TO247),  $I_{DSS}$  (left) &  $I_{GSS}$  (right) measurements at 150°C (three devices per split).

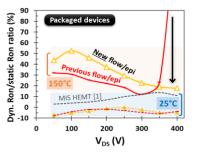

Fig. 12 shows cumulative  $R_{ON}$  dynamic measurements. At 25°C we outperform published MIS HEMT data [1], and we report results also at 150°C (which are rarely presented): the dynamic  $R_{ON}$  change is limited to +18% after cumulative  $V_{DS}$  stress up to +400V for our most recent process integration.

Fig. 12. Cumulative dynamic Ron meas. at 25°C, 150°C for past / new (TO247 packaged) devices ( $V_{GS}$ =-2V,  $V_{DS}$ =50-400V, step +50V, t<sub>stress</sub>=10s).

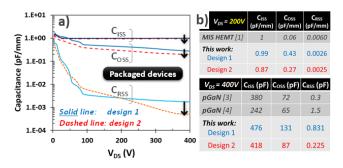

**Figs. 13** shows the three typical capacitances ( $C_{ISS}$ ,  $C_{OSS}$ ,  $C_{RSS}$ ). We point out the fact that layout modification ( $L_G$ , field plates) is a powerful tool to adjust the capacitances (esp.  $C_{RSS}$ ) to dynamic targets.

Fig. 13. a) Device C<sub>ISS</sub>, C<sub>OSS</sub>, C<sub>RSS</sub> capacitances measured on packaged devices (TO247) for two layout configurations at 25°C, freq.=1MHz,  $V_{GS}$ =0V. Design 2 (more aggressive layout) shows strong capacitance reduction. b) Summary tables for capacitances measured at  $V_{DS}$ =+200V and +400V compared to pGaN/MIS HEMT ref.

The C<sub>ISS</sub>/C<sub>RSS</sub> ratio at 400V can thus be maximized for canceling parasitic switch ON of low side transistor in half bridge circuits. This ratio is found to be much higher than the pGaN references [3-4]: 1800 vs. 130-160. C<sub>ISS</sub> corresponds indeed to gate capacitance  $C_{GS}+C_{GD}$  which relates, in our architecture, to the MOS gate dielectric thickness (making this parameter an efficient tuning variable).

#### B. Gate charge, switching results

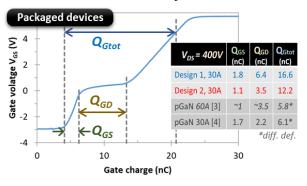

Relatively high  $C_{ISS}$  values implies that a large charge amount is necessary to switch the transistor ON. This effect is visible in **Fig. 14** (Gate charge measurements), and explains why  $Q_{Gtot}$  is ~2 times larger than pGaN references. One can note that further gate optimization can be applied (dielectric thickness increase) to solve this issue. Another benefit of such an optimization is V<sub>th</sub> increase.

Fig. 14. Gate charge at 25°C,  $V_{DS}{=}400V,\,V_{GS}{:}{-}3$  to  ${+}6$  V ( $Q_{Gtot}$  calculation for 4.5 V). Table: mean values for 5 devices and 2 designs (& references).

Switching tests typically used for analyzing losses in half bridge circuits are shown in **Fig. 15a**. Turn-on switching loss energy ( $E_{ON}$ ) is dramatically improved (>63%) with our recent integration scheme (nots shown here). The switching times  $t_{d(on)}$  and  $t_{d(off)}$  are also presented (for two designs) and compared to pGaN references (**Fig. 15b**) showing that fully recessed gate outperforms these commercial devices.

Fig. 15. Switching tests (double pulse 400V, half bridge). **a)** Typical example (design 1,  $I_D$ =8A). **b)** Switching times for the two designs and pGaN references.

#### V. CONCLUSIONS AND PERSPECTIVES

In this work we present an overview of fully recessed gate AlGaN/GaN MOS channel HEMT from process, integration, advanced characterizations (on wafer) to package level (gate charge, switching...). We investigated the RON performance through a wide range of characteristics: i) the R<sub>ON</sub> partitioning enables us to highlight the specific role of 2DEG resistance (at 25 and 150°C); ii) in particular the comparison with pGaN gate architecture shows a better R<sub>ON</sub>(T)/R<sub>ON</sub>(25°C) ratio for MOSc-HEMT, which is critical for power applications. Moreover leakage currents are shown to be largely lower compared to literature: ID (and  $I_G$ ) under blocking mode, and  $I_G$  in conduction mode (this property is due to the high quality of the gate dielectrics). Packaged devices have also been evaluated for dynamic performance. We showed improved switching characteristics (especially  $t_{d(on)}$  and t<sub>d(off)</sub>) compared to pGaN gate devices. All these elements show that MOSc-HEMTs can lead to more efficient and compact power systems.

#### REFERENCES

- P. Moens et al., "An industrial process for 650V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric," 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2014, pp. 374-377, doi: 10.1109/ISPSD.2014.6856054.

- [2] W. Vandendaele et al., "A Novel Insight on Interface Traps Density (Dit) Extraction in GaN-on-Si MOS-c HEMTs," 2020 IEEE International Electron Devices Meeting (IEDM), 2020, pp. 23.5.1-23.5.4, doi: 10.1109/IEDM13553.2020.9371965.

- [3] IGT60R070D1 final data sheet, "600V CoolGaN™ enhancementmode Power Transistor", rev 2.12, 2020-05-29 (www.infineon.com).

- [4] GS66508T data sheet, "Top-side cooled 650 V E-mode GaN transistor", Rev 200402 (www.gansystems.com).

- [5] A. Pérez-Tomás, A. Fontserè, "AlGaN/GaN hybrid MOS-HEMT analytical mobility model", *Solid-State Electronics*, Volume 56, Issue 1, 2011, Pages 201-206, ISSN 0038-1101, doi: 10.1016/ j.sse.2010.11.016.

- [6] X. Zhang et al., "Addressing FinFET metrology challenges in 1× node using tilt-beam critical dimension scanning electron microscope", J. of Micro/Nanolithography, MEMS, and MOEMS, 13(4), 041407 (2014), doi: 10.1117/1.JMM.13.4.041407.

- [7] K. J. Chen et al., "Planar GaN Power Integration The World is Flat," 2020 IEEE International Electron Devices Meeting (IEDM), 2020, pp. 27.1.1-27.1.4, doi: 10.1109/IEDM13553.2020.9372069.

- [8] K. Im et al., "Normally Off GaN MOSFET Based on AlGaN/GaN Heterostructure With Extremely High 2DEG Density Grown on Silicon Substrate," in *IEEE Electron Device Letters*, vol. 31, no. 3, pp. 192-194, March 2010, doi: 10.1109/LED.2009.2039024.

- [9] Hironobu Miyamoto et al., "Threshold voltage control of nonrecessed GaN MOS HEMTs and recessed GaN MOS FETs by Al<sub>x</sub>Ga<sub>1-x</sub>N back barrier", 2020 Japanese Journal of Applied Physics 59 044002, doi: 10.35848/1347-4065/ab778a.

- [10] S. Kumar, S. Vura, S.B. Dolmanan, S. Tripathy, R. Muralidharan and D.N. Nath (2020), "Deep Submicron Normally Off AlGaN/GaN MOSFET on Silicon with VTH > 5V and On-Current > 0.5 A mm<sup>-1</sup>", *Phys. Status Solidi A*, 217: 1900709. https://doi.org/10.1002 /pssa.201900709

- [11] F. Roccaforte, G. Greco, P. Fiorenza and F. Iucolano, "An overview of normally-off GaN-based high electron mobility transistors", *Materials*, vol. 12, no. 10, pp. 1599, May 2019, doi: 10.3390/ma12101599.