# A 7.4 $\mu$ W and 860 $\mu$ m<sup>2</sup> per channel cryo-CMOS IC for 70-channel frequency-multiplexed $\mu$ s-readout of semiconductor qubits

Quentin Schmidt, Brian Martinez, Thomas Houriez, Baptiste Jadot, Aloysius Jansen, Xavier Jehl, Tristan Meunier, Gaël Pillonnet, Gérard Billiot, Adrien Morel, et al.

### ▶ To cite this version:

Quentin Schmidt, Brian Martinez, Thomas Houriez, Baptiste Jadot, Aloysius Jansen, et al.. A  $7.4\mu W$  and  $860\mu m^2$  per channel cryo-CMOS IC for 70-channel frequency-multiplexed  $\mu$ s-readout of semiconductor qubits. Custom Integrated Circuit Conference 2024, IEEE, Apr 2024, Denver, United States. pp.11-6, 10.1109/CICC60959.2024.10529081. cea-04563150

# HAL Id: cea-04563150 https://cea.hal.science/cea-04563150

Submitted on 29 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**IEEE CICC 2024**

#### A 7.4µW and 860µm<sup>2</sup> per channel cryo-CMOS IC for 70channel frequency-multiplexed us-readout semiconductor qubits

Quentin Schmidt<sup>1</sup>, Brian Martinez<sup>1</sup>, Thomas Houriez<sup>1</sup>, Baptiste Jadot<sup>1</sup>, Aloysius Jansen<sup>2</sup>, Xavier Jehl<sup>2</sup>, Tristan Meunier<sup>3,4</sup>, Gaël Pillonnet<sup>1</sup>, Gérard Billiot<sup>1</sup>, Adrien Morel<sup>6</sup>, Yvain Thonnart<sup>5</sup>, Franck Badets1

<sup>1</sup>Univ. Grenoble Alpes, CEA, Leti, <sup>2</sup>Univ. Grenoble Alpes, CEA, PHELIQS, <sup>3</sup>Quobly, <sup>4</sup>Univ. Grenoble Alpes, CNRS, Institut Neel, <sup>5</sup>Univ. Grenoble Alpes, CEA, List, F-38000 Grenoble, France, <sup>6</sup>SYMME, Univ. Savoie Mont Blanc, Annecy, France

Large-scale quantum computing holds promise for exponentially faster computation speed to address currently unsolvable problems. Nevertheless, biasing, driving and reading numerous physical qubits operating at cryogenic temperature remains an on-going challenge. In particular, the integration of cryogenic control and readout ICs appears mandatory to overcome the wiring bottleneck [1, 2, 3]. In this regard, the promising higher operating temperature (up to 1K) of silicon semiconductor qubits offers a more substantial cryogenic power budget, which could enable addressing larger qubit arrays with integrated cryogenic CMOS electronics. In the context of 100,000 qubits at 1K, the maximum power consumption allowed by cooling capability is about 1W within a compact footprint of just a few defining targets of <10µW/qubit consumption and <0.01mm²/qubit footprint. Focusing on the readout IC, the semiconductor-qubit coherence time also imposes a typical <100µs readout time, while requiring a Bit Error Rate (BER) below 10<sup>-3</sup>.

Reflectometry, in conjunction with a frequency-division multiplexing (FDM) technique, has been proposed as a potential solution [1, 2, 3]. However, the footprint of associated passive inductors and/or the need of intermediary frequencies (IF) remain impractical for addressing large-scale arrays of qubits. Additionally, the resonator quality factor introduces a strong tradeoff between spectral selection and reading time (Ti). To overcome these issues, charge-based readouts using cryogenic transimpedance amplifiers (TIA) or current integrators were proposed by [4, 5]. Nevertheless, existing implementations still face limitations in terms of gain [4] (<80dB.Ω), or are not compatible with FDM [5]. Moreover, they offer no answer to solve the wiring bottleneck issue.

Taking inspiration from [6], this paper introduces a tunable FDMcapable cryogenic capacitive feedback TIA (CTIA) in FDSOI 28nm CMOS technology for reading simultaneously up to 70 channels in a charge-readout scheme with an external direct IQ conversion.

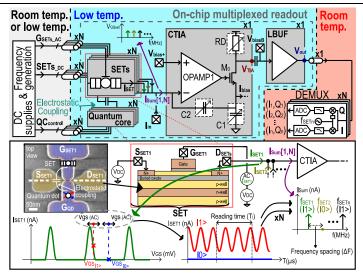

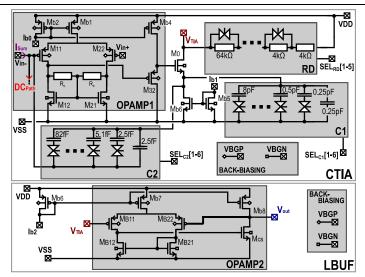

Figure 1 depicts the circuit architecture of the proposed CTIA for FDM charge readout. The MHz range CTIA input current is either coming from co-integrated single electron transistors (SET) or from emulated current stimuli (lin). In a SET configuration, the modulation of the SET gates at different frequencies, with a frequency separation  $(\Delta F)$ , results in On-Off Keying (OOK) sub-nA signals depending on the electrostatic charge environment reflecting the qubit state information. The sum of all OOK current signals (ISUM) is amplified and converted into a voltage (VTIA) through the CTIA. Then, the voltage is sent to RT via an integrated line buffer (LBUF). At RT, digitization and demodulation of N multiplexed frequencies yield N (I, Q) components representing simultaneously the N quantum states.

Figure 2 presents the schematics of the proposed tunable CTIA and LBUF. In contrast to [6], OPAMP1 is a two-stage opamp. The V<sub>CM</sub> bias is provided by current mirrors, which also provide a DC path for the input current. As capacitive feedback does not set the DC feedback, a local common mode feedback is introduced. To drive the large M0 gate capacitance without instability, the OPAMP1 second stage is designed as a common drain stage. LBUF, on the other hand, is a two-stage opamp source follower responsible for driving the capacitance of the output wiring from cryogenic temperature to RT (typically ~300pF). Rather than relying on conventional temperaturedependent passive Miller compensation that could lead to instabilities at cryogenic temperature, LBUF has been designed to use the output wire capacitance itself as a compensation.

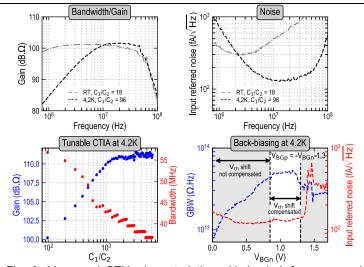

Figure 3 shows the CTIA performances at 4.2K measured with a 1nA input current source and facing a 40fF parasitic input capacitance. By adjusting the tunable passives elements (C1, C2, RD) to obtain a gain of  $101dB.\Omega$ , a bandwidth of 50MHz and a noise level of 130fA/√Hz are achieved. The power consumptions of the CTIA and LBUF are 180μW and 330μW respectively. As depicted, tuning C1 and C2 allows a tradeoff between gain and bandwidth without affecting the CTIA power consumption, illustrating its flexibility for

Die micrograph.

scaling and its adaptability to specific SET characteristics. RD and biasing currents are used to account for thermal effects. Besides, FDSOI allows independent NMOS and PMOS back-gate biasing (VBGN=1V, VBGP=-2.3V) in order to compensate for the temperature shifts of V<sub>TH</sub>, ensuring that the targeted operating point is maintained. Unlike prior works on cryogenic integrated charge readout architectures (Fig. 5) our CTIA exhibits, >100dB.Ω gain, and <1mW power consumption, while reaching >10MHz bandwidth and achieving comparable noise performances. Thereby it meets all the necessary specifications for a FDM scalable charge-based readout.

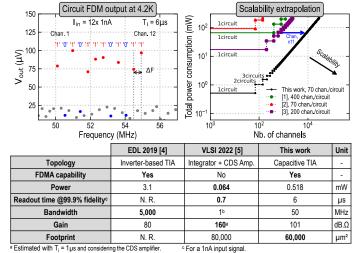

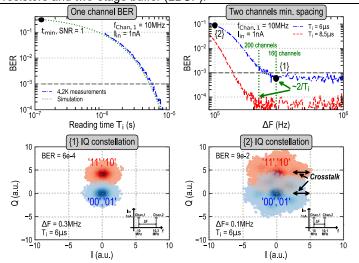

Figure 4 illustrates the readout performances achieved with our proposed FDM readout. Given our noise level, when reading a single 1nA signal at 10 MHz, the required reading times are respectively 6µs and 8.5µs to reach a BER of 10<sup>-3</sup> and of 10<sup>-4</sup>. The reading time to reach a signal-to-noise ratio of 1 (tmin) has been extrapolated to t<sub>min</sub>=125ns from our 4.2K measurements, which is 16x shorter than [1]. To study the crosstalk between channels, we introduced a second channel and measured the reached BER depending on the frequency separation  $\Delta F$  between both, for a given reading time. For ΔF>2/T<sub>i</sub>, crosstalk becomes negligible compared to the noise level and the BER decreases down to the single-channel case. While  $\Delta F=1/T_i$  could be reached according to the orthogonal FDM (OFDM) principle, we were limited by our RT demultiplexing instruments baseband filter. Two IQ constellations {1} and {2} are shown for two values of frequency spacing, highlighting the crosstalk for ΔF below the second orthogonal frequency. Our readout chain demonstrates operation near the OFDM limit, which is not attained by [1, 2, 3] due to their limited resonators Q factors. With a bandwidth of 50MHz and a reading time of 6µs to achieve a 99.9% fidelity, the proposed CTIA could read 166 channels. Our circuit is no longer limited by frequency separation and in practice the I<sub>IN</sub>1dB=70nA compression point at 1dB achieved by LBUF yields 70 channels. Fig. 5 presents a frequency distribution example for an FDM readout of 12 channels with a 438kHz channel spacing (chosen to prevent FFT aliasing).

Figure 6 compares our alternative multiplexed readout with state of the art cryo-CMOS reflectometry. A first-order extrapolation of power consumption and number of channels yields a power efficiency of 7.4µW/channel, which is a 11x improvement compared to [1, 2, 3], as illustrated in Fig. 5. A footprint efficiency of 860µm²/channel has been achieved, which is a 2.3x improvement. Furthermore, our circuit eliminates bulky resonators, which constitutes a major advantage for scalable qubit readout. Our readout circuit demonstrates the capability to simultaneously read 70 channels within the aforementioned budgets of <10µW/qubit power consumption and <0.01mm²/qubit footprint, which represent a significant advancement for large-scale readout of semiconductor qubits.

## Acknowledgement:

This work is supported by the French National Research Agency under the programme "France 2030" (PEPR PRESQUILE - ANR-22-PETQ-0002). Electronic PCBs were supplied by CEA test engineers as part of the European Qu-test project.

#### References:

- [1] B. Prabowo et al., "13.3 A 6-to-8GHz 0.17mW/Qubit Cryo-CMOS Receiver for Multiple Spin Qubit Readout in 40nm CMOS Technology," ISSCC, 2021.

- [2] A. Ruffino et al., "13.2 A Fully-Integrated 40-nm 5-6.5 GHz Cryo-CMOS System-on-Chip with I/Q Receiver and Frequency Synthesizer for Scalable Multiplexed Readout of Quantum Dots," ISSCC, 2021.

- [3] A. Nagulu et al., "Sub-mW/qubit 5.2-7.2GHz 65nm Cryo-CMOS RX for Scalable Quantum Computing Applications," CICC, 2023.

[4] S. Bonen *et al.*, "Cryogenic Characterization of 22-nm FDSOI CMOS

- Technology for Quantum Computing ICs," EDL, 2019.

- [5] H. Fuketa et al., "A Cryogenic CMOS Current Comparator for Spin Qubit Readout Achieving Fast Readout Time and High Current Resolution," VLSI, 2022. [6] B. Razavi, "A 622 Mb/s 4.5 pA/√Hz CMOS transimpedance amplifier [for optical receiver frontend]," ISSCC, 2000.

Fig. 1. Block diagram of the proposed frequency multiplexed readout, illustrating the temperature repartition of the system and the signal generation using charge sensing and SET.

Fig. 3. Measured CTIA characteristics with  $I_{\rm in}$ =1nA for room and cryogenic temperature (RT & 4.2K): gain and noise. Gain and bandwidth depending on programmable capacitors. Effect of the back-biasing on the GBW and input referred noise.

Fig. 5. Measured output voltage of the circuit at 4.2K and predicted evolution of the addressable number of channels depending on the available power consumption for readout. Comparison table of state of the art circuits dedicated to charge readout of quantum devices.

Fig. 2. Transistor level schematics of the proposed main blocks: capacitive feedback TIA (CTIA) with programmable capacitors and resistors and two-stage buffer (LBUF).

Fig. 4. Bit Error Rate (BER) measured at 4.2K depending on the reading time ( $T_i$ ) and the frequency spacing ( $\Delta F$ ). IQ constellations of the output states for 2 values of frequency spacing with 2 channels, showing the effect of crosstalk for small  $\Delta F$ .

|                                         | ISSCC 2021 [1]         | ISSCC 2021 [2]         | CICC 2023 [3]          | This work        | Unit   |

|-----------------------------------------|------------------------|------------------------|------------------------|------------------|--------|

| Reading type                            | Reflectometry          | Reflectometry          | Reflectometry          | Charge readout   | -      |

| Temperature                             | 4.2                    | 3.5                    | 4                      | 4.2              | К      |

| Off-chip components                     | Directionnal           | Directionnal           | Directionnal           | No               | -      |

| at cryogenic temp.                      | coupler, LNA           | coupler                | coupler                |                  |        |

| Architecture                            | Intermediate IF I/Q    | Intermediate IF I/Q    | Intermediate IF I/Q    | Direct I/Q       | -      |

| Footprint                               | 0.68c                  | 2.10 <sup>c,e,f</sup>  | 0.81°                  | 0.06             | mm²    |

| Power consumption                       | 66.0                   | 92°                    | 17.1                   | 0.518            | mW     |

| Bandwidth                               | 2,000                  | 1,400                  | 2,000                  | 50               | MHz    |

| Channel frequency spacing               | 5                      | 10                     | 10                     | 0.3              | MHz    |

| t <sub>min</sub> b                      | 1.96                   | N. R.                  | N. R.                  | 0.125            | μs     |

| P1dB / I <sub>IN</sub> 1dB <sup>d</sup> | -58.4 / -              | -85 / -                | -81 / -                | - / 70           | dBm/nA |

| Nb. of channels<br>limiting factor      | Resonators Q<br>factor | Resonators Q<br>factor | Resonators Q<br>factor | Buffer linearity | -      |

| Channels/circuit                        | 400                    | 70                     | 200                    | 70 / 166a        | -      |

| Power/channel                           | 0.16                   | 1.31                   | 0.085                  | 0.0074           | mW     |

| Footprint/channel                       |                        | 30,000°+Resonator      | 4,050°+Resonator       | 860              | μm²    |

<sup>&</sup>lt;sup>a</sup> Without considering the I<sub>IN</sub>1dB limitation.

f Estimated from chip micrograph.

Fig. 6. Comparison table of state of the art readout circuits for multiplexed-oriented qubit readout at cryogenic temperature.

$<sup>^{\</sup>rm b}$  With  ${\rm t_{min}}$  the required reading time to reach SNR = 1.

c Reported data that doesn't consider passive resonator footprints and discrete cryogenic electronics

d I<sub>IN</sub>1dB the maximal input current for a 1dB gain loss.

e Excluding on-chip signal generation (VCO, PLL).