## Processing and electrical characterization of SiC-on-Insulator structures

Guillaume Gelineau, Cédric Masante, Emmanuel Rolland, Sophie Barbet, Lucie Corbin, Agathe Andre, Loïc Turchetti, Séverin Rouchier, Alexandre Moulin, Mathieu Delcroix, et al.

## ▶ To cite this version:

Guillaume Gelineau, Cédric Masante, Emmanuel Rolland, Sophie Barbet, Lucie Corbin, et al.. Processing and electrical characterization of SiC-on-Insulator structures. ICSCRM 2023 - the International Conference on Silicon Carbide and Related Materials, Sep 2023, Sorrente, Italy. cea-04557058

## HAL Id: cea-04557058 https://cea.hal.science/cea-04557058

Submitted on 24 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Processing and electrical characterization of SiC-on-Insulator structures

<u>G. Gelineau</u><sup>1)</sup>, C. Masante<sup>1)</sup>, E. Rolland<sup>1)</sup>, S. Barbet<sup>1)</sup>, L. Corbin<sup>1)</sup>, A. André<sup>1)</sup>, L. Turchetti<sup>2)</sup>, S. Rouchier<sup>2)</sup>, A. Moulin<sup>1)</sup>, M. Delcroix<sup>1)</sup>, N. Troutot<sup>1)</sup>, S. Huet<sup>1)</sup>, V. Prudkovskiy<sup>1)</sup>, K Mony<sup>3)</sup> and J. Widiez<sup>1)</sup>

<sup>1)</sup> Univ. Grenoble Alpes, CEA, LETI, 17 avenue des Martyrs, 38054 Grenoble, France

<sup>2)</sup> SOITEC, Parc technologique des fontaines, 38190 Bernin, France.

<sup>3)</sup> Univ. Grenoble Alpes, CEA, Grenoble INP, IRIG, PHELIQS, 17 avenue des Martyrs, 38054 Grenoble, France e-mail: guillaume.gelineau@cea.fr

Ion slicing technologies are becoming increasingly popular among silicon carbide (SiC) processing techniques, whether for manufacturing substrates for power electronics [1], [2] or integration platforms for optical devices [3]. For either of these applications, one as to ensure the excellent quality of the transferred layer. In this extent, silicon carbide-on-insulator (SICOI) structures can be of great interest in order to probe the properties of the transferred layer alone. The electrically insulating oxide layer between the receiver substrate and the transferred layer allows one to measure the electrical properties of the transferred layer allows one to measure the electrical properties of the transferred layer allows one to measure the fabrication step [4]. We thus report the fabrication process of such a SICOI structure, using a monocrystalline 4H-SiC wafer as the handle substrate. The choice of the later minimizes the difference of the thermal dilatation coefficients of the transferred layer and the substrate, as compared to the use of a Si handle [5], as well as allowing to benefit of a higher melting point. Doing so enables to access higher annealing temperatures, and to understand more acutely the effects of such manufacturing processes.

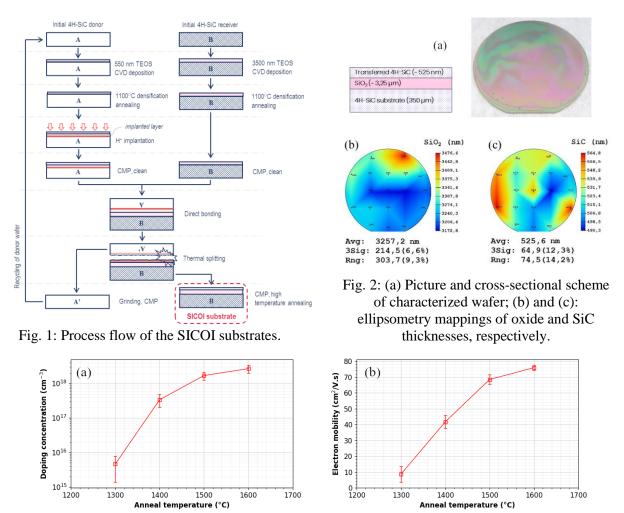

The substrates were processed as described on the Fig. 1. Layers of tetraethoxysilane (TEOS) were deposited on both the donor (550 nm) and the receiver (3500 nm) substrates (both of  $4.10^{18}$  cm<sup>-3</sup> n-doped bulk 4H-SiC), before dehydrogenation at 1100°C (1 hr) under a N<sub>2</sub> atmosphere. The donor wafer was then H<sup>+</sup>-implanted at room temperature, 160 keV and at a dose of 5,5.10<sup>16</sup> at.cm<sup>-2</sup>. The two substrates were directly bonded after cleaning and polishing steps. A subsequent thermal treatment of 950°C during 1 hr was then applied in order to split the implanted (donor) wafer at the maximum hydrogen concentration depth (i.e. around 700 nm). The SICOI substrates are eventually obtained after 1- a polishing, and 2- a final annealing step (which temperature ranges between 1200°C and 1600°C) – benefitting both the bonding strength and the transferred layer crystal quality. The thicknesses of the oxide and transferred SiC layers of the resulting substrates were found to be of 3.25 µm and 525 nm, respectively, with  $\pm 9.3$  % and  $\pm 14.2$  % variation over the entire wafer surface (see Fig. 2).

The Fig. 3 shows the doping level and the electron mobility inferred from Hall measurements. Both are found to be beneficially affected by a higher annealing temperatures, proof of a progressive healing of the electrical properties of the transferred material. After 1600°C anneal, one can even assess the recovery of a doping level and of an electron mobility close to those of the initial donor (3.10<sup>18</sup> cm<sup>-3</sup> and 76 cm<sup>2</sup>/V.s, respectively). The TLM I-V measurements were carried out at several temperatures, ranging from RT to 200°C. The decrease of the electrical resistivity inferred from these measurements with increasing measuring temperature, shown on Fig. 4, indicates that electrical conduction mechanisms are subjected to ionization processes, which energies depend on the final annealing temperature. One can then calculate electrical compensation ratios for each one of these samples. Those we determine here range from 10 % (after 1200°C anneal) to 0 % (1400°C and over).

SICOI substrates can thus be used as a tool for probing the electrical properties of a thin 4H-SiC layer transferred using an ion slicing technology. Hall and TLM measurement show an evolution of these properties with increasing annealing temperature: reduced resistivity, higher doping activation and higher electron mobility. Further measures of transistor effect and photoluminescence will now be carried out to highlight the presence of any depletion layer or any deep level defects inside the material.

- [1] S. Rouchier, et al., Trans Tech Publications, vol. 1062, pp. 131–135, 2021.

- [2] K. Imaoka *et al.*, US patent 9,761,479 B2, 2017.

- [3] A. Yi et al., Optical Materials, vol. 107, p. 109990, 2020.

- [4] X. Zhang et al., Nuc. Inst. Methods Phys. Res. B, vol. 436, pp. 107–111, 2018.

- [5] E. Hugonnard-Bruyère, et al., Mat. Sci. Eng.: B, vol. 61–62, pp. 382–388, 1999.

Fig. 3: Hall doping level (a) and electron mobility (b) measured at room temperature as a function of the annealing temperature.

Fig. 4: Transferred layer resistivity values extracted from TLM measurements as a function of the measuring temperature for samples annealed between 1200°C and 1600°C.