# Disruptive approaches towards Energy Efficient VLSI Technologies

Olivier Faynot, Sylvain Barraud, Theophile Dubreuil, Elisa Vianello, Emmanuel Oilier, Denis Dutoit, François Andrieu, Fabien Clermidy, Julien Arcamone

### ▶ To cite this version:

Olivier Faynot, Sylvain Barraud, Theophile Dubreuil, Elisa Vianello, Emmanuel Oilier, et al.. Disruptive approaches towards Energy Efficient VLSI Technologies. VLSI-TSA/VLSI-DAT 2023 - IEEE International VLSI Symposium on Technology, Systems and Applications, Apr 2023, HsinChu, Taiwan. pp.1-2, 10.1109/VLSI-TSA/VLSI-DAT57221.2023.10134262. cea-04553118

## HAL Id: cea-04553118 https://cea.hal.science/cea-04553118

Submitted on 19 Apr2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Olivier Faynot<sup>1</sup>, Sylvain Barraud<sup>1</sup>, Theophile Dubreuil<sup>1</sup>, Elisa Vianello<sup>1</sup>, Emmanuel Ollier<sup>1</sup>, Denis Dutoit<sup>2</sup>, François Andrieu<sup>1</sup>, Fabien Clermidy<sup>2</sup>, Julien Arcamone<sup>1</sup>

> <sup>1</sup> CEA-Leti, <sup>2</sup> CEA-List , University Grenoble Alps, 17 rue des Martyrs, 38054 Grenoble Cedex, France

> > E-mail: <u>olivier.faynot@cea.fr</u>

2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT) | 979-8-3503-3416-6/23/\$31.00 ©2023 IEE | DOI: 10.1109/VLSI-TSA/VLSI-DAT57221.2023.10134262

Abstract—Nowadays, the data deluge related to data generation, transfer, compute and storage, induces a huge increase of power consumption related to the usage of integrated circuits. New technologies and concepts are necessary to overcome the issue. This paper will give an overview all the main ongoing developments that will significantly improve the Power efficiency of Integrated Circuits. Disruptive computing, such as Quantum or In Memory Computing are well known to provide significant improvement. Novel Non Volatile Memories, coupled with Neuromorphic architectures can also be an enabler of power efficient electronic. As data transfer is the main source of Power consumption, 3D integrations can enable chiplet approaches that reduce the length of interconnects.

#### I. INTRODUCTION

World's digitalization induces a tremendous increase of data generation, close to 500 Zetabyte by 2030. This data deluge leads to a dramatic increase of energy consumption, not sustainable on a medium term. Technological breakthrough must be developed in order to improve by a factor of at least 1000, the Power efficiency of electronic devices. Since many years, CMOS scaling was able to reduce the power consumption when switching from the previous node to the next one. This was well known as the Moore's law. Today, with the huge increase of IC's usage, disruptive approaches are mandatory in order to reduce the energy consumption of semi-conductors.

#### II. CMOS OPTIONS

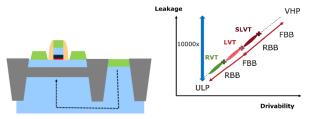

Technology scaling, following Moore's law has always been the most efficient way to reduce the Power consumption from one node to another. An alternative approach appeared below 28nm, with the so-called FD-SOI technology. Besides key advantages related to its lower parasitics and outstanding RF performance for a Silicon based platform, this technology offers a key feature to circuit designers: the Back Bias effect. This effect was disappearing in planar Bulk technologies and does not exist in FinFET technology. On the contrary, this effect exists and is very efficient on FD-SOI technology. Such effect allows to significantly modulate the power consumption of integrated circuits, as illustrated in Fig.1.

Fig. 1 : Back Biasing effect on planar FD-SOI technology

Such effect allows a significant improvement of the tradeoff between operation frequency and Power consumption, with up to 450% frequency improvement demonstrated on Cortex M4F [1].

#### **III. DISRUPTIVE COMPUTING**

#### A. Bio inspired resource-limited Edge AI hardware

As AI becomes increasingly integrated into our daily lives, there is a crucial need to address its energy consumption and storage requirements. Edge computing offers a potential solution by processing data in real-time at the source where sensors are located. However, this requires compact and lowpower computer systems with low latency to be effective.

To meet these requirements, hybrid resistive memories-Complementary Metal-Oxide Semiconductor (CMOS) neuromorphic architectures with their in-memory eventdriven computing capabilities provide an ideal hardware substrate. To showcase the full potential of these systems, we recently designed and fabricated an event-driven objectlocalization system based on the neuroanatomy of barn owls. Our system uses state-of-the-art piezoelectric ultrasound transducer sensors and a neuromorphic computational map based on resistive memories [2]. We have focused on the task of acoustic-based object localization. In particular, the owl's localization system encodes the time-of-flight of sound waves coming from prey to calculate its position. Our system implements a similar approach, using a single emitting piezoelectric microelectromechanical systems (pMUT) membrane operating at 111.9 kHz and two reception pMUT membranes to emulate the owl's ears. The system also includes a neuromorphic computational map that was fabricated by co-integrating a 130-nm CMOS processor with hafnium-dioxide resistive memory devices. The results of our experiments have revealed the potential of our approach, with orders of magnitude greater energy efficiency than a microcontroller performing the same task. This work highlights the promise of edge computing and neuromorphic architectures in meeting the energy consumption and storage requirements of AI systems.

Fig. 2: Object localization system in barn owls and the proposed bio-inspired technology

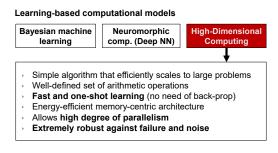

#### B. Memory-centric High-Dimensional computing

Among alternative brain-inspired computing paradigm, High-Dimensional Computing (HDC), based on random distributed representation, offers a promising way for learning and classification tasks. Unlike conventional computing, HDC computes with (pseudo)-random hypervectors (HVs) of Ddimension. This implies significant advantages (Fig. 3): a simple algorithm with a well-defined set of arithmetic operations (Multiplication /Addition /Permutation), with fast and single-pass learning that can benefit from a memorycentric architecture (highly energy-efficient and fast thanks to a high degree of parallelism).

Fig. 3: Main characteristics of HDC algorithm vs other learning-based computational models.

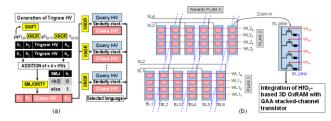

The first hardware implementations of HDC based on emerging non-volatile memory provided a good accuracy of recognition with a promising energy efficiency, even if computing was partially produced within peripheral circuitry [3]. More recently, other 3D RRAM architectures have been proposed to implement the Multiply-Add-Permute (MAP) operations within the memory itself. Novel 3D RRAM architecture, which benefits from the high density of vertically stacked-channel transistors integrates the RRAM cell directly inside the drain contact of selector [4]. These highly compact 1T1R memory cells can be exploited to perform stateful inmemory MAP operations with a high level of parallelism (Fig. 4).

Fig. 4: (a) Overview of HDC algorithm for language recognition with the XNOR/MAJ/SHIFT operations, (b) Electrical schematic of a 3D 1T1R architecture based on the co-integration of HfO2 OxRAM and GAA stacked-channel transistor.

### IV. 3D AND CHIPLET APPROACH

It is now well established that the combination of different kinds of integrated circuits by 2.5 and 3D technologies is a way to combine the best of different technologies and the miniaturization to provide higher performance, flexibility and modularity with drastic energy efficiency benefits. Our current developments are focussed on developing i) the chiplet approach (Fig. 5) for high performance computing and Edge Artificial Intelligence, ii) multi-level architectures for image sensors and displays. Those developments are enabled by advanced 3D technological bricks (high density through silicon vias, wafer-to-wafer and die-to-wafer direct hybrid bonding, 3D sequencial integration...) as illustrated on Fig.6.

*Fig. 5: INTACT integrated circuit [5] with 6 chiplets stacked on an active interposer.*

3D pitch reduction for bandwidth increase

Fig. 6: Technological roadmap around 3D integration.

#### ACKNOWLEDGMENT

The authors would like to thank CEA-Leti facilities for the lot processing. This work was partially supported by the French Public Authorities within the frame of the Nano2022 (IPCEI Microelectronics) project and by Nanoelec IRT program.

#### REFERENCES

- Yasser Moursy et al, 'A 0.021mm2 PVT-Aware Digital-Flow-Compatible Adaptive Back-Biasing Regulator with Scalable Drivers Achieving 450% Frequency Boosting and 30% Power Reduction in 22nm FDSOI Technology, ISSCC 2021.

- [2] F. Moro, E. Hardy, B. Fain, T. Dalgaty, P. Clémencon, A. De Prà, E. Esmanhotto, N. Castellani, F. Blard, F. Gardien, T. Masquida, F. Rummens, D. Esseni, J. Casas, G. Indiveri, M. Payvand, E. Vianello, "Neuromorphic object localization using resistive memories and ultrasonic transducers", Nature communications, vol.13, June 2022.

- [3] G. Karunaratne *et al.*, Nat Electron **3**, 327–337 (2020). <u>https://doi.org/10.1038/s41928-020-0410-3</u>.

- [4] T. Dubreuil et al., 2023 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Hsinchu, Taiwan, 2023..

- [5] Pascal Vivet et al, "220GOPS 96-Core Processor with 6 Chiplets 3D-Stacked on an Active Interposer Offering 0.6ns/mm Latency, 3Tb/s/mm2 Inter-Chiplet Interconnects and 156mW/mm2 @ 82%-Peak-Efficiency DC-DC Converters," ISSCC 2020.