## Doped channel SOI pMOS TCAD description including floating body effects

Joris Lacord, Ayoub Boutayeb, Daphnée Bosch, Obaid-Allah Adami, Pierre Lhéritier, Fabienne Ponthenier, François Guyader, Sylvain Joblot

#### ▶ To cite this version:

Joris Lacord, Ayoub Boutayeb, Daphnée Bosch, Obaid-Allah Adami, Pierre Lhéritier, et al.. Doped channel SOI pMOS TCAD description including floating body effects. SISPAD 2023 - Conference on Simulation of Semiconductor Processes and Devices, Sep 2023, kobe, Japan. pp.69-72, 10.23919/SIS-PAD57422.2023.10319562. cea-04541952

### HAL Id: cea-04541952 https://cea.hal.science/cea-04541952

Submitted on 11 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Doped Channel SOI pMOS TCAD Description Including Floating Body Effects

J. Lacord, A. Boutayeb, D. Bosch, O. Adami, P. Lhéritier, F. Ponthenier *CEA-Leti, Univ. Grenoble Alpes* Grenoble, France joris.lacord@cea.fr

A. Boutayeb, F. Guyader, S. Joblot STMicroelectronics Crolles, France A. Boutayeb

Univ. Grenoble Alpes, IMEP-LAHC,

Grenoble INP

Grenoble. France

Abstract— In this work, we propose to investigate Silicon-on-Insulator (SOI) pMOS behavior modulation due to channel doping and its TCAD description. We first demonstrate channel doping variation due to the diffusion through the BOX and consumption during gate oxide formation. As the channel thickness is not so thin (Tsi=22nm), channel doping variation leads to different device operation from Fully Depleted (FD) to Partially Depleted (PD), going through an "in between" regime where Floating Body (FB) effects occurs. We finally propose TCAD methodology to account for channel doping variation in SOI pMOS.

#### Keywords—SOI; TCAD; Floating Body Effects

#### I. INTRODUCTION

SOI devices are studied since decades for many applications: Partially-Depleted SOI devices with thick silicon film (>60nm) are used for RF-SOI applications [1] while Fully-Depleted-SOI devices with thin SOI film (<10nm) are used for RF, digital and more Moore applications [2-4]. Floating Body (FB) effects are known to occur in PD-SOI devices [5-6] and can be canceled by body contact [7-8] while FD-SOI device are immune to FB effects thanks to the thin SOI film. Recently, SOI device on thin BOX with relatively thin film (22nm) have been proposed to fulfill imager application requirements with 3D sequential integration [9], where SOI film doping can be used for Vt centering. The objective of this paper is to determine the operation of such a SOI device and to propose the corresponding TCAD description, accounting for the SOI film doping.

#### II. DEVICE & TCAD DESCRIPTION

SOI pMOS is defined to fulfill imager applications requirements ( $V_{DD}$ =2.5V) [9]: SiO2-polysilicon gate, 22 nm

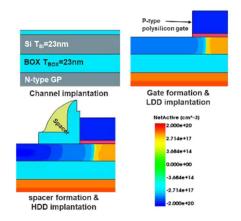

Fig. 2 : pMOS structure snapshots taken during TCAD process simulation

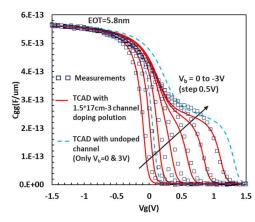

Fig. 1 :  $(C_{GG}-V_G)$  for  $V_b = 0$  to -3V from measurement and TCAD before and after tuning.

silicon film thickness (TsI), 25 nm buried oxide thickness (T<sub>BOX</sub>), 5 nm SiO2 gate oxide grown by Rapid Thermal Oxidation (RTO) and a highly in-situ doped N-type Ground Plane (GP, Phosphorus, 2.10<sup>20</sup>cm<sup>-3</sup>). To build high V<sub>T</sub> devices, channel doping is performed with BF2 implantation for large dose variation (0 to 6.10<sup>13</sup>cm<sup>-2</sup>) and gate length L varies from 0.15 to 1 µm. TCAD is performed through process and device simulations. The complete process is simulated (Fig.1): channel implantation, gate formation (RTO and Ptype polysilicon), LDD implantation, spacer formation and HDD implantation. Device simulations are then performed with Poisson equation, drift-diffusion, SRH recombination ThinLayer(IALmob) including and model HighFieldSaturation.

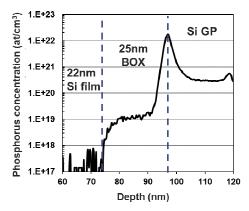

Fig. 3 : SIMS characteristic in the SOI substrate highlighting the phosphorus diffusion from the GP to the Si film.

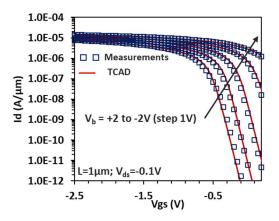

Fig. 4 : L=1 $\mu$ m pMOS I<sub>d</sub>-V<sub>g</sub> for V<sub>b</sub> variation at V<sub>d</sub>=-0.1V from TCAD and measurement.

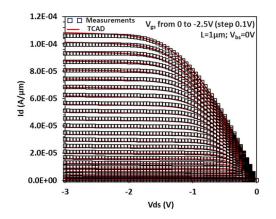

Fig. 5 : L=1 $\mu$ m pMOS I<sub>d</sub>-V<sub>d</sub> for V<sub>g</sub> variation from 0 to -2.5V at V<sub>b</sub>=0V from TCAD and measurement

#### III. UNDOPED CHANNEL SOI PMOS TCAD VALIDATION

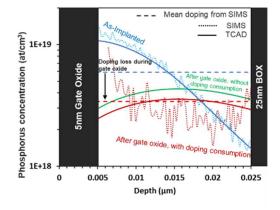

We first focus on long channel (L=1 $\mu$ m) undoped channel SOI pMOS. Gate capacitance with gate voltage characteristic (Cgg-Vg, Fig.2) highlight that strong inversion regime is well described but there is lower TCAD threshold voltage V<sub>T</sub> at V<sub>b</sub>=0 & 3V than measurement (dashed blue line). To increase TCAD V<sub>T</sub>, higher N-type channel doping is necessary and cannot come from the implantation steps, which are all P-type. From Secondary Ion Mass Spectrometry (SIMS) measurement performed on SOI substrate (Fig.3), we

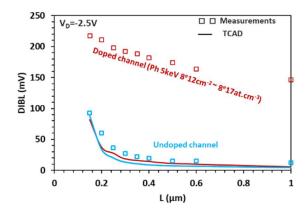

Fig. 7 : DIBL variation with gate length L for doped and undoped channel from TCAD and measurement

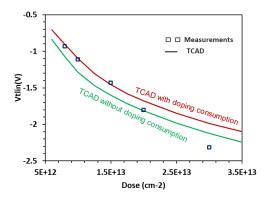

Fig. 8 : L=1  $\mu m \ V_{\text{tiin}}$  variation with Phosphorus implantation dose from measurement and TCAD

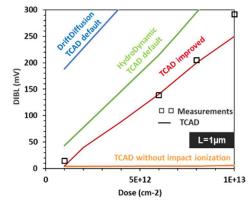

demonstrate that  $1{\sim}4e17cm^{-3}$  Phosphorus diffused from the GP to the channel through the 25nm thick BOX. It is included in TCAD and  $C_{gg}$ - $V_g$  for  $V_b$  variation is reproduced (red line on Fig.2), as well as long channel  $I_d$ - $V_g$  at  $V_d$ =-0.1V for  $V_b$  variation &  $I_d$ - $V_d$  at  $V_b$ =0V (Fig 4,5). The short channel TCAD description is then validated with DIBL variation versus gate length (Fig.6). An important DIBL degradation appears for doped channel, even for long gate and is not observed in TCAD.

#### IV. DOPED CHANNEL SOI PMOS TCAD DESCRIPTION

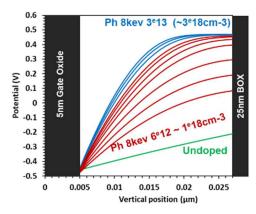

Linear regime threshold voltage V<sub>tlin</sub> variation with channel implantation dose is overestimated by TCAD (green curve on Fig.7). SIMS (Fig.8) characterization reveals that asimplanted phosphorus profile in the 22nm silicon film is well predicted by TCAD (blue curves). However, it also highlights that the mean doping in the silicon film is significantly reduced after the gate oxide formation (Fig.8 dashed lines:~3.10<sup>18</sup>cm<sup>-3</sup> doping loss during the gate oxide formation). We attribute it to doping consumption in the surface during the oxidation and include it as a 3nm silicon etching in the process simulation. The phosphorus profile agreement between TCAD and SIMS is improved (Fig.8, red curves) as well as the V<sub>tlin</sub> variation (red curve on Fig.7) up to phosphorus dose  $1.5.10^{13}$ cm<sup>-2</sup> and  $V_{tlin}$ =-1.5V. As the channel doping increases, the silicon depletion layer decreases and can be lower than the silicon film: the device

Fig. 6: as-implanted and after gate oxide phosphorus profile in the Si film comparison between SIMS and TCAD

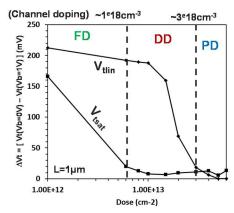

Fig. 9 : L=1 $\mu$ m pMOS  $V_{tlin}$  and  $V_{tsat}$  variation from  $V_B$ =0 to  $1V_b$  as a function of the channel implantation dose. Channel doping from TCAD are provided.

Fig. 10 : Potential variation in the Si film from the gate oxide to the BOX at  $V_G$ = $V_{din}$  and  $V_D$ =-0.1V for several channel implantation dose.

operation can move from Fully Depleted (FD) to Partially Depleted (PD) operation. Because of the undepleted portion of the silicon film in PD operation, the ground plane bias (V<sub>B</sub>) has no impact on V<sub>T</sub> contrary to FD [2]. Fig.9 shows the measurement of the  $V_{\text{tlin}}$  dependency to  $V_{\text{B}}$  as a function of channel doping and demonstrates that PD operation starts around 3.10<sup>18</sup>cm<sup>-3</sup> channel doping. Same plot is performed with  $V_{tsat}$  (saturated regime  $V_T$  at  $V_D$ =-2.5V) shows that  $V_B$ impact is canceled for doping >1.10<sup>18</sup>cm<sup>-3</sup>. The channel doping range where V<sub>tlin</sub> depends on the V<sub>B</sub> and V<sub>tsat</sub> doesn't depends on V<sub>B</sub> defines the Dynamic Depleted (DD) operation where the device is FD in linear regime, and PD in saturated regime [10,11]. The potential variation at  $V_G = V_T$  and  $V_D = -$ 0.1V in the Si film is shown on Fig.10 and highlights the difference between the 3 operating regimes: linear for FD, curved for

DD and curved with a constant portion close to the BOX for PD. With channel doping increase, the depleted layer controlled by the gate decreases, so the floating area is thicker. We then focused on TCAD description of device with  $V_T$  lower than -1.5V (FD and DD regimes).

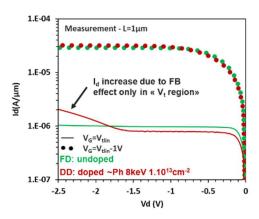

Fig. 11 : Measured  $I_d$ - $V_d$  for L=1 $\mu$ m doped and undoped pMOS at  $V_G$ = $V_{din}$  &  $V_G$ = $V_{tin}$ -1V

#### V. FLOATING BODY EFFECTS TCAD DESCRIPTION

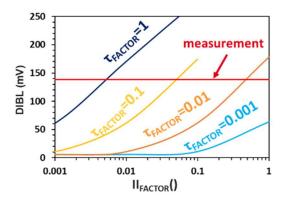

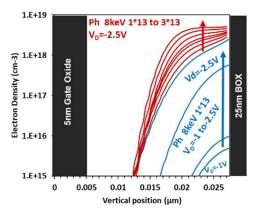

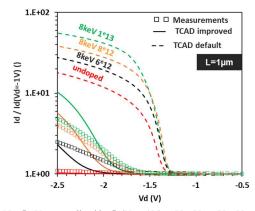

In DD operation, Floating Body effects (FB) occur. As shown by I<sub>d</sub>-V<sub>d</sub> measurements (Fig.11), they produce a drain current increase at  $|V_D|$ >1.5V only for  $V_G$  around  $V_T$ . This is due to the silicon floating area charged by Impact Ionization (II) at the drain [5]. For pMOS, it is charged with electrons: this negative charge reduces V<sub>tsat</sub> and cancels the V<sub>B</sub> impact on V<sub>tsat</sub>: the long channel DIBL increases with channel doping because FB effects are worsened (Fig. 12). To account for it in TCAD, II needs to be activated. DriftDiffusion simulations with default parameters leads to too high DIBL (blue on Fig.12). II is usually lower with hydrodynamic simulation [12] but DIBL is still too high. To reduce DIBL for long and doped channel, FB effect needs to be reduced. Two options are possible: reducing the II rate by a factor (II<sub>FACTOR</sub>) or increase the recombination rate in the floating area with carrier lifetime reduction by a factor  $(\tau_{FACTOR})$ . Note that is was demonstrated that carrier lifetime are shorter in thin film SOI than in bulk device (~10ns is 7nm Si film, [13]). Fig.13 shows the TCAD long channel DIBL variation for  $II_{FACTOR}$  and  $\tau_{FACTOR}$  variations: in the following, we use (II<sub>FACTOR</sub>= 0.01 and  $\tau_{FACTOR}$ =0.2 (same value as [14]). With this TCAD improvement, DIBL variation with channel doping is reproduced (Fig.12). To

Fig. 12 : DIBL variation with the channel implantation dose from measurement and different TCAD settings.

Fig. 13 : L=1 $\mu$ m DIBL variation with  $II_{FACTOR}$  for several  $\tau_{FACTOR}$  at constant channel doping (Phosphorus dose  $6.10^{12}$ cm<sup>-2</sup>) compare to measurement (red line)

observe FB effects, we need  $|V_D| > 1.5V$  and channel doping needs to be  $> 1.10^{18} cm^{-3}$  (Fig.14). It also shows floating area thickness increases with channel doping: the electrons stored increases, so the charge increases and the DIBL increases. Finally, Fig.15 shows the FB effects TCAD description improvement for various channel doping on  $I_d$ - $V_d$  at  $V_g$ = $V_{tlin}$ .

To highlight FB effects impact on the characteristic, drain current is normalized by its value at V<sub>d</sub>=-1V, where there is

$\label{eq:Fig. 14:Electron density in the Si film at $V_G\!\!=\!\!V_{tlin}$ from tuned $TCAD$ for $V_D$ and channel doping variation.}$

$\label{eq:fig.15: ID-VD normalized by ID(VD=-1V) at VG=VT at VG=Vtlin, from measurement, defaut hydrodynamic TCAD and tuned TCAD for channel doping variation.}$

no FB effect. Our description can still be improved, but the channel doping impact is well captured.

#### VI. CONCLUSION

In this paper, we propose a TCAD description of 22nm thick SOI device including the floating body effect variation with channel doping. We highlight that large parameter variation is required to match the experimental long channel DIBL, but the modeling still needs to be improved to reproduce experimental  $I_DV_D$  characteristics.

#### REFERENCES

- [1] P. Chevalier et al., "PD-SOI CMOS and SiGe BiCMOS Technologies for 5G and 6G communications," 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2020, pp. 34.4.1-34.4.4, doi: 10.1109/IEDM13553.2020.9371954.

- [2] N. Planes et al., "28nm FDSOI technology platform for high-speed low-voltage digital applications," 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 2012, pp. 133-134, doi: 10.1109/VLSIT.2012.6242497.

- [3] O. Weber et al., "18nm FDSOI Enhanced Device Platform for ULP/ULL MCUs," 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2022, pp. 27.2.1-27.2.4, doi: 10.1109/IEDM45625.2022.10019397.

- [4] R. Carter et al., "22nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications," 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2016, pp. 2.2.1-2.2.4, doi: 10.1109/IEDM.2016.7838029.

- T. Ouisse et al. "Investigation of floating body effects in silicon-on-insulator metal-oxide-semiconductor field-effect transistors Journal of Applied Physics 70, 3912–3919 (1991) <a href="https://doi.org/10.1063/1.349200">https://doi.org/10.1063/1.349200</a>

- [6] S. K. H. Fung et al., "Controlling floating-body effects for 0.13 /spl mu/m and 0.10 /spl mu/m SOI CMOS," International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), San Francisco, CA, USA, 2000, pp. 231-234, doi: 10.1109/IEDM.2000.904299.

- [7] S. Pemmaraju and S. A. Parke, "Elimination of body effects in SOI CMOS devices," 2004 IEEE Workshop on Microelectronics and Electron Devices, Boise, ID, USA, 2004, pp. 126-128, doi: 10.1109/WMED.2004.1297373.

- [8] J. Sleight and K. Mistry, "A compact Schottky body contact technology for SOI transistors," International Electron Devices Meeting. IEDM Technical Digest, Washington, DC, USA, 1997, pp. 419-422, doi: 10.1109/IEDM.1997.650414.

- [9] F. Guyader et al., "3-Tier BSI CIS with 3D Sequential & Hybrid Bonding Enabling a1.4um pitch,106dB HDR Flicker Free Pixel," 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2022, pp. 37.4.1-37.4.4, doi: 10.1109/IEDM45625.2022.10019432.H.-K. Lim et al. TED 83

- [10] J J. W. Sleight and K. R. Mistry, "DC and transient characterization of a compact Schottky body contact technology for SOI transistors," in IEEE Transactions on Electron Devices, vol. 46, no. 7, pp. 1451-1456, July 1999, doi: 10.1109/16.772490.

- [11] W. Wu et al."Surface-potential-based compact modeling of dynamically depleted SOI MOSFETs," Solid-State Electronics, Volume 54, Issue 5,2010 https://doi.org/10.1016/j.sse.2009.12.040.

- [12] D. Munteanua and G. Le Carval "Assessment of Anomalous Behavior in Hydrodynamic Simulation of CMOS Bulk and Partially Depleted SOI Devices" Journal of The Electrochemical Society, Volume 149, Number 10 https://doi.org/10.1149/1.1506168

- [13] K. H. Lee, M. Bawedin, H. -J. Park, M. Parihar and S. Cristoloveanu, "Carrier lifetime evaluation in FD-SOI layers," 2017 47th European Solid-State Device Research Conference (ESSDERC), Leuven, Belgium, 2017, pp. 140-143, doi: 10.1109/ESSDERC.2017.8066611.

- [14] D. Bosch et al. "SOI pMOS drain leakage understanding based on TCAD and measurements" to be published to SISPAD 2023