## In memory energy application for resistive random access memory

Paola Trotti, Sami Oukassi, Gabriel Molas, Mathieu Bernard, François Aussenac, Gaël Pillonnet

#### ▶ To cite this version:

Paola Trotti, Sami Oukassi, Gabriel Molas, Mathieu Bernard, François Aussenac, et al.. In memory energy application for resistive random access memory. Advanced Electronic Materials, 2021, 7 (12), pp.2100297. 10.1002/aelm.202100297. cea-04523527

### HAL Id: cea-04523527 https://cea.hal.science/cea-04523527v1

Submitted on 17 May 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# In Memory Energy Application for Resistive Random Access Memory

Paola Trotti,\* Sami Oukassi, Gabriel Molas,\* Mathieu Bernard, François Aussenac, and Gaël Pillonnet

This work explores the innovative concept of a hybrid dual-behavior device, based on emerging nonvolatile memory technology, for both data retention and energy storage. RRAM (resistive random access memory) is considered a major candidate as next-generation memory, thanks to its promising performances in terms of scalability and CMOS process compatibility. Its working mechanisms, based on faradaic processes, motivate the study on the feasibility of operating RRAM also as energy storage element. To evaluate the energy capability, various electrochemical characterizations on state-ofthe-art RRAM are presented. The highly resistive electrolyte, extremely small physical scale (nm), and current range (pA), put in quite a critical framework, far from conventional solid-state batteries. Cyclic voltammetry tests reveal that although no oxidation peak appears during the redox cycle, the cells behave as standard electrochemical storage elements when investigating the impact of the scan rate, maximum positive voltage, and area on the reduction peak. Concentration and diffusion coefficients are derived, in the order of 10<sup>-12</sup> cm<sup>2</sup> s<sup>-1</sup> and few mmol cm<sup>-3</sup>, respectively, while energy storage capability amounts to 3.5 pJ μm<sup>-2</sup>. Finally, design concepts are proposed, where RRAM "in-memory energy" technology would be a newfangled approach to meet the needs of various emerging and standard applications.

#### 1. Introduction

Recent advances in fields like artificial intelligence (AI), the internet of things (IoT), virtual reality, and cloud computing have been demanding ever-increasing computational capability. Power-efficient calculation is key in any task implemented on a chip, from high-performance core computing to the edge of IoT. While process miniaturization managed to effectively reduce consumptions in the past, its effectiveness has been dropping for recent technological nodes, the overall balance in power cost coming majorly from losses over transmission lines. As a result, further downscaling is expected to soon no longer pay off the development investment, and alternative strategies

P. Trotti, S. Oukassi, G. Molas, M. Bernard, F. Aussenac, G. Pillonnet CEA LETI

Univ. Grenoble Alpes Grenoble 38000, France E-mail: paola.trotti@cea.fr; gabriel.molas@cea.fr

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202100297.

DOI: 10.1002/aelm.202100297

must be considered. This branch of research involves the so-called Moore than More's devices.<sup>[1]</sup> Some attempts to ease consumption rely on on-chip integration of nanoscale energy sources,<sup>[2,3]</sup> while others, notably in memory computing (IMU),<sup>[4]</sup> offer a revisited architecture where computation is decentralized. Other research groups proposed the integration of energy sources in close proximity of the memory,<sup>[5,6]</sup> or completely integrated within the memory architecture.<sup>[7]</sup>

In this work, we explore a radically different concept, which lies on "dual-behavior" devices, able to store either information or energy, depending on the applied bias. Such capability would be greatly beneficial, allowing localized and high bandwidth energy supply to the processing unit (the memory or a dedicated arithmetic logic unit, ALU). The samples considered in our study indeed resemble ionic batteries at the nanoscale, providing ground to our inquiry of using these devices as energy sources, other than memory cells. Their operation

relies on faradaic processes; therefore, the resulting energy density is expected to well exceed that of electrostatic capacitors, possibly being comparable to supercapacitors'. [8] The diameter of the devices under study can range between 1 and 100 µm, resulting in much smaller than the diameter of state-of-the-art planar supercapacitors (~mm²),[2] making such architecture more scalable and granular than any other state-of-the-art integrated power source. Energy storage is achievable when the device is, under a memory point of view, storing a logic 0, and could be accumulated during low logic operation activity for later use, for example, during the most power-hungry phases. These devices would also offer the advantage of placing the battery cell in close proximity to the target, meaning reduced IR drop and voltage undershoot, which develop in a typical inductive-impedance power delivery network (PDN).[9] A broad range of applications could be envisioned, each demanding different energy requirements, with widespread specifications. The most suitable target field should be selected taking into account the output voltage, energy, and power delivered by such RRAM-based batteries. In this work, we provide an outlook on some possible implementations, with some quantified ranges in terms of energy and instantaneous power requirements. Figure 1 reports the three main eligible domains: energy to memory, [10] energy to logic, [11] and neuromorphic computing.[12-15]

|                       | Required<br>Energy [pJ] |                     | Operating<br>Voltage [V] | Instantaneous<br>Power [uW] |

|-----------------------|-------------------------|---------------------|--------------------------|-----------------------------|

| Energy to memory      | [10] NAND FLASH         | NAND FLASH 0.01 ~20 | ~20                      | ~1m                         |

| ******                | NOR FLASH               | 100                 | ~5                       | 100                         |

| 5420                  | PCM                     | 100                 | 3-5                      | ~1k                         |

| 50.57                 | RRAM                    | 1-10                | 2-5                      | ~100-1k                     |

| 77.5                  | STTRAM                  | 0.1                 | 1-3                      | ~10                         |

|                       | (switching energy       | per cell)           |                          |                             |

| Emanary to logic (11) | IoT processor:          |                     |                          |                             |

| Energy to logic [11]  | ARM Cortex-M0           | 3 - 6.4             | 0.4-0.7                  | 0.64 - 240                  |

|                       | ARM Cortex-M0+          | 1.1 - 11.7          | 0.19-1.2                 | 0.4 - 735                   |

|                       | MSP430 compatible       | 7                   | 0.32-0.48                | 56 - 497                    |

| <b>→</b>              | ARM Cortex-M3           | 23                  | 0.5-1                    | 23 - 460                    |

|                       | (minimum energy         | per operation       | )                        |                             |

| Neuromorphic          | Synaptic technology:    |                     |                          |                             |

| _                     | SRAM-based [12]         | 27                  | 28 nm-compatible         | 63 k                        |

|                       | SRAM-based [13]         | 105                 | 14 nm-compatible         | *******<br>*                |

|                       | RRAM-based [14]         | N/A                 | 40 nm-compatible         | 9.9 k                       |

|                       | RRAM-based [14]         | N/A                 | 180 nm-compatible        | 15.8 k                      |

|                       | RRAM-based [15]         | 180                 | 130 nm-compatible        | 1.5 k                       |

|                       | (Energy per synar       | otic event)         |                          |                             |

Figure 1. List of required energy, operating voltage and instantaneous power for various applications.

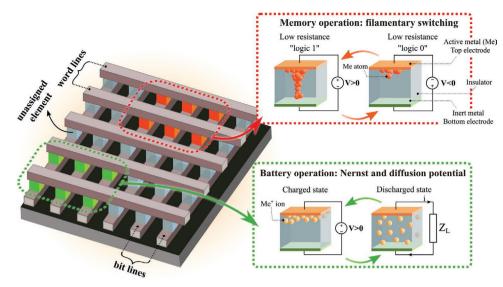

#### 2. In-Memory Energy Storage Concept

RRAM is a popular emerging memory technology that relies on (a wide range of) materials, which are able, under appropriate bias, to switch their resistance value between high and low. Different resistances are associated with different logic states, namely a low resistive state (LRS) and a high resistive state (HRS). States are nonvolatile, meaning that once a resistance transition happens, the bias can be removed without occurring into the degradation of the information stored. Known as the filamentary switching effect, the phenomenon behind RRAM operation consists in the deposition and dissolution of a thin metallic filament between the device's access electrodes. [16–18] A schematic illustration of the memory effect is reported in Figure 2. Some major advantages of RRAM technology are:

- high scalability (typical cell areas are ≈100 nm<sup>2</sup>);<sup>[19]</sup>

- II. low operating energy (down to 10 pJ per bit);<sup>[16]</sup>

- III. fast switching speed (in the order of ≈ns);<sup>[20]</sup>

- IV. high retention of the stored logic state;<sup>[21]</sup>

- V. high cycling capability (>10<sup>6</sup> cycles);<sup>[22]</sup>

- VI. a common BEOL cell structure (metal-insulator-metal stack);<sup>[23]</sup>

- VII. Compatibility with CMOS technology, by materials and fabrication process.  $\sp[24]$

A typical RRAM cell is structured as a metal-insulator-metal (MIM) stack, whose middle layer is an electrical insulator that is relatively ion conductive, enclosed between an electrochemically active and inert material. The resulting configuration is an electrode-electrolyte-electrode system, in fact resembling a classical

ionic battery.<sup>[8]</sup> Measurements of electro-magnetic-field (EMF) in RRAM have been reported in the literature, [<sup>25,26]</sup> and an interplay of Nernst, diffusion, and Gibbs-Thompson potentials have been suggested as underlying causes. [<sup>25]</sup> RRAM-based batteries would present the advantage of being highly scalable and dynamically allocable, which translates into the possibility of placing energy sources right next to memory blocks, supplying energy for the writing of logic states. Therefore, less power waste over transmission lines and high PDN efficiency could be achieved. An extended concept of in-memory-computing-and-energy, performed through RRAM devices, thus holds great potential.

Our farsighted concept of a memory-battery dual-behavior device is presented in Figure 2: the elements are arranged in a crossbar array<sup>[27,28]</sup> to maximize integration density. In the envisioned design, subarrays could be dynamically assigned to perform as either memory or battery, depending on realtime needs. In a practical implementation, each element of the array shown in Figure 2 comprises a RRAM cell in series with a selection device, like a transistor or a selector in order to avoid leakage and disturbance between cells.[16] When operated in battery mode, the charging operation follows a similar procedure to the writing of a memory cell (better details given in Section 4), while the discharging should be operated by some dedicated control circuitry. This block might be able to address multiple cells in parallel, possibly adjusting the number of selected elements in accordance with the demanded energy, in order for them to supply the energy to the load. Section S2 (Supporting Information) illustrates a system-level design for a hybrid dual-behavior crossbar-based device.

21991608, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms/

and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons I

Figure 2. Innovative concept of a hybrid dual-behavior RRAM device. In the envisioned implementation, elements are placed at the intersection of word and bit lines, in a crossbar array configuration, which allows maximizing energy and memory density. In red and green, respectively, cells storing logic values and energy.

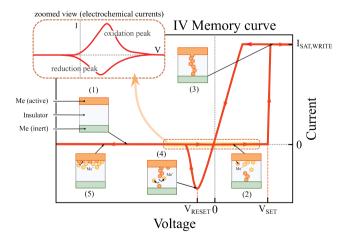

#### 2.1. Operating Principle of RRAMS

**Figure 3** reports a typical RRAM I-V curve, obtained by reading the current flowing between the cell's electrodes while sweeping the voltage across them (quasi-static operation). The device initially is in HRS (typically in a range  $[10^7-10^{11}]$   $\Omega^{[29,30]}$ ), so that at point (1), the current approaches 0. Towards (2), the increasing voltage gradually enhances the oxidation of the top electrode, which releases metal cations ( $Me^{z+}$ ) inside the electrolyte, in parallel reducing some  $Me^{z+}$  ions at the electrolyte/bottom electrode interface, according to the general reaction:

$$Me^{z+} + ze^{-} \leftrightarrow Me$$

(1)

Atom by atom, the filament piles up. The gap between the filament tip and the top electrode grows smaller and enhances electron tunneling, boosting conduction until the filament is fully formed (3). $^{[17,18]}$  At the set voltage,  $V_{\text{SET}}$ , the cell completes its transition to a low resistance state, and toggles its logic value to a logic 1. Once the current hits  $I_{SAT,WRITE}$ , typically around 100 µA,[31] the current-limiting element in series with the memory prevents further increase, in order to avoid cell damage. As a result, the current is held at the compliance value  $I_{SAT,WRITE}$  . The first high to low resistance transition a device experience is called forming process, and usually occurs at a higher voltage (called "forming voltage") with respect to subsequent HRS to LRS switchings, called set events, or set processes. After the cell reaches the LRS, the sweeping direction is reversed. The filament continues to bridge the electrodes until point (4), when the reactions of Expression 1 are reversed: oxidation of Me to Me<sup>z+</sup> takes place at the bottom electrode/electrolyte, while reduction of Mez+ to Me occurs at the electrolyte/top electrode interface. The filament is disrupted at the reset voltage,  $V_{\text{RESET}}$ , at which the cell's resistance switches back to a high value.

The inset of Figure 3 shows a zoomed view of the high-lighted area, with electrochemical currents in evidence, associated with the redox peaks of the reactions happening at the electrode interfaces. A non-zero voltage might be measured across the cell as a result of the ongoing reactions and ion gradients development. Valov et al. have reported measurements of open-circuit voltage across RRAM while the cell is in HRS.<sup>[25]</sup> They motivated their findings with the arise of Nernst, Diffusion, and Gibbs-Thomson potentials between the electrodes of the devices under study.<sup>[25]</sup> A diffusion potential resulted from a non-null gradient of charge inside the electrolyte, introduced by the release of redox ion products. Such potential can thus be externally controlled, following the activation of bias-triggered electrochemical reactions. Below the activation energy, reactions cannot continue, and ions

**Figure 3.** A typical *I–V* curve of a RRAM. The memory is, initially (1), in a logic "0" state (highly resistive), and switches to a logic "1" in (3), when the filament bridges the electrodes. The memory goes back to "0" in (4), when the filament dissolves. In the inset, a zoomed view showing the electrochemical currents (redox peaks).

2199160x, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/aelm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms-and-conditional)

ms) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons License

spontaneously diffuse back to a homogeneous concentration over time, gradually nulling the voltage drop. A corresponding "re-equilibrium" current can be detected. Valov's group reported discharging short-circuit currents, when externally grounding the electrodes after having triggered redox reactions. [25] Although their research lies in a theoretical domain, meant to deepen the filamentary switching understanding, their findings inspired our study on the feasibility of a practical implementation of the nanobattery effect in RRAMs.

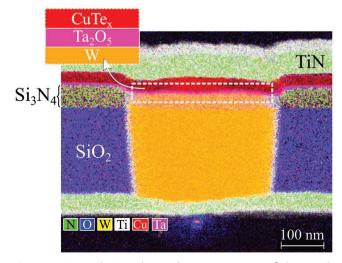

#### 3. Experimental Section

RRAM device-under-test (DUT) stack is: CuTe<sub>2</sub>Ge/  $\text{Ta}_2\text{O}_5/\text{W}.^{[32-36]}$  The samples were fabricated on 8 in. wafers, in 1R cell configuration.<sup>[16]</sup> Three different Ta<sub>2</sub>O<sub>5</sub> thickness (5, 10, and 15 nm) were produced and tested. Figure 4 is reported a TEM picture with ESD elemental mapping. "Plug-shaped" bottom electrodes (W) were first deposited. Consecutively, the Ta<sub>2</sub>O<sub>5</sub> layer was RF sputtered, adjusting the sputtering time according to the targeted thickness. The density of the Ta<sub>2</sub>O<sub>5</sub> layer resulted approximately equal to 7 g cm<sup>-3</sup>. A 30 nm thick CuTe2Ge alloy was deposited as the top electrode, and successively capped by a Ti/TiN layer. Seven different areas were produced (0.07 to 2.27 µm<sup>2</sup>) by adjusting the bottom electrode diameter, in a range from 0.3 to 1.7 µm, with a step of 0.2 µm. Wafer testing was performed on a Cascade microprobe station, implementing triaxial Kelvin-connected SMUs, controlled by Parameter Analyzer HP4155.

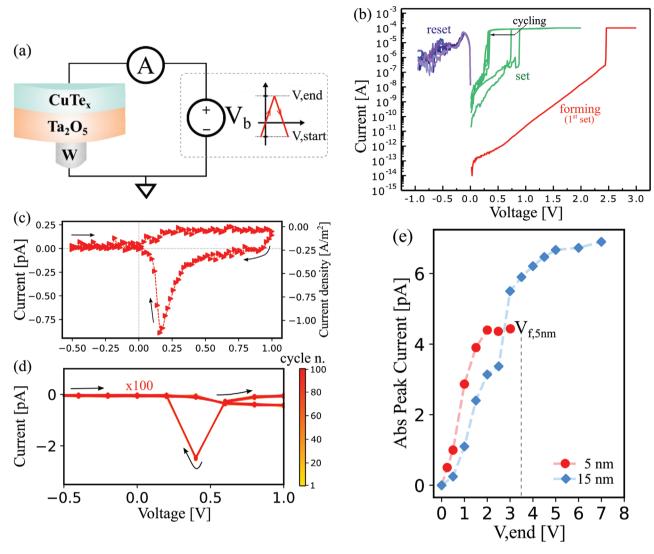

Fresh (i.e., unformed) devices have been characterized through the setup shown in Figure 5a, which allows investigating both memory (in quasi-static testing regime) and battery operation. In the latter case, the voltage drop across the device has to be limited below the forming value. Battery behavior was tested through cyclic voltammetry (CV), in two-electrode configuration. A linear voltage ramp biasing the access contacts was applied while reading the current flowing through the stack. In the voltage range and sweeping speed (≈1 V s<sup>-1</sup>) considered for the CV tests, negligible electron

Figure 4. TEM with ESD elemental mapping picture of the sample structure

tunneling and capacitive contributions arise, thus the measured current was assumed to be deriving mainly from electron exchange through redox reactions.

#### 4. Results and Discussion

Memory operation was first validated; Figure 5b reports typical characteristics for a 5 nm sample: forming, set and reset curves are shown. Further memory characterization is reported in Section S1 (Supporting Information). Next, we proceeded to investigate the electrochemical behavior, the maximum value of the sweeping voltage, Vend, being limited below the forming value, which was found to remarkably increase with the thickness of the Ta<sub>2</sub>O<sub>5</sub> layer: a mean of 3 V for 5 nm, 5 V for 10 nm, and >15 V for 15 nm. Results of CV tests are presented in Section 4.1, while mathematical extrapolation of diffusion and concentration coefficients is reported in Section 4.2.

#### 4.1. Cyclic Voltammetry Results

A typical CV curve, for a 5 nm thick Ta<sub>2</sub>O<sub>5</sub> sample, is shown in Figure 5c. A clear current peak can be observed when sweeping through  $V_b$ 's falling ramp, at approximately 200 mV. We associate such a peak to a reduction reaction of copper cations at the CuTe<sub>2</sub>Ge/Ta<sub>2</sub>O<sub>5</sub> top electrode/electrolyte interface.

Given the absence of a reference electrode, it is nontrivial to assign a specific reaction to the current peak. Aqueous solution potentials suggest that the reduction of Cu<sup>+</sup> ions to Cu is the most energetically favorable.[37] Although our (solid) electrolyte is far from an aqueous solution, some research groups hypostatized that water molecule might be incorporated inside nanopores of Ta<sub>2</sub>O<sub>5</sub> due to ambient humidity, [26] therefore aqueous potentials might still hold true. Applying this assumption to our samples, during the positive voltage scan the reaction taking place at the CuTe<sub>2</sub>Ge/Ta<sub>2</sub>O<sub>5</sub> interface could be assigned to:

$$Cu \to Cu^+ + e^- \tag{2}$$

Sustained by the counter-reaction: [26,38]

$$2H_2O + 2e^- \rightarrow 2OH^- + H_2$$

(3)

At the Ta<sub>2</sub>O<sub>5</sub>/W interface: The reaction expressed by Expression 3 might be responsible for Cu<sup>+</sup> generation when no prior copper cation is present, and afterward concurs with the reduction on Cu<sup>+</sup> at the Ta<sub>2</sub>O<sub>5</sub>/W interface:

$$Cu^{+} + e^{-} \rightarrow Cu \tag{4}$$

Upon negative voltage scan rate, the oxidation in Expression 2 would take place at the Ta<sub>2</sub>O<sub>5</sub>/W interface, while Expression 4, which we associate with the reduction peak observed in Figure 5c, occurs at the CuTe<sub>2</sub>Ge/Ta<sub>2</sub>O<sub>5</sub>. It can be observed in Figure 5c,d that no oxidation peak appears when sweeping to positive voltages. This result agrees with what was reported in the literature for high-density Ta2O5 samples, where it was found that the oxide density trades with electrochemical

2199160x, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/aelm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms

ns) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons License

**Figure 5.** Cyclic voltammetry results. a) The test setup. In b) forming, set and reset curves for a 5 nm thick  $Ta_2O_5$  sample. c) A typical voltammogram, featuring a clear current peak during the negative scan rate. In d) At lower resolution, the peak of a 10 nm thick  $Ta_2O_5$  device over 100 cycles, the curves perfectly overimposing on each other. In e) the current peak amplitude (absolute value) versus  $V_{end}$ . Different slopes can be observed for different thicknesses, while a saturation trend for increasing values of  $V_{end}$  bends the curves for both cases.

currents, and no oxidation peak was observed above 7.1 g cm<sup>-3</sup>,<sup>[26]</sup> a value that closely approaches that of our samples. Figure 5d reports 100 overimposed CV cycles for a 10 nm thick sample. The peaks appear less detailed with comparison to Figure 5a, as a lower resolution was used to speed test times. The curves perfectly overlap with one another, no remarkable change in shape is appreciable over cycling. Figure 5e reports various current peak amplitudes, each obtained by sweeping  $V_{\mathrm{end}}$  in a range from 0 to 2 V, while keeping  $V_{\mathrm{start}}$  fixed at -2 V. Each curve represents a different oxide thickness sample: namely 5 and 15 nm. The maximum  $V_{\rm end}$  value is limited to 3.5 V for the 5 nm sample, as the device was formed at 4 V. For either case, the peak current at  $V_{\text{end}} = 0$  was null (approaching the noise level). This result can be motivated with the lack of copper cations to reduce when no sweeping to positive voltages takes place beforehand. For  $V_{\rm end} > 0$ , the relationship between voltage and current is initially ( $V_{\rm end,5~nm}$  < 2,  $V_{\rm end,15~nm}$  < 3) close to linear, with the 5 nm thick case exhibiting a higher slope. For greater voltages, however, the current saturates in both cases. Our interpretation is that the cation content can effectively be increased by heightening  $V_{\rm end}$  until some threshold value, beyond which the saturation trend sets in, possibly as a consequence of having reached the maximum solubility of copper ions inside the  ${\rm Ta_2O_5}$  electrolyte. Our results thus support the fact that, although no oxidation peak is detected during positive scan rates, some oxidation processes must be taking place nonetheless, providing copper cations which are later reduced when the scan polarity is reversed.

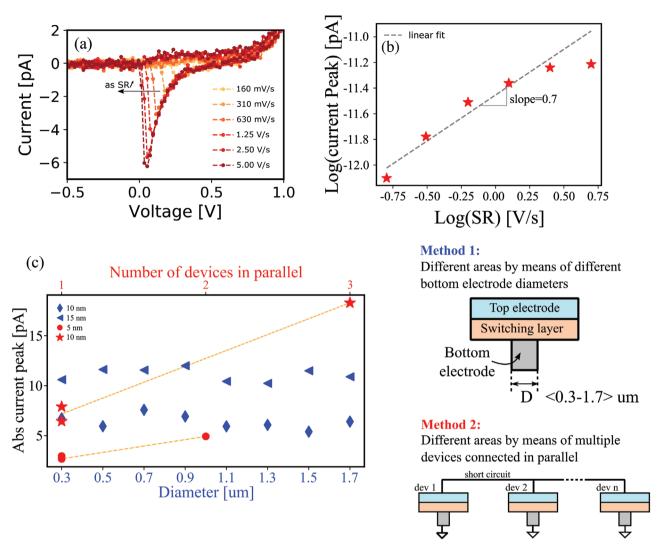

To further investigate the nature of current peaks in our DUT, we performed CVs at various scan rates, ranging from  $160 \text{ mV s}^{-1}$  to  $5 \text{ V s}^{-1}$ . **Figure 6**a shows an overlap of six curves, each obtained at a different scan rate. It can be observed that, increasing the sweep speed, the current peak amplitude increases and the voltage at which the peak is obtained drifts

2199160x, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/aelm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms

-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons License

Figure 6. Impact of scan rate and area. a) In different colors, CV curves at various sweep rates, ranging from 160 mV  $s^{-1}$  to 5 V  $s^{-1}$ . b) The amplitude of the current peak versus the scan rate. (c) Trend of peak current versus area, increased either by means of a larger bottom electrode diameter (Method 1, in blue) or by multiple devices connected in parallel (Method 2, in red).

to more negative values. The shift in peak position is typical of irreversible processes, with which we identified our reactions. The Randles-Sevick equation for irreversible processes declines as:<sup>[39]</sup>

$$I_{p} = 0.4958(Fn)^{3/2}(RT)^{-1/2}Ac_{0}(\alpha Dv)^{1/2}$$

(5)

where  $I_{\rm p}$  is the peak current, F is the Faraday constant, n is the number of electrons involved in the reaction, R is the gas constant, T is the absolute temperature, A is the electrode area,  $c_0$  the concentration coefficient,  $\alpha$  is the transfer coefficient, D is the diffusion coefficient and v is the scan rate. Equation 5 dictates a linear trend between the peak current and the scan rate. Figure 5b shows a log–log plot of current peak amplitudes versus the scan rate, along with a linear fit showing a slope equal to 0.7. Equation 5 predicts a slope of 0.5 for faradaic processes, so we associate the measured currents as mainly deriving from redox reactions. We point out that capacitive

currents should approach a slope equal to 1, and feature a boxshape behavior over the whole voltage range, which appears far from our reported case, as shown in Figure 5a. The trend of the current to the scan rate appears to deviate from linear when the voltage sweep is fastened. The bend of the curve might be explained through relatively low reaction kinetics, which cannot keep up to the pace when the potential is rapidly changing. Equation 5 also expresses a linear device area-peak current relationship. We measured the trend for our samples by comparing CVs, in the same testing conditions, obtained from devices with different areas (Figure 6c, method 1). As shown in Figure 6c, we did not observe a peak current variation when testing different area samples. However, we were able to measure a linear area-peak current trend when physically connecting either two or three devices in parallel (Figure 6c, method 2). Our interpretation is that the ongoing electrochemical reactions are possibly limited to a restricted portion of the device electrolyte, in a similar manner to the resistive switching effect.[40,41]

2199160x, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/aelm. 202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com

of use; OA articles are governed by the applicable Creative Commons License

#### 4.2. Diffusion and Concentration Coefficient Extrapolation

Further investigation was carried out by deriving the diffusion and concentration coefficients characterizing the reactions taking place in our samples. The recombining charge during the reduction process was first calculated by discrete timeintegration of the current during the negative voltage scan:

$$Q_{\text{Cu}^+} \partial t \left| \sum_{n=0}^{N} i_n \right| \tag{6}$$

where  $\partial t$  is the time interval between each sample,  $i_n$  the nth value of the current and N the number of samples collected. In order to exclude tunneling contributions, only samples in the interval [-0.2, 0.6] V were considered. We then derived the injected moles with Faraday law:

$$N_{\text{Cu}^{+}} = \frac{Q_{\text{Cu}^{+}}}{n F} \tag{7}$$

where n is the oxidation number (assumed equal to 1) and F the Faraday constant. The concentration coefficient, for our sample's cylindrical geometry, can be expressed as:

$$c_{\text{Cu}^{+}} = \frac{N_{\text{Cu}^{+}}}{V_{\text{Ta}_{2}\text{O}_{5}}} = \frac{N_{\text{Cu}^{+}}}{t_{\text{GeS}_{2}} \left(\pi \frac{d^{2}}{2}\right)}$$

(8)

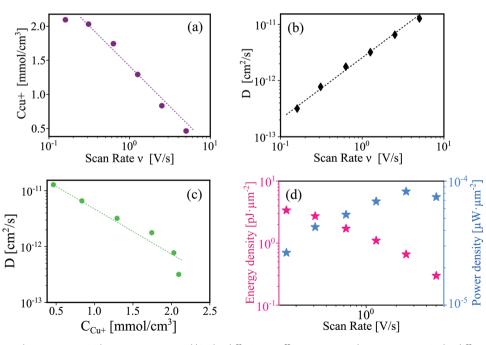

where  $V_{\rm Ta_2O_5}$  is the volume of the electrolyte where the copper cations are dissolved, and d is the diameter of the bottom electrode. **Figure 7**a reports the concentration coefficient versus the scan rate:  $c_{\rm Cu+}$  reasonably drops with increasing v, in accordance with Equation 5, as less time is available for reactions to

generate products when the potential is swept faster. Finally, diffusion coefficients were extrapolated using Equation (5):

$$D = \frac{RT}{\alpha v (Fn)^3} \left( \frac{I_{pk}}{0.4958 \, A \, c_{Cv^+}} \right)^2 \tag{9}$$

where  $\alpha$  has been taken equal to 0.5.<sup>[26]</sup> Results, at different scan rates, are plotted in Figure 7b, while Figure 7c shows D versus  $c_{\text{Cu+}}$ . It can be seen that the trend of D with  $\nu$  is opposite to that of the concentration coefficients, as diffusivity increases when less  $c_{\text{Cu+}}$  ions are present. Our trends are in agreement with reports from the literature for a similar RRAM stack.<sup>[26,42]</sup> The energy storage capability was evaluated through:

$$E_{SR,i=} \partial t \left| \sum_{n=0}^{N} i_n V_n \right| = \partial t P \tag{10}$$

where  $V_{\rm n}$  are the values of the voltage at which the current was sampled, and  $i_n$  the corresponding current samples, during the negative scan. P is the released power. Figure 7d reports estimated energy and power densities versus the scan rate. It can be seen that the energy density is decreasing when the scan rate is higher, as a result of having less available ions.

#### 5. Summary and Perspectives

The characterization of RRAM in-memory energy devices conducted in this work allows us to draw some preliminary considerations:

I. The proposed technology allows to operate a device simultaneously both as memory and energy storage

Figure 7. Electrochemical parameters. a) The concentration and b) The diffusion coefficients, versus the scan rate. In c), the diffusion coefficient versus the concentration coefficient. (d) Energy (in pink) and power density (in blue), versus the scan rate.

2199160x, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Condition (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Condition (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Condition (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Condition (https://onlinelibrary.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online Library.wiley.com/doi/10.1002/aclm.202100297 by CEA National, Wiley Online (https://onlinelibrary.wiley.com/doi/10.100297 by CEA National, Wiley Online (https://onlinelibrary.wiley.com/doi/10.10029

and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons License

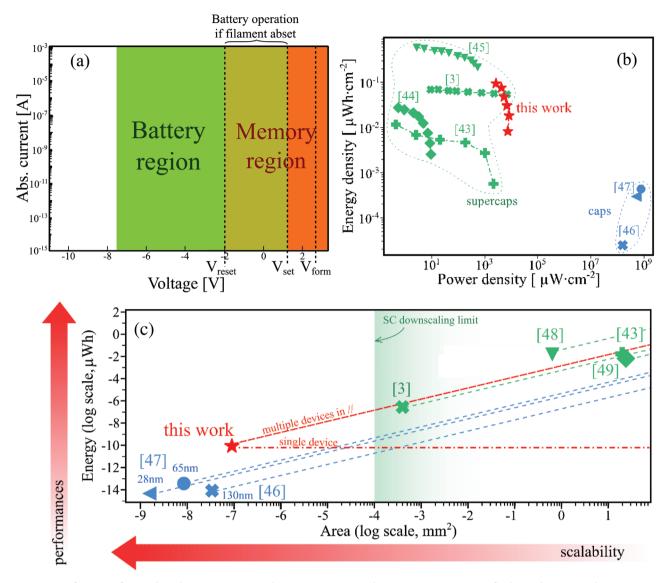

**Figure 8.** Specifications of RRAM-based in-memory energy devices. a) Reports qualitative operating regions of a device. b) Ragone plot. In green are reported some planar supercapacitors, [3,43-45] in blue on-chip capacitors for different technological nodes (130 nm<sup>[46]</sup> 65 nm and 28 nm FDSOI<sup>[47]</sup>) and in red the value extrapolated for our work. c) Device area versus energy. The markers correspond to the energy stored at the minimum area, while the dotted lines represent energy-area scalability for some microsupercapacitors, [3,43,48,49] on-chip capacitors, [46,47] and our work.

element, whenever the cell is storing a logic "0." In fact, electrochemical reactions are expected to take place either before the creation, or after the dissolution of the conducting filament. **Figure 8**a illustrates the operating regions, in terms of qualitative voltage and current domains, of such dual-behavior RRAM cell.

- II. Our study put into evidence that the faradaic processes happening inside our samples seem not involve the whole volume, as a linear trend of the current peak with the area could not be satisfied when enlarging the device diameter, but was instead verified when connecting multiple devices in parallel (Figure 8c). Consequently, the energy storage mechanism appears to be a "local" phenomenon, possibly limited to the switchable oxide region of the solid electrolyte. As a result, energy capability should be increased by

- maximizing the number of devices connected in parallel, meaning that further downscaling would be beneficial to boost both memory and energy density.

- III. The estimated energy density achievable with our devices peaks around 3.5 pJ  $\mu m^{-2}$  (at  $\nu=160~\rm mV~s^{-1}$ ), while the maximum power density amounts to 80 pW  $\mu m^{-2}$  (for  $\nu=5~\rm V~s^{-1}$ ). The Ragone plot of Figure 8b benchmarks and compares our devices to other state-of-the-art integrated energy storage elements. Remarkably, the energy and power densities extrapolated appear to rival with those of integrated planar supercapacitors. Figure 8c reports stored energy versus sample area, highlighting that the energy could theoretically be linearly increased with the number of devices connected in parallel, up to values comparable to those of integrated planar supercapacitors.

Furthermore, the proposed technology (benchmarked at a minimum area of 0.07  $\mu m^2$ ) provides the added advantage of being much more scalable, opening the possibility of realizing "deep granular supercapacitor" by means of RRAM elements.

IV. Practical measurements of reactions' relaxation times are yet to be quantified for our study. For similar RRAM stacks at voltage ranges close to our CV tests, Tsuruoka et al. reported stable ion concentration coefficients in the order of hundreds of seconds.<sup>[26]</sup> Furthermore, the eligibility of applications might be narrowed down to those who can benefit from relatively low relaxation times. In particular, one can consider that long relaxation times would be required for data storage application with unfrequent reprogramming, while short relaxation times could be sufficient as we address tiers on top of the memory hierarchy which require more frequent refresh or update. However, a comprehensive characterization is still to be performed in order to draw final conclusions on this aspect, as well as a detailed analysis of required relaxation times depending on the specific application.

#### 6. Conclusion

In this work, we explored the new concept of RRAM-based in-memory energy devices, by conducting a preliminary energy storage characterization on state-of-the-art RRAM memory samples. Our study allowed us to confirm the faradaic nature of the processes taking place inside our devices, which exhibit "local" traits. Consequently, the proposed technology offers the advantage of raising both energy and memory density with downscaling. The extrapolated energy and power densities compare with SOA integrated supercapacitor, with the added benefit of being much more scalable. In conclusion, the proposed technology would well adapt to the IMC field, and has the potential of broadening its advantages by adding the energy storage feature inside the memory. Further evaluation is demanded: in particular, aiming to quantify the output voltage, columbic efficiency and experimental energy and power density capability. As a next step, new design solutions where the memory and energy performances are optimized could be explored, in order to bring the technology on the application level.

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### **Conflict of Interest**

The authors declare no conflict of interest.

#### **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Keywords**

dual behavior, energy in memory, RRAM battery

Received: March 23, 2021 Revised: June 24, 2021 Published online: August 19, 2021 2199106x, 2021, 12, Downoaded from https://onlinelibrary.wiley.com/oi/01.01002/welm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Information (https://onlinelibrary.wiley.com/erms-and-conditions) on Wiley Online Library for rules of use of

- [1] A. Wolfgang, M. Brillouët, P. Cogez, M. Graef, B. Huizing, R. Mahnkopf, "More-than-Moore" White Paper. International Technology Roadmap for Semiconductors, www.itrs.net/ITRS201999-2014Mtgs,Presentations&Links/2010ITRS/IRC-ITRS-MtM-v23.pdf. 2010, p. 2, (Accessed: August 2021).

- [2] L. Strambini, A. Paghi, S. Mariani, A. Sood, J. Kalliomäki, P. Järvinen, F. Toia, M. Scurati, M. Morelli, A. Lamperti, G. Barillaro, Nano Energy 2020, 68, 104281.

- [3] V. Sallaz, S. Oukassi, F. Voiron, R. Salot, D. Berardan, J. Power Sources 2020, 451, 227786.

- [4] A. Sebastian, M. L.e Gallo, R. Khaddam-Aljameh, E. Eleftheriou, Nat. Nanotechnol. 2020, 15, 529.

- [5] G. Zhou, Z. Ren, L. Wang, J. Wu, B. Sun, A. Zhou, G. Zhang, S. Zheng, S. Duan, Q. Song, *Nano Energy* 2019, 63, 103793.

- [6] I. K. Jin, J.-Y. Park, B.-H. Lee, S.-B. Jeon, I.-W. Tcho, S.-J. Park, W.-G. Kim, J.-K. Han, S.-W. Lee, S.-Y. Kim, H. Bae, D. Kim, Y.-K. Choi, Nano Energy 2018, 52, 63.

- [7] M. Kim, C. Lee, Y. Song, S.-M. Koo, J.-M. Oh, J. Woo, D. Lee, IEEE Electron Device Lett. 2019, 40, 1622.

- [8] S. Oukassi, A. Bazin, C. Secouard, I. Chevalier, S. Poncet, S. Poulet, J.-M. Boissel, F. Geffraye, J. Brun, R. Salot, in *IEEE Int. Electron Devices Meeting (IEDM)*, 2019, pp. 26.1.1–26.1.4, https://doi.org/10.1109/IEDM19573.2019.899348.

- [9] H. Jung, M. Pedram, in 2010 Design, Automation & Test in Europe Conf. & Exhibition, 2010, pp. 351–356, https://doi.org/10.1109/ DATE.2010.5457180.

- [10] K. Prall, in 2017 IEEE International Memory Workshop (IMW), 2017, pp. 1-5, https://doi.org/10.1109/IMW.2017.7939072.

- [11] J. Lee, Y. Zhang, Q. Dong, W. Lim, M. Saligane, Y. Kim, S. Jeong, J. Lim, M. Yasuda, S. Miyoshi, M. Kawaminami, D. Blaauw, D. Sylvester, *IEEE J. Solid-State Circuits* 2020, 55, 87.

- [12] P. Merolla, J. V. Arthur, R. A-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson1, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, D. S. Modha, *Science* 2014, 345, 668.

- [13] M. Davies, N. Srinivasa, T.-H. Lin, G. Chinya, Y. Cao, S. H. Choday, G. Dimou, P. Joshi, N. Imam, S. Jain, Y. Liao, C.-K. Lin, A. Lines, R. Liu, D. Mathaikutty, S. McCoy, A. Paul, J. Tse, G. Venkataramanan, Y.-H. Weng, A. Wild, Y. Yang, H. Wang, *IEEE Micro* 2018, 38, 82.

- [14] R. Mochida, K. Kouno, Y. Hayata, M. Nakayama, T. Ono, H. Suwa, R. Yasuhara, K. Katayama, in 2019 *IEEE 11th Int. Memory Workshop* (*IMW*), 2019, pp. 1–4, https://doi.org/10.1109/IMW.2019.8739720.

- [15] A. Valentian, F. Rummens, E. Vianello, T. Mesquida, C. Lecat-Mathieu de Boissac, O. Bichler, C. Reita, in 2019 IEEE Int. Electron Devices Meeting (IEDM), IEEE, Piscataway, NJ 2019, pp. 14.3.1–14.3.4, https://doi.org/10.1109/IEDM19573.2019.8993431.

- [16] G. Sassine, C. Cagli, J. Nodin, G. Molas, E. Nowak, IEEE J. Electron Devices Soc. 2018, 6, 696.

- [17] J. Guy, G. Molas, P. Blaise, M. Bernard, A. Roule, G. Le Carval, V. Delaye, A. Toffoli, G. Ghibaudo, F. Clermidy, B. De Salvo, L. Perniola, *IEEE Trans. Electron Devices* 2015, 62, 3482.

- [18] J. Guy, G. Molas, P. Blaise, C. Carabasse, M. Bernard, A. Roule, G. Le Carval, V. Sousa, H. Grampeix, V. Delaye, A. Toffoli, J. Cluzel, P. Brianceau, O. Pollet, V. Balan, S. Barraud, O. Cueto,

2199160x, 2021, 12, Downloaded from https://onlinelibrary.wiley.com/ai/10.1002/aclm.202100297 by CEA National, Wiley Online Library on [17/05/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms-and-conditions) on Wiley Online Library for rules of the Company of the Co

of use; OA articles are governed by the applicable Creative Commons I

- G. Ghibaudo, F. Clermidy, B. de Salvo, L. Perniola, in 2014 *IEEE Int. Electron Devices Meeting*, **2014**, pp. 6.5.1–6.5.4, https://doi.org/10.1109/IEDM.2014.7046997.

- [19] Y. Lu, J. H. Lee, I.-W. Chen, Nanoscale 2017, 9, 12690.

- [20] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, S. Williams, Nanotechnology 2011, 22, 485203.

- [21] H.-S. P. Wong, H.-Y. Lee, S. Yu, Y.-S. Chen, Y. Wu, P.-S. Chen, B. Lee, F. T. Chen, M.-J. Tsai, Proc. IEEE 2012, 100, 1951.

- [22] M. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, Y. Kim, C. Kim, D. H. Seo, S. Seo, U. Chung, I. Yoo, K. Kim, *Nat. Mater.* 2011, 10, 625.

- [23] L. Grenouillet, N. Castellani, A. Persico, V. Meli, S. Martin, O. Billoint, R. Segaud, S. Bernasconi, C. Pellissier, C. Jahan, C. CharpinNicolle, P. Dezest, C. Carabasse, P. Besombes, S. Ricavy, N.-P. Tran, A. Magalhaes-Lucas, A. Roman, C. Boixaderas, T. Magis, M. Bedjaoui, M. Tessaire, A. Seignard, F. Mazen, S. Landis, E. Vianello, G. Molas, F. Gaillard, J. Arcamone, E. Nowak, in 2021 IEEE Int. Memory Workshop (IMW), 2021, pp. 1–4, https://doi.org/10.1109/IMW51353.2021.9439607.

- [24] S. Yu, H.-Y. Chen, B. Gao, J. Kang, H.-S. P. Wong, ACS Nano 2013, 7, 2320.

- [25] I. Valov, E. Linn, S. Tappertzhofenl, S. Schmelzer, J. van den Hurk, F. Lentz, R. Waser, Nat. Commun. 2013, 4, 1771.

- [26] T. Tsuruoka, I. Valov, S. Tappertzhofen, J. Hurk, T. Hasegawa, R. Waser, M. Aono, Adv. Funct. Mater. 2015, 25, 6374.

- [27] S.-S. Sheu, M.-F. Chang, K.-F. Lin, C.-W. Wu, Y.-S. Chen, P.-F. Chiu, C.-C. Kuo, Y.-S. Yang, P.-C. Chiang, W.-P. Lin, C.-H. Lin, H.-Y. Lee, P.-Y. Gu, S.-M. Wang, F. T. Chen, K.-L. Su, C.-H. Lien, K.-H. Cheng, H.-T. Wu, T.-K. Ku, M.-J. Kao, M.-J. Tsai, in 2011 *IEEE Int. Solid State Circuits Conf.*, 2011, pp. 200–202, https://doi.org/10.1109/ISSCC.2011.5746281.

- [28] R. Fackenthal, M. Kitagawa, W. Otsuka, K. Prall, D. Mills, K. Tsutsui, J. Javanifard, K. Tedrow, T. Tsushima, Y. Shibahara, G. Hush, in *IEEE Int. Solid State Circuits Conf. Digest of Technical Papers (ISSCC)* 2014, pp. 338–339, https://doi.org/10.1109/ISSCC.2014.6757460.

- [29] D. Alfaro Robayo, G. Sassine, Q. Rafhay, G. Ghibaudo, G. Molas, E. Nowak, IEEE Trans. Electron Devices 2019, 66, 3318.

- [30] C. Nail, G. Molas, P. Blaise, B. Sklenard, R. Berthier, M. Bernard, L. Perniola, G. Ghibaudo, C. Vallée, IEEE Trans. Electron Devices 2017. 64, 4479.

- [31] C. Nail, G. Molas, P. Blaise, G. Piccolboni, B. Sklenard, C. Cagli, M. Bernard, A. Roule, A. Azzaz, E. Vianello, C. Carabasse, R. Berthier, D. Cooper, C. Pelissier, T. Magis, G. Ghibaudo, C. Vallée, D. Bedeau, O. Mosendz, B. De Salvo, L. Perniola, in *IEEE Int. Electron Devices Meeting (IEDM)*, 2016 pp. 4.5.1–4.5.4, https://doi.org/10.1109/IEDM.2016.7838346.

- [32] M. Tada, T. Sakamoto, Y. Tsuji, N. Banno, Y. Saito, Y. Yabe, S. Ishida, M. Terai, S. Kotsuji, N. Iguchi, M. Aono, H. Hada, N. Kasai, in 2017

- *IEEE Int. Electron Devices Meeting (IEDM)*, **2009**, pp. 1–4, https://doi.org/10.1109/IEDM.2009.5424287.

- [33] M. Tada, T. Sakamoto, N. Banno, M. Aono, H. Hada, N. Kasai, IEEE Trans. Electron Devices 2010, 57, 1987.

- [34] N. Banno, T. Sakamoto, H. Hada, N. Kasai, N. Iguchi, H. Imai, S. Fujieda, T. Ichihashi, T. Hasegawa, M. Aono, in 2009 IEEE Int. Reliability Physics Symposium, 2009, pp. 395–399, https://doi. org/10.1109/IRPS.2009.5173285.

- [35] N. Banno, T. Sakamoto, N. Iguchi, H. Sunamura, K. Terabe, T. Hasegawa, M. Aono, IEEE Trans. Electron Devices 2008, 55, 3283.

- [36] G. Sassine, C. Nail, P. Blaise, B. Sklenard, M. Bernard, R. Gassilloud, A. Marty, M. Veillerot, C. Vallée, E. Nowak, G. Molas, Adv. Electron. Mater. 2019, 2, 1800658.

- [37] A. J. Bard, R. Parsons, J. Jordan, Standard Potentials in Aqueous Solution, CRC Press, Boca Raton, FL 1985.

- [38] S. Tappertzhofen, R. Waser, I. Valov, ChemElectroChem 2014, 1, 1287.

- [39] P. Zanello, Inorganic Electrochemistry, Theory, Practice and Application, The Royal Society of Chemistry, Cambridge 2003.

- [40] J. Sandrini, L. Grenouillet, V. Meli, N. Castellani, I. Hammad, S. Bernasconi, F. Aussenac, S. Van Duijn, G. Audoit, M. Barlas, J. F. Nodin, O. Billoint, G. Molas, R. Fournel, E. Nowak, F. Gaillard, C. Cagli, in 2019 IEEE Int. Electron Devices Meeting (IEDM) 2019, pp. 30.5.1–30.5.4, https://doi.org/10.1109/IEDM19573.2019.899348.

- [41] J. Guy, G. Molas, E. Vianello, F. Longnos, S. Blanc, C. Carabasse, M. Bernard, J. F. Nodin, A. Toffoli, J. Cluzel, P. Blaise, P. Dorion, O. Cueto, H. Grampeix, E. Souchier, T. Cabout, P. Brianceau, V. Balan, A. Roule, S. Maitrejean, L. Perniola, B. De Salvo, in 2013 IEEE Int. Electron Devices Meeting 2013, pp. 30.2.1–30.2.4, https://doi.org/10.1109/IEDM.2013.6724722.

- [42] T. Tsuruoka, I. Valov, C. Mannequin, T. Hasegawa, R. Waser, M. Aono, *Jpn. J. Appl. Phys.* 2016, 55, 06GJ09.

- [43] Z.-S. Wu, K. Parvez, X. Feng, K. Müllen, Nat. Commun. 2013, 4, 2487

- [44] S. S. Delekta, K. H. Adolfsson, N. B. Erdal, M. Hakkarainen, M. Östling, J. Li, Nanoscale 2019, 11, 10172.

- [45] S. Zheng, X. Tang, Z.-S. Wu, Y.-Z. Tan, S. Wang, C. Sun, H.-M. Cheng, X. Bao, ACS Nano 2017, 11, 2171.

- [46] P. Renz, M. Kaufmann, M. Lueders, B. Wicht, IEEE Solid-State Circuits Lett. 2019, 2, 236.

- [47] G. Pillonnet, N. Jeanniot, in CIPS 2016, 9th Int. Conf. on Integrated Power Electronics Systems 2016, pp. 1–5.

- [48] D. Pech, M. Brunet, P.-L. Taberna, P. Simon, N. Fabre, F. Mesnilgrente, V. Conédéra, H. Durou, J. Power Sources 2010, 195, 1366

- [49] W. Gao, N. Singh, L. Song, Z. Liu, A. L. M. Reddy, L. Ci, R. Vajtai, Q. Zhang, B. Wei, P. M. Ajayan, Nat. Nanotechnol. 2011, 6, 496.