## Influence of substrate resistivity on porous silicon small-signal RF properties

Geoffroy Godet, Emmanuel Augendre, Jose Lugo, Hélène Jacquinot, Frederic Xavier-Paul Gaillard, Thomas Lorne, Emmanuel Rolland, Thierry Taris, Florence Servant

## ▶ To cite this version:

Geoffroy Godet, Emmanuel Augendre, Jose Lugo, Hélène Jacquinot, Frederic Xavier-Paul Gaillard, et al.. Influence of substrate resistivity on porous silicon small-signal RF properties. IEEE Transactions on Electron Devices, 2020, 67 (11), pp.4654-4657. 10.1109/TED.2020.3023063. cea-03676642

## HAL Id: cea-03676642 https://cea.hal.science/cea-03676642

Submitted on 24 May 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Influence of Substrate Resistivity on Porous Silicon Small-Signal RF Properties

Geoffroy Godet, Emmanuel Augendre<sup>®</sup>, *Member, IEEE*, Jose Lugo-Alvarez<sup>®</sup>, Hélène Jacquinot, Frédéric X. Gaillard, Thomas Lorne, Emmanuel Rolland, Thierry Taris<sup>®</sup>, *Member, IEEE*, and Florence Servant

Abstract—This article provides guidelines to design porous silicon (PS) layers regarding optimization of small-signal properties in passive structures for radio frequency (RF): insertion loss and crosstalk. Results are based on high-frequency measurements on 200-mm wafers and electromagnetic simulations up to 40 GHz. Using substrate resistivity below 1  $\Omega$  cm allows the best tradeoff with minimized PS thickness.

Index Terms—Crosstalk, linear attenuation coefficient, porous silicon (PS), S-parameters, substrate resistivity.

Fig. 1. Cross-sectional imaging of the Si/PS interface for two distinct substrate resistivities, using scanning electron microscopy.

#### I. INTRODUCTION

ITH the advent of pervasive mobile and wireless devices, porous silicon (PS), a long studied material [1]–[3], attracts a renewed interest as blanket or local substrate material for radio frequency (RF) applications [4]–[6]: it is compatible with Si technology and offers lower permittivity and higher resistivity than Si.

The latter helps to reduce signal propagation loss (attenuation). Using PS benefits a wide range of devices including coplanar waveguides (CPWs), inductors, and filters [6]. There are reports indicating that for a given device

Manuscript received June 16, 2020; revised August 28, 2020; accepted September 3, 2020. Date of publication September 23, 2020; date of current version October 22, 2020. This work was supported in part by European Commission, French State and Auvergne-Rhône Alpes Region through the funding of Electronic Components and Systems for European Leadership (ECSEL) Project BEYOND5 part of Important Project of Common European Interest (IPCEI) Microelectronics and in part by the French Nano2022 Program. The review of this article was arranged by Editor H. Wong. (Corresponding author: Emmanuel Augendre.)

Geoffroy Godet was with Univ. Grenoble Alpes, F-38000 Grenoble, France, and also with CEA, LETI, MINATEC Campus, F-38054 Grenoble, France. He is now with Easii-IC, 38100 Grenoble, France (e-mail: geoffroy.godet@easii-ic.com).

Emmanuel Augendre, Jose Lugo-Alvarez, Hélène Jacquinot, Frédéric X. Gaillard, Thomas Lorne, Emmanuel Rolland, and Florence Servant are with Univ. Grenoble Alpes, F-38000 Grenoble, France, and also with CEA, LETI, MINATEC Campus, F-38054 Grenoble, France (e-mail: emmanuel.augendre@cea.fr; jose.lugo@cea.fr; helene.jacquinot@cea.fr; frederic-x.gaillard@cea.fr; thomas.lorne@cea.fr; emmanuel.rolland@cea.fr; florence.servant@cea.fr).

Thierry Taris is with IMS, CNRS UMR5218, 33405 Talence, France, and also with Université Sciences et Technologies - Bordeaux 1, 33400 Talence, France (e-mail: thierry.taris@ims-bordeaux.fr).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2020.3023063

geometry, increased PS thickness improves device performance [7], [8]. However, the systematic effect of starting bulk silicon resistivity on RF small-signal properties has not yet been described with PS.

In this article, we report for the first time on the impact of silicon resistivity on substrate loss of CPW made on PS. First, we fabricated CPW on PS variants (made with different thicknesses on silicon with variable resistivity). We then measured the S-parameters of CPW fabricated on these substrates up to 40 GHz. A simple high frequency structure simulator (HFSS) [9] model reproduces these measurement results. This model enables predicting the impact of substrate resistivity on CPW substrate loss and crosstalk, allowing to draw guidelines for the design of future RF PS layers.

#### II. EXPERIMENTAL

#### A. PS Fabrication

We prepared blanked PS layers starting from 200-mm p-type doped silicon wafers with resistivity in the  $1\text{--}2\text{-}\Omega$  · cm and  $5\text{--}10\text{-}\Omega$  · cm ranges, respectively. For each resistivity, Si substrates were electrochemically anodized in hydrofluoric acid (35%) with isopropanol as surfactant and a current density of 14 mA/cm². The thickness and porosity of these layers were determined using differential weighting and cross section scanning electron microscopy. Fig. 1 illustrates the morphology of these layers. For each resistivity, layers of 12- and 20- $\mu$ m thickness were fabricated. In all samples, porosity was estimated close to 50%.

#### B. CPW Fabrication

After PS formation, a thin (400 nm) silicon dioxide layer was deposited by plasma-enhanced chemical vapor deposition

0018-9383 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 2. Material stack used in the fabrication of CPW on PS.

at 260 °C. The wafers were then coated with 100 nm of titanium and 1  $\mu$ m of gold. Photolithography and wet etching lead to the patterning of this metal stack into CPW transmission lines (see Fig. 2). RF probing pads with 100- $\mu$ m pitch allow CPW connection.

# C. S-Parameter Measurements and Parameter Extraction

Scattering parameters were measured between 100 MHz and 40 GHz using an Anritsu 37369A Vectorial Network Analyzer and ground–signal–ground (GSG) probes from Cascade. Measurements were carried out on different CPW pairs differing only by their lengths (500 and 1500  $\mu$ m). RF pad parasitic contributions were removed using Mangan's method proposed in [10]. Losses were calculated as follows:

$$\alpha_C = R/2Z_0 \tag{1}$$

$$\alpha_G = GZ_0/2 \tag{2}$$

$$\alpha_{\text{total}} = \alpha_G + \alpha_C \tag{3}$$

where  $\alpha_C$  and  $\alpha_G$  are the respective contributions of metallic conductor and substrate material to  $\alpha_{\rm total}$ , the total loss of the CPW. R and G are the linear resistance and conductance values of the *resistance-inductance-capacitance-conductance* (RLCG) equivalent model of the transmission line and  $Z_0$  relates to its characteristic impedance.

#### III. RESULTS AND DISCUSSION

#### A. Choice of CPW Dimensions

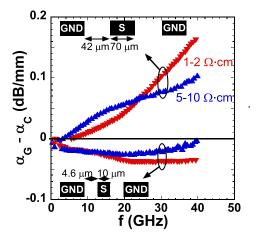

Losses were extracted on two contrasting CPW geometries: a narrow signal line with small signal-to-ground gap (S/G = 10  $\mu$ m/4.6  $\mu$ m) and a wide signal line with a large signal-to-ground gap (S/G = 70  $\mu$ m/42  $\mu$ m). Both CPW lines have a 50- $\Omega$  characteristic impedance for a 3-k $\Omega$  · cm Si substrate without PS. Fig. 3 presents the results obtained on two different Si substrate resistivities.

For the compact CPW, it is noticeable that conductor contribution dominates losses. This originates both from the higher linear resistance of the signal line and from reduced substrate losses, as electromagnetic fields are mainly confined within the low-loss PS layer. In contrast, in the wide signal-line and large gap configuration, the substrate component (including bulk Si contribution) determines CPW linear loss. For this reason, the investigation of substrate resistivity impact focuses on the larger layout.

### B. HFSS Electromagnetic Simulations

Different configurations were implemented in the HFSS software [9], using parameter values listed in Tables I and II.

Fig. 3. Experimental difference between conductor and substrate contribution to propagation linear loss versus frequency, on  $20-\mu$ m-thick PS layers, as a function of CPW geometry and substrate resistivity.

TABLE I STACK DESCRIPTION

| Thickness (μm) |     |                  |       |              |  |  |  |

|----------------|-----|------------------|-------|--------------|--|--|--|

| Au Ti          |     | SiO <sub>2</sub> | PS    | Si Substrate |  |  |  |

| 1.0            | 0.1 | 0.4              | 5→200 | 700          |  |  |  |

TABLE II

ELECTRICAL PROPERTIES

| Intrinsic properties at 824 MHz     |           |           |                  |                      |         |  |  |

|-------------------------------------|-----------|-----------|------------------|----------------------|---------|--|--|

| Layer                               | Au        | Ti        | SiO <sub>2</sub> | PS                   | Si      |  |  |

| $\mathbf{\mathcal{E}}_{\mathrm{r}}$ | 1.0       | 1.0       | 3.9              | 4.5                  | 11.9    |  |  |

| ρ (Ω·cm)                            | 2.30·10-6 | 4.17·10-5 | 1.0.1018         | 10 <sup>6</sup> ·ρsi | 10-2→50 |  |  |

In these structures, the substrate resistivity was chosen to be 1.5 and 7.5  $\Omega \cdot$  cm for hardware in the respective 1–2- $\Omega \cdot$  cm and 5–10- $\Omega \cdot$  cm resistivity ranges. PS layer resistivity value was set in agreement with [11]. The relative permittivity value of 4.5 originates from [12] and best describes the permittivity around 50% porosity.

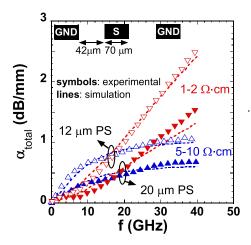

Fig. 4 compares measured and simulated losses as a function of frequency, on CPW structures with the same dimensions: 70- $\mu$ m-wide signal line, 308- $\mu$ m-wide surrounding ground lines separated by a 42- $\mu$ m-wide gap. Two variants of silicon resistivity are combined with two variants of PS layer thickness (12 and 20  $\mu$ m).

The loss values in this work are of the same order of magnitude as literature data with similar stacks: in [7], losses of 1.5 dB/mm at 40 GHz have been reported on 15- $\mu$ m-thick PS on 1–3- $\Omega$ ·cm Si and with a gap of 2.5  $\mu$ m. In this work, this value is obtained with a 20- $\mu$ m PS layer. The difference is due to CPW geometry: in our case, this was selected in order to maximize substrate impact, not to optimize performance (which would require narrower line-to-ground gaps as in [7]).

The obtained trend agrees with literature data showing that increasing PS thickness yields attenuated losses [7]. Comparing at 16 GHz, increasing PS thickness from

Fig. 4. Total linear propagation loss as a function of frequency, on 12- and 20-  $\mu m$  PS layers, for two different substrate resistivities. Symbols denote measurement results and dashed lines denote HFSS simulation output.

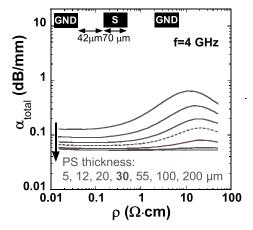

Fig. 5. HFSS simulated total attenuation as a function of substrate resistivity, for various PS thickness values, at 4 GHz.

12 to 20  $\mu$ m decreases attenuation coefficients from 0.8 to 0.4 dB/mm.

The change in substrate doping has a strong impact on the attenuation dependence on frequency. Below 16 GHz, for a given PS thickness, it is more favorable to use 1.5 than 7.5  $\Omega \cdot$  cm. This trend reverses at higher frequencies, especially with thinner PS.

In all cases, the simulations capture the observed dependence on PS thickness and Si substrate resistivity. In order to have a better insight of these trends, HFSS simulations were performed to investigate wider parameter ranges.

#### C. Simulated Dependence of Loss on Resistivity

Fig. 5 presents simulated attenuation coefficients for PS layers between 5- and 200- $\mu$ m thickness, on Si substrates in the 10–50- $\Omega$  · cm resistivity range, at a fixed frequency of 4 GHz.

For those thickness and resistivity ranges, the variation of the characteristic impedance of the chosen coplanar line is between 30 and 80  $\Omega$ .

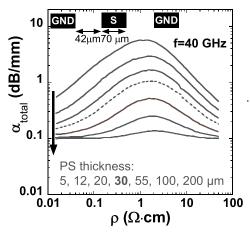

Fig. 6. HFSS simulated total attenuation as a function of substrate resistivity, for various PS thickness values, at 40 GHz.

Both PS thickness and substrate resistivity appear to influence the observed trends.

For each PS layer thickness, attenuation reaches a peak value in the 10–20- $\Omega$  · cm resistivity range.

- For higher resistivity values, eddy currents fade, reducing losses.

- For lower resistivity values, the electromagnetic field is mainly confined into the PS layer, which also dims eddy currents.

The  $10-20-\Omega \cdot \text{cm}$  resistivity range leads to a worst case regime where both mechanisms are most ineffective.

The effect of substrate resistivity is amplified in the case of thin PS layers. Conversely, substrate resistivity influence on losses decreases as soon as PS layer thickness reaches a sufficiently high value (which is around the same order of magnitude as CPW signal-to-ground spacing).

The exercise was repeated at 40 GHz. Fig. 6 summarizes the corresponding main results.

Worst case attenuation values appear in the  $1-2-\Omega \cdot cm$  resistivity range, which is one order of magnitude lower than the 4 GHz case.

In that resistivity range, the peak attenuation value increases with frequency (about 10-fold higher than at 4 GHz). The dependence of the peak attenuation value on PS layer thickness seems relatively unchanged.

Minimum attenuation appears for the thickest PS layers and is weakly dependent on substrate doping. This minimum level is higher than in the case of 4 GHz operation. Both observations can be explained by the fact that metallic conductor contribution determines the minimum value and skin effect sets its frequency dependence.

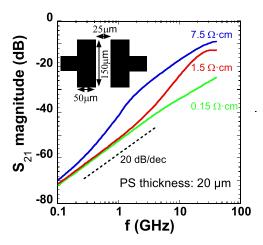

#### D. Simulated Dependence of Crosstalk on Resistivity

Fig. 7 compares the simulated magnitude of  $S_{21}$  versus frequency between 100 MHz and 40 GHz, for three different substrate resistivities, with 20- $\mu$ m-thick PS layer, on a coplanar test structure with 25- $\mu$ m coupling distance and 150- $\mu$ m coupling width, as described in the inset of Fig. 7.

While  $S_{21}$  bears a weak dependence on substrate resistivity below 1 GHz, only the  $0.15-\Omega \cdot \text{cm}$  resistivity case shows

Fig. 7. HFSS simulated  $S_{21}$  magnitude as a function of frequency for three different substrate resistivities, using a 20- $\mu$ m PS layer, extracted on a coplanar structure.

a 20-dB/decade capacitive coupling behavior over the whole frequency range. It is thus mandatory to use low-resistivity (<1  $\Omega$ ·cm) silicon in order to minimize 25- $\mu$ m-range crosstalk up to 40 GHz.

#### E. Guidelines for PS Layer Design

At a given frequency and for a given PS layer thickness, Figs. 5 and 6 suggest that a given loss target value could be achieved with different substrate resistivities in the  $10^{-2}$ –50- $\Omega$ · cm range.

However, it might be preferable to use low-resistivity silicon as a default starting material.

- It requires relatively thin PS layers for low-frequency operation.

- 2) It contributes in minimizing crosstalk over the whole frequency range.

- 3) It allows keeping the same PS features, as changing Si resistivity can affect PS morphology [13].

#### IV. CONCLUSION

This article reports the first systematic evaluation of substrate resistivity influence on the attenuation coefficient of CPWs fabricated on various thicknesses of PS.

First, we fabricated CPW on PS variants (with different thicknesses and made on silicon substrates with variable resistivity). We then measured the S-parameters of CPW fabricated on these substrates up to 40 GHz. HFSS simulation reproduces these measurement results. This enables the

prediction of the substrate resistivity impact on CPW substrate loss and crosstalk.

At each frequency, there is a substrate resistivity range in which attenuation is maximal, suggesting that either low or high resistivity could provide well-controlled attenuation values with minimum PS thickness. At the same time, simulations suggest that low substrate resistivity is necessary to minimize crosstalk up to high frequencies.

While  $1-\Omega \cdot$  cm substrate resistivity is suitable for PS to operate in the sub-6-GHz domain, we recommend using lower resistivity silicon if the PS layers are meant to be compatible with a wider range of operating frequencies.

#### REFERENCES

- A. Uhlir, "Electrolytic shaping of germanium and silicon," *Bell Syst. Tech. J.*, vol. 35, no. 2, pp. 333–347, Mar. 1956, doi: 10.1002/j.1538-7305.1956.tb02385.x.

- [2] D. R. Turner, "Electropolishing silicon in hydrofluoric acid solutions," J. Electrochem. Soc., vol. 105, no. 7, p. 402, 1958, doi: 10.1149/1.2428873.

- [3] X. G. Zhang, S. D. Collins, and R. L. Smith, "Porous silicon formation and electropolishing of silicon by anodic polarization in HF solution," *J. Electrochem. Soc.*, vol. 136, no. 5, pp. 1561–1565, May 1989, doi: 10.1149/1.2096961.

- [4] M. Rack, Y. Belaroussi, K. Ben Ali, G. Scheen, B. Kazemi Esfeh, and J.-P. Raskin, "Small- and large-signal performance up to 175 °C of low-cost porous silicon substrate for RF applications," *IEEE Trans. Electron Devices*, vol. 65, no. 5, pp. 1887–1895, May 2018, doi: 10.1109/TED.2018.2818466.

- [5] Y. Belaroussi et al., "High quality silicon-based substrates for microwave and millimeter wave passive circuits," Solid-State Electron., vol. 135, pp. 78–84, Sep. 2017, doi: 10.1016/j.sse.2017.06.028.

- [6] G. Gautier and P. Leduc, "Porous silicon for electrical isolation in radio frequency devices: A review," *Appl. Phys. Rev.*, vol. 1, no. 1, Mar. 2014, Art. no. 011101, doi: 10.1063/1.4833575.

- [7] R. J. Welty, S. H. Park, P. M. Asbeck, K.-P.-S. Dancil, and M. J. Sailor, "Porous silicon technology for RF integrated circuit applications," in *Top. Meeting Silicon Monolithic Integr. Circuits RF Syst. Dig. Papers*, 1998, pp. 160–163, doi: 10.1109/SMIC.1998.750212.

- [8] J. Billoué, G. Gautier, and L. Ventura, "Integration of RF inductors and filters on mesoporous silicon isolation layers," *Phys. Status Solidi A*, vol. 208, no. 6, pp. 1449–1452, Jun. 2011, doi: 10.1002/pssa.201000027.

- [9] Description of the Ansys HFSS Simulation Software. Accessed: Jan. 2020. [Online]. Available: https://www.ansys.com/products/electronics/ansys-hfss

- [10] A. M. Mangan, S. P. Voinigescu, M.-T. Yang, and M. Tazlauanu, "De-embedding transmission line measurements for accurate modeling of IC designs," *IEEE Trans. Electron Devices*, vol. 53, no. 2, pp. 235–241, Feb. 2006, doi: 10.1109/TED.2005.861726.

- [11] S. Ménard, A. Fèvre, J. Billoué, and G. Gautier, "P type porous silicon resistivity and carrier transport," J. Appl. Phys., vol. 118, no. 10, Sep. 2015, Art. no. 105703, doi: 10.1063/1.4930222.

- [12] P. Sarafis and A. G. Nassiopoulou, "Dielectric properties of porous silicon for use as a substrate for the on-chip integration of millimeterwave devices in the frequency range 140 to 210 GHz," *Nanosc. Res. Lett.*, vol. 9, no. 1, p. 418, Dec. 2014, doi: 10.1186/1556-276X-9-418.

- [13] G. Korotcenkov and B. K. Cho, "Silicon porosification: State of the art," Crit. Rev. Solid State Mater. Sci., vol. 35, no. 3, pp. 153–260, Aug. 2010, doi: 10.1080/10408436.2010.495446.