## Gate spacers etching of Si\_3N\_4 using cyclic approach for 3D CMOS devices

Valentin Bacquie, Aurelien Tavernier, Francois Boulard, Olivier Pollet, Nicolas Posseme

#### ▶ To cite this version:

Valentin Bacquie, Aurelien Tavernier, Francois Boulard, Olivier Pollet, Nicolas Posseme. Gate spacers etching of Si\_3N\_4 using cyclic approach for 3D CMOS devices. Journal of Vacuum Science & Technology A, 2021, 39, pp.033005. 10.1116/6.0000871. cea-03343549

### HAL Id: cea-03343549 https://cea.hal.science/cea-03343549

Submitted on 14 Sep 2021

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Gate spacers etching of Si<sub>3</sub>N<sub>4</sub> using cyclic approach for 3D CMOS devices

Cite as: J. Vac. Sci. Technol. A 39, 033005 (2021); https://doi.org/10.1116/6.0000871 Submitted: 17 December 2020 . Accepted: 15 March 2021 . Published Online: 06 April 2021

Valentin Bacquié, Aurélien Tavernier, François Boulard, Olivier Pollet, and Nicolas Possémé

# Gate spacers etching of Si<sub>3</sub>N<sub>4</sub> using cyclic approach for 3D CMOS devices

Cite as: J. Vac. Sci. Technol. A **39**, 033005 (2021); doi: 10.1116/6.0000871 Submitted: 17 December 2020 · Accepted: 15 March 2021 · Published Online: 6 April 2021

Valentin Bacquié, a) Aurélien Tavernier, François Boulard, Olivier Pollet, and Nicolas Possémé

#### **AFFILIATIONS**

Univ. Grenoble Alpes, CEA, LETI, Grenoble F-38000, France

a)Electronic mail: valentin.bacquie@cea.fr

#### **ABSTRACT**

In this work, we optimize a  $CH_3F/O_2/He/SiCl_4$  chemistry to etch silicon nitride gate spacers for 3D CMOS devices in a 300 mm inductively coupled plasma reactor. The chemistry has high directivity and high selectivity to Si and  $SiO_2$ . A cyclic approach, which alternates this chemistry with a  $CH_2F_2/O_2/CH_4/He$  plasma, is investigated. Using *quasi in situ* x-ray photoelectron spectroscopy and ellipsometry measurements, etching mechanisms are proposed to explain the results obtained. As a result of process optimization, silicon nitride spacers with vertical profile and a small critical dimension loss of 3 nm as well as complete spacers removal on sidewalls of the active area are obtained on 3D patterns, confirming the advantages of this approach.

Published under license by AVS. https://doi.org/10.1116/6.0000871

#### I. INTRODUCTION

As the gate length of the complementary metal oxide semiconductor (CMOS) transistor is reduced, the spacer's etching gradually becomes more constrained. In particular, different 3D architectures, such as Fin Field Effect Transistor (FinFET) or stacked nanowire, are currently developed to limit the short channel effect or the tunneling effect and to improve device performance. With these new architectures, a good control of critical dimensions (CDs) with an absence of foot at the bottom of the gate spacers as well as a minimal Si/SiGe recess is mandatory to achieve good device performances. In addition, parasitic spacers several tens of nanometers high located on the side of the active area have to be totally removed by an over etch with a high selectivity to Si and SiO<sub>2</sub>.

The primary function of spacers is to electrically isolate the gate from the source and drain. Silicon nitride  $(Si_3N_4)$  is used in the amorphous state for the gate spacers of CMOS transistors. Etching of  $Si_3N_4$  has been widely studied. It is generally done by fluorocarbon  $C_xF_y$  (Refs. 3–6) or hydrofluorocarbon  $C_xH_yF_z$  (Refs. 7–15) chemistries. Fluorine-rich gases such as  $CF_4$ ,  $C_4F_8$ , or  $CHF_3$  with a high  $Si_3N_4$  etch rate of about 30 nm min<sup>-1</sup> were investigated. However, these chemistries do not have either sufficient selectivity to  $Si/SiO_2$  or too much lateral etching to be suitable for 3D spacer etching. Even a chemistry with infinite selectivity, like  $CF_4/CH_4$ , shows limitations by the formation of a large foot during spacers etching. <sup>16</sup>

The addition of  $O_2$  to hydrofluorocarbon chemistry has also been investigated. Oxygen helps to reduce the concentration of fluorocarbon radicals like  $CF_x$  by forming volatile species such as CO,  $CO_2$ , or  $COF_2$  and enhance  $Si_3N_4$  etching. Hydrogen from incident hydrofluorocarbon tends to increase the etching rate of  $Si_3N_4$  compared to fluorocarbon without hydrogen by the possible reaction of volatile species, such as HCN. Moreover, it scavenges fluorine from the deposited film, reducing its fluorine content.

A way to obtain good spacers profile with no foot and no parasitic spacers is to increase the ion bombardment energy. Indeed, highly energetic ions allow for a vertical distribution of species participating in the etching process. However, it can induce damage and implantation leading to crystalline silicon (c-Si) consumption, also called Si-recess, after cleaning. <sup>20–23</sup>

To address spacers' etching challenges, different solutions are proposed in the literature. Pulsed plasma approaches show some reduction of plasma induced damage (0.5 nm c-Si recess) by adjusting  $CF_x$  radical densities in hydrofluorocarbon chemistry at low duty cycle. Another approach is to modify  $\mathrm{Si_3N_4}$  using light ions followed by selective removal of the modified layer. Both techniques show high selectivity and limited c-Si recess for 2D applications. They could be used for 3D architectures but would need significant optimization.

Hydrofluorocarbon chemistry with O<sub>2</sub> addition is actually used in the industry for spacers etching applications and could be a candidate to address the 3D application's needs. <sup>24</sup> Possémé *et al.* proposed to add tetrachlorosilicon (SiCl<sub>4</sub>) to a CH<sub>3</sub>F/O<sub>2</sub>/CH<sub>4</sub>/He chemistry. <sup>16</sup> They show, at low percentage of SiCl<sub>4</sub>, selective deposition of oxide layer preferentially on polycrystalline silicon (poly-Si) compared to Si<sub>3</sub>N<sub>4</sub>. Further studies have shown that CH<sub>3</sub>F/O<sub>2</sub> ratios between 1 and 2 are able to etch Si<sub>3</sub>N<sub>4</sub> while minimizing Si consumption thanks to the formation of an SiO<sub>x</sub>F<sub>y</sub> layer on poly-Si. <sup>24</sup>

Oxide deposition on Si only is no longer sufficient when it comes to 3D architectures. The lateral growth of the oxide on Si by the action of the  $CH_3F$ -based chemistry forms a passivation layer, which prevents the  $Si_3N_4$  parasitic spacers etching. Multistep cycling with a second chemistry that is more isotropic and selective to c-Si makes it possible to continuously etch the  $Si_3N_4$  parasitic spacers while preserving gate spacers' CDs and limiting Si-recess on the active area.

Pollet *et al.* showed interest in this approach for parasitic spacers etching with a limited c-Si consumption (3–4 nm). However, a significant CD loss points out the need for improvement. Moreover, it is necessary to understand oxide deposition mechanisms with  $SiCl_4$  addition to  $CH_3F$ -based chemistry and its subsequent etch in order to have good process control with this cyclic approach.<sup>29</sup>

In this paper, the process parameters of CH<sub>3</sub>F/O<sub>2</sub>/He/SiCl<sub>4</sub> plasma are studied in order to improve the cyclic process. First, deposition/etch kinetics, O<sub>2</sub>/SiCl<sub>4</sub> ratio, and source power's influence are studied on blanket wafers. Then, *quasi in situ* x-ray photoelectron spectroscopy (XPS) characterization provides insight into the composition of the layers present on the surface and is used to propose etching and deposition mechanisms. Finally, cycling optimization results are discussed and applied on 3D spacer patterns.

#### II. EXPERIMENTAL SETUP

#### A. Materials

$\rm Si_3N_4$  etch rate studies are conducted on 300 mm silicon blanket wafers coated with 55 and 140 nm thick  $\rm Si_3N_4$ . Nitride films are deposited by low pressure chemical vapor deposition (LPCVD) at 750 °C on 10.5 nm thermal oxide and silicon bulk. C-Si etch experiments are performed on  $2\times2~\rm cm^2$  samples of c-Si coming from fully depleted silicon on insulator (FDSOI) wafers with 16 nm of c-Si deposited over 145 nm of  $\rm SiO_2$  and silicon bulk. Samples are placed at the center of a silicon carrier wafer and fixed with a kapton tap.

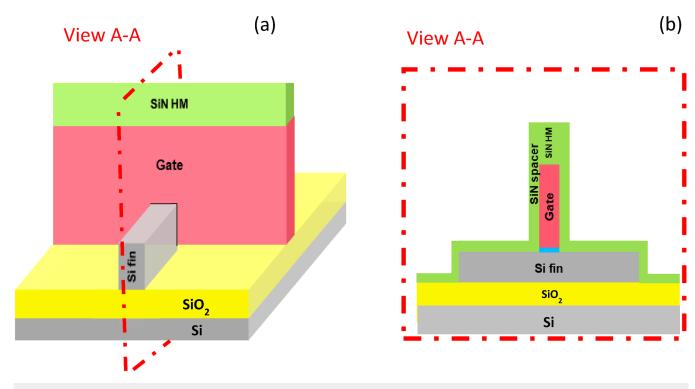

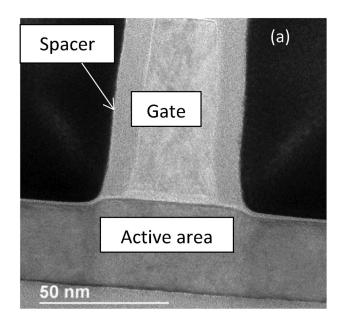

Patterned wafers are used to optimize the cyclic hydrofluoro-carbon chemistry. The stack and architecture are presented in Fig. 1. The substrate consists of an FDSOI stack with 36 nm c-Si active area deposited over 145 nm of SiO<sub>2</sub> on silicon bulk. The gate is then deposited over this stack. It is composed of 70 nm poly-Si deposited by LPCVD with a gate oxide of 3 nm SiO<sub>2</sub>. An Si<sub>3</sub>N<sub>4</sub> hard mask is deposited by plasma enhanced chemical vapor deposition over the gate. Finally, the spacer consists of an 11.5 nm Si<sub>3</sub>N<sub>4</sub> layer deposited conformally by plasma enhanced atomic layer deposition at 630 °C over the whole 3D pattern architecture [see the cut view A-A in Fig. 1(b)].

#### B. Etching setup and chemistries

The etching equipment used is a LamResearch\* 300 mm Kiyo  $FX^{TM}$  Inductively Coupled Plasma (ICP) reactor operating at 13.56 MHz for both source and bias generators. The wafer is electrostatically clamped and is temperature-controlled by helium circulation. After etching and between each wafer, the reactor chamber is cleaned and its walls are coated using  $SiCl_4/O_2$  chemistry.

Two etching chemistries are studied. The first one is a CH $_3$ F-based chemistry with CH $_3$ F/O $_2$ /He at 200/200/120 sccm and addition of a small amount of SiCl $_4$  (2 sccm). Bias voltage, pressure, source power, and temperature are set at 250 V $_{\rm bias}$ , 90 mTorr, 400 W, and 50 °C, respectively. The second one is a CH $_2$ F $_2$ -based chemistry with CH $_2$ F $_2$ /O $_2$ /CH $_4$ /He at 95/63/20/50 sccm and bias voltage, pressure, source power, and temperature set at 100 V $_{\rm bias}$ , 40 mTorr, 400 W, and 60 °C. The cyclic process consists of these two alternating chemistries. At the end of the dry etching process, a wet etch based on hydrofluorydric acid (HF) diluted to 1% during 30 s is applied to clean the wafers.

#### C. Characterization setup

XPS measurements are conducted in a Thermo Fisher Scientific® Spectroscopy ARXPS Theta300<sup>TM</sup> tool operating with a monochromatic Al Kα x-ray source at 1486 eV. Eight incidence angles are used with a range between 23.75° and 76.25°. The smallest angle of analysis corresponds to a probed depth thickness of 8-10 nm. The largest angle corresponds to an extreme surface analysis of the first nanometers. Measurements are carried out at 0.1 eV step, 100 eV pass energy, and 500 ms dwell time. Flood gun is used to compensate charging due to the material being dielectric. This technique is coupled with an Adixen<sup>TM</sup> transfer case for *quasi* in situ experiments keeping the wafer under vacuum after etching. The spectra positioning strategy is carried out using the reference peak of carbon at 284.5 eV. Thickness measurements are done by spectroscopic ellipsometry with two instruments: the Atlas<sup>TM</sup> III from Nanometrics\* and the RC2<sup>TM</sup> from J.A. Woollam\* in the wavelength ranges from 400 to 1000 nm. Atlas III is used in the case of a full blanket wafer while RC2 is used for  $2 \times 2 \text{ cm}^2$ samples. Ellipsometric model uncertainties are estimated at 1 nm.

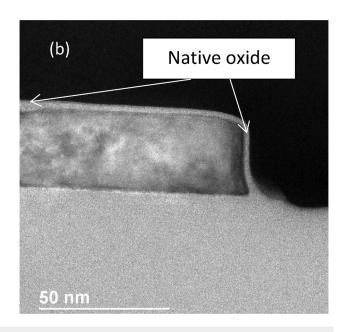

Transmission electron microscopy (TEM) is performed to obtain cross-view images of the 3D architecture samples after etching. The processing of these samples is done by tungsten encapsulation over 100 nm in order to be able to observe them. TEM samples are made on the focused ion beam by Helios Nanolab TM from FEI. TEM measurements are performed on a Tecnai Osiris TM from the same manufacturer, and energy dispersive x-ray spectrometry (EDX) analyses are used to characterize the different elements present on the sample.

#### **III. RESULTS AND DISCUSSION**

#### A. Process optimization and comprehension

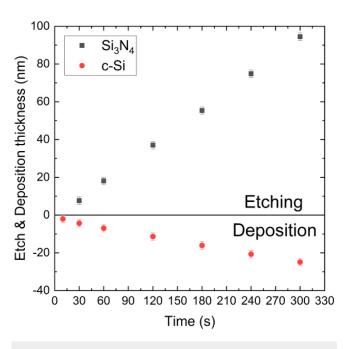

Figure 2 shows the  $CH_3F$ -based chemistry with 2 sccm of  $SiCl_4$  etching on  $Si_3N_4$  and deposition on c-Si kinetics. A linear etch rate of  $19~\text{nm min}^{-1}$  on  $Si_3N_4$  and a linear deposition rate on c-Si of  $5~\text{nm min}^{-1}$  are observed. The deposited layer has been

FIG. 1. Patterned device illustration (a) and cut view after spacer deposition (b).

FIG. 2. Etch and deposition kinetics of  $CH_3F$ -based chemistry with 2 sccm of  $SiCl_4$  on  $Si_3N_4$  and c-Si.

characterized by Pollet *et al.* at 5 sccm of SiCl<sub>4</sub> on poly-Si.<sup>29</sup> Ex situ XPS and ellipsometry measurements showed a selective deposition of SiO<sub>x</sub> on poly-Si compared to Si<sub>3</sub>N<sub>4</sub>. However, after a process time longer than 120 s, they observe an SiO<sub>x</sub> deposition, which starts to grow on Si<sub>3</sub>N<sub>4</sub>. In their conditions, they lose selective deposition between the two materials and observed an etch rate saturation on Si<sub>3</sub>N<sub>4</sub>. As we do not observe etch saturation, we can assume that there is no oxide deposition on Si<sub>3</sub>N<sub>4</sub> in our process condition. This assumption will be discussed in detail later. We also observe a larger Si<sub>3</sub>N<sub>4</sub> etch rate compared to the 14 nm min<sup>-1</sup> observed by Pollet *et al.* during the linear part.<sup>29</sup> These results indicate that Si<sub>3</sub>N<sub>4</sub> etch rate and oxide deposition depend on SiCl<sub>4</sub> flow and more particularly on the O<sub>2</sub>/SiCl<sub>4</sub> ratio.

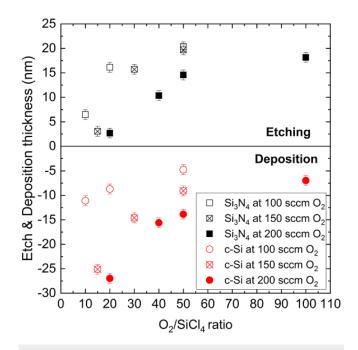

Figure 3 shows the influence of the  $O_2/SiCl_4$  ratio on both the  $Si_3N_4$  etched thickness and the oxide deposition thickness over c-Si for a process time of 60 s. The  $O_2$  flow rate ranges from 100 to 200 sccm with an addition of  $SiCl_4$  from 2 to 10 sccm. Whatever the  $O_2/SiCl_4$  ratio explored, when  $O_2$  flow increases from 100 to 200 sccm, oxide deposited thickness on c-Si increases while  $Si_3N_4$  etched thickness decreases. Regarding the  $O_2/SiCl_4$  ratio, when this ratio increases, oxide deposited thickness on c-Si decreases while  $Si_3N_4$  etched thickness increases. At this stage, there is an inverse correlation between  $Si_3N_4$  etched thickness and deposited oxide thickness on c-Si.

Additionally, an oxide thickness of 20 nm (not shown here) is observed on  $Si_3N_4$  for  $O_2/SiCl_4$  ratios of 15 and 20, corresponding

FIG. 3.  $\mathrm{Si}_3 N_4$  etched thickness and oxide deposition thickness on c-Si as a function of  $\mathrm{O}_2/\mathrm{SiCl}_4$  ratio.

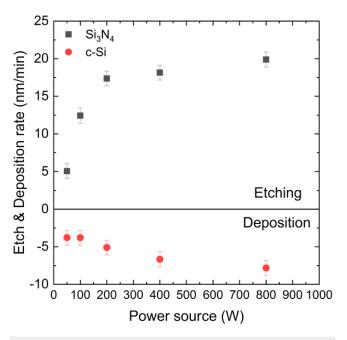

**FIG. 4.**  $Si_3N_4$  etch rate and oxide deposition rate on c-Si as a function of source power of  $CH_3F$ -based chemistry.

Figure 4 shows the Si<sub>3</sub>N<sub>4</sub> etch rate and oxide deposition rate on c-Si as a function of the source power for CH<sub>3</sub>F-based chemistry at an O2/SiCl4 ratio of 100. Both rates increase with the source power from 50 to 800 W. Two regimes are observed for the  $Si_3N_4$ etch rate. Below 200 W, Si<sub>3</sub>N<sub>4</sub> etch rate increases sharply from 5 to 17 nm min<sup>-1</sup>. Above and up to 800 W, it increases slowly until 20 nm min<sup>-1</sup>. The threshold at 200 W is not totally clear. One possible explanation comes from the transition from the capacitive mode (E) to the inductive mode (H) of the ICP reactor.<sup>31</sup> At low source power below 200 W, corresponding to mode E, we suppose the electron density is low and there are less dissociated species from fluorine molecules in the plasma and therefore there is less free F radical flux who interact with material, which may explain the low Si<sub>3</sub>N<sub>4</sub> etch rate. For source power higher than 200 W, corresponding to mode H, the increase in source power leads to an increase in electron density and a higher dissociation participating in the Si<sub>3</sub>N<sub>4</sub> etching. Beyond this value, the weak growth of Si<sub>3</sub>N<sub>4</sub> etch rate seems to indicate that the dissociation of the species participating in the etching increase weakly.

For the oxide deposition rate on c-Si, two regimes are observed. Below 100 W, the oxide deposition rate increases rapidly to  $4 \text{ nm min}^{-1}$ . Above 100 W, oxide deposition rate increases slowly from 4 to  $8 \text{ nm min}^{-1}$ . As SiCl<sub>4</sub> is in the minority in CH<sub>3</sub>F-based chemistry, the trend of oxide growth as a function of the source power applied does not allow seeing clearly a threshold like it does for the Si<sub>3</sub>N<sub>4</sub> etching rate. Beyond 100 W, the weak growth of oxide deposition rate seems to indicate that the dissociation of the species participating in the oxide deposition increases weakly. In addition, the recess measured is minimal, below 1 nm,

and no trend is observed regarding the plasma source. For the rest of the study, a source power of 400 W is chosen to be far from the threshold and to remain in the inductive mode.

#### B. Surface composition

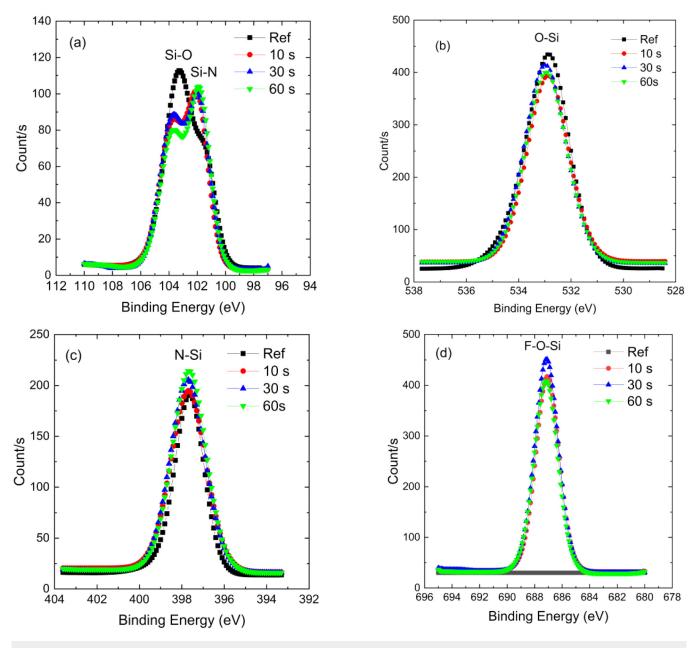

In order to get a better understanding of the reactive layers that form during etching on  $Si_3N_4$  or deposition on c-Si, *quasi in situ* XPS analysis is performed at different process times. Table I and Fig. 5 summarize the atomic percentages of the different elements detected after application of CH<sub>3</sub>F-based chemistry and their associated peak on  $Si_3N_4$  after 10, 30, and 60 s processes and on c-Si after 30 and 120 s (Table II and Fig. 6) processes. The angle of 76.25° is chosen for  $Si_3N_4$  to observe the composition at the extreme surface. For c-Si, the analysis angle is chosen at 23.75° to probe in depth the deposited oxide.

In Table I and Fig. 5, no significant variation of the elements percentage is observed on the extreme surface from 10 to 60 s of etching. The low percentage of carbon from 4% to 5% indicates a low carbon contamination, which is the contamination threshold of the Adixen transfer case. The majority species detected are oxygen, fluorine, and nitride around 20% each. Next come the two peaks of the Si2p spectrum identified by the Si-O bonds at 103.5 eV (Ref. 32) and Si-N at 102 eV (Ref. 33) slightly below 15% and finally some carbon and chlorine. Oxygen at 533 eV corresponds to the O-Si bond.<sup>32,33</sup> The presence of fluorine at 687.2 eV corresponds to the F-O-Si bond. 34 The presence of nitrogen at 398 eV corresponds to the N-Si bond. 32,33 The percentage of N-Si and Si-N bonds in these proportions indicates a stoichiometry close to Si<sub>3</sub>N<sub>4</sub> material. The fact that both Si<sub>3</sub>N<sub>4</sub> material and F-O-Si, O-Si bonds are detected at the extreme surface indicates that a thin layer of fluorine-rich silicon oxynitride  $SiO_xN_vF_z$  is present on  $Si_3N_4$ .

Areas ratio of the Si-O and Si-N elements are constant in the function of time process. Thanks to Eq. (1),<sup>35</sup>

$$t_{\text{SiO}_2/\text{Si}_3\text{N}_4} = \lambda_{\text{SiO}_2/\text{Si}_3\text{N}_4}\cos(\theta) \cdot \ln\left(\frac{A_{\text{SiO}_2}}{A_{\text{Si}_3\text{N}_4}} + 1\right),$$

(1)

where  $t_{\text{SiO}_2/\text{Si}_3\text{N}_4}$  is the oxide layer thickness on top of Si<sub>3</sub>N<sub>4</sub>,  $\lambda_{\text{SiO}_2/\text{Si}_3\text{N}_4}$  is the Si–N photoelectrons inelastic mean free path (IMFP) through oxide,  $\theta$  is the angle of observation, and  $A_{\text{SiO}_2}$  and  $A_{\text{Si}_3\text{N}_4}$  areas corresponding to Si–O and Si–N peaks, respectively, it

**TABLE I.** Percentage value of elements detected by quasi *in situ* XPS at different process times on  $Si_3N_4$  at the extreme surface at a probing angle of 76.25°.

| Element (%) | Reference | Time |      |      |

|-------------|-----------|------|------|------|

|             |           | 10 s | 30 s | 60 s |

| Cl2p        | 0.0       | 3.5  | 2.0  | 1.7  |

| C1s         | 17.0      | 5.3  | 4.4  | 4.1  |

| F1s         | 0.0       | 20.5 | 21.8 | 20.9 |

| O1s         | 31.7      | 23.0 | 23.9 | 23.7 |

| Si2p-O      | 14.3      | 13.9 | 14.4 | 13.3 |

| Si2p-N      | 14.5      | 14.7 | 14.0 | 15.5 |

| N1s         | 18.5      | 19.3 | 19.5 | 20.9 |

is possible to evaluate the oxide layer thickness. Taking the approximation of  $\lambda_{SiO_2/Si_3N_4} \sim \lambda_{SiO_2}$  and a value of 4 nm from the TTP-2M method, <sup>36</sup> the reactive oxide layer thickness is estimated to be inferior to 1 nm. It is consistent with the fact that the reactive layer is thin enough to allow a steady etching of Si<sub>3</sub>N<sub>4</sub> in accordance with the observed etch rates in Fig. 2.

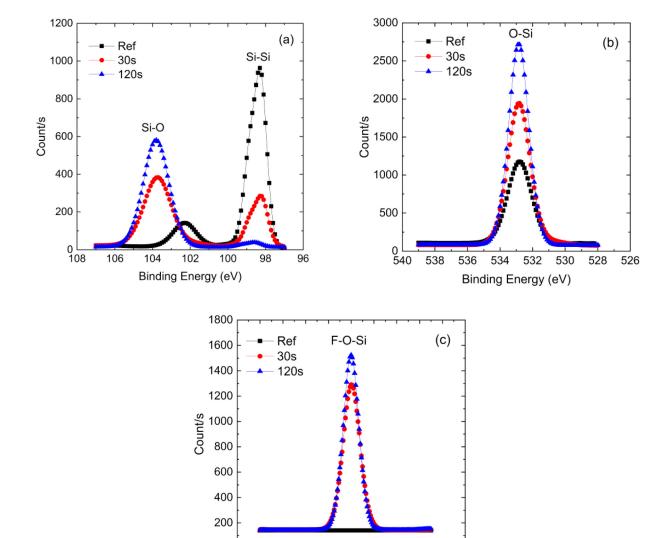

Table II and Fig. 6 show that the surface composition evolves from 30 to 120 s process time on c-Si. Oxygen intensity increases from 42.7% to 47.5% while fluorine remains constant around 21%. The two peaks of the Si2p spectrum are identified as the Si-O bonds at 103.5 eV (Ref. 32) and the doublet Si-Si bonds at 99.2 and 99.8 eV. Intensity of Si-O bonds increases from 23.6% to 29.8%. For Si-Si bonds intensity, it decreases from 10.6% to 1% for 120 s time process. Carbon is lower than 2% and is attributed to carbon contamination. Oxygen at 533 eV corresponds to the O-Si bond. 32,33 The presence of fluorine at 686 eV corresponds to the F-O-Si bond.<sup>34</sup> The fact that F-O-Si, O-Si, and Si-O bonds are detected at the surface indicates a fluorine-rich silicon oxide layer. It can be deduced a presence of SiO<sub>x</sub>F<sub>v</sub> layer on c-Si. The increase of Si-O and O-Si and the decrease of Si-Si from 30 to 120 s indicate the growth of a fluorine-rich silicon oxide layer. Here, the application of Eq. (1) leads to oxide thicknesses of 4 nm for 30 s and 11.6 nm for 120 s time process. These values are in good agreement with ellipsometry measurements presented in Fig. 2.

The bonding energy of Si-N is smaller than that of Si-O, 437 and 800 kJ mol<sup>-1</sup>, respectively.<sup>37</sup> This suggests that it is easier to dissociate the Si-N bond than the Si-O bond. In the case of Si<sub>3</sub>N<sub>4</sub>, the reactive layer estimated by XPS is thin enough to allow energetic species to react with the material and form volatile products such as CN, HCN, 18,19 or SiF<sub>4</sub>. 38 The linear Si<sub>3</sub>N<sub>4</sub> etching rate and constant surface composition suggest that etching occurs through a steady state. The thickness of the reactive layer depends on the O<sub>2</sub>/ SiCl<sub>4</sub> ratio. In the case of c-Si, the oxide growth is initiated beforehand by oxidation of the material due to high O2 flow of CH<sub>3</sub>F-based chemistry and follows the mechanism proposed by Ullal et al.<sup>30</sup> Moreover, dissociation from SiCl<sub>4</sub> to SiCl<sub>3</sub> by electron collision inside the plasma is the most probable species formed due to the higher cross section. <sup>39,40</sup> We suppose that these SiCl<sub>3</sub> species are mainly accelerated from the plasma to the wafer and then react at the oxidized surface following the mechanism proposed by Ullal et al. in order to form this oxide layer.

The choice of the  $O_2/SiCl_4$  ratio in  $CH_3F$ -based chemistry shows that the oxide layer thickness grows linearly, limiting the diffusion of reactive species from the plasma to the c-Si surface by forming a fluorine-rich silicon oxide  $SiO_xF_y$  layer and thus limiting the Si-recess. Therefore, the selective deposition between the two materials is induced by the choice of  $O_2/SiCl_4$  ratio and the difference between bonding energies for Si–N and Si–O.

#### C. Application on patterned structures

To etch  $Si_3N_4$  spacers on 3D patterns, a first step based on  $CH_3F/O_2/He/SiCl_4$  chemistry is used. The time is set in order to etch 11.5 nm of  $Si_3N_4$  on the active source and drain area. An over etch is applied to allow the growth of 4 nm thick oxide on the active area. Then, the etching strategy chosen for the spacers in 3D topology is a cyclic approach, which alternates the  $CH_3F$ -based

**FIG. 5.** Element spectra for (a) Si2p, (b) O1s, (c) N1s, and (d) F1s detected by quasi in situ XPS for reference, 10, 30, and 60 s on  $Si_3N_4$  at the extreme surface (76.25°).

and  $CH_2F_2$ -based chemistries. The former has been detailed in Secs. III A and III B. The role of the latter is to etch the surplus of oxide deposit from the former. The oxide etch rate of  $CH_2F_2$ -based chemistry is measured at 2 nm min<sup>-1</sup> on blanket wafers (not shown here).

After the first oxide deposition of 4 nm, the cycling of these two chemistries is applied. The strategy here is to reduce the oxide

thickness to 2 nm with  $CH_2F_2$ -based chemistry in order to allow  $Si_3N_4$  parasitic spacers etching and keep enough oxide thickness to protect the active area. To complete a cycle,  $CH_3F$ -based chemistry is used to restart  $Si_3N_4$  etching. The oxide deposited on the active area is expected to regrow to 4 nm after each end of cycle. Such a strategy is established from ellipsometric measurement on blanket wafers. Thus, during one complete cycle, we expect the oxide layer

**TABLE II.** Percentage value of elements detected by quasi *in situ* XPS at different process times on c-Si at bottom at 23.75°.

| Element (%)       |           | Time |       |  |

|-------------------|-----------|------|-------|--|

|                   | Reference | 30 s | 120 s |  |

| C1s               | 13.0      | 1.5  | 0.5   |  |

| F1s               | 0.0       | 21.5 | 21.2  |  |

| O1s               | 32.0      | 42.7 | 47.5  |  |

| Si2p-O            | 8.3       | 23.6 | 29.8  |  |

| Si2p-O<br>Si2p-Si | 45.5      | 10.6 | 1.0   |  |

thickness on the active area to oscillate between 2 and 4 nm. The equivalent etch rate of  $\mathrm{Si}_3\mathrm{N}_4$  per cycle is estimated between 15 and 20 nm cycle<sup>-1</sup>. Cycles are applied on the patterned wafer and the results are presented in Fig. 7 before diluted HF 1% and after diluted HF 1% treatment in Fig. 8.

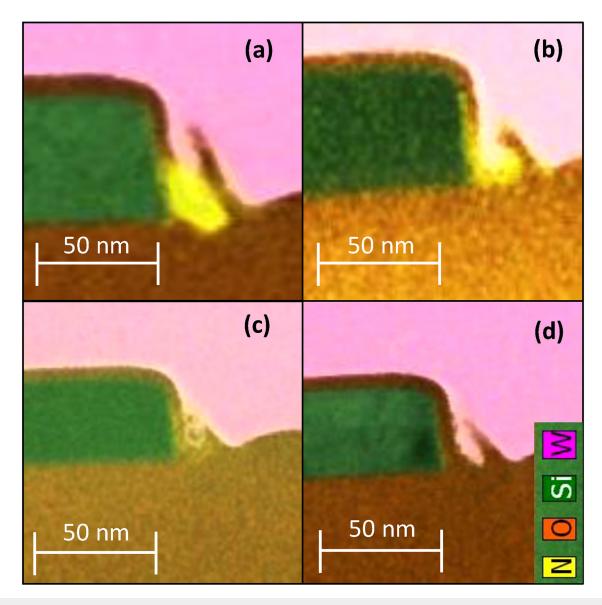

Figure 7 shows the TEM/EDX mapping of the elements present after one, two, four, and six cycles at the edges of the active source and drain area. Here, the Si fin height is 36 nm. The elements present are silicon, oxygen, tungsten, and nitrogen. After a full cycle, as shown in Fig. 7(a), about 60% of the Si<sub>3</sub>N<sub>4</sub> spacer is removed. Thicknesses of both oxides, on the surface of c-Si and on

FIG. 6. Element spectra for (a) Si2p, (b) O1s, and (c) F1s detected by quasi in situ XPS for reference, 30 and 120 s on c-Si at bottom (23.75°).

696 694 692 690 688 686 684 682 680 678 676 Binding Energy (eV)

FIG. 7. TEM/EDX images showing the side of the active area after: (a) one cycle, (b) two cycles, (c) four cycles, and (d) six cycles.

the side of  $Si_3N_4$ , are close to 4 nm, as expected. There is no oxide on top of  $Si_3N_4$ . After two cycles as shown in Fig. 7(b), 90% of the spacers on the side of the pattern is removed. Again, the oxide on the surface of c-Si and on the side of  $Si_3N_4$  is estimated at 4 nm. Finally, after four and six cycles, as shown in Figs. 7(c) and 7(d), respectively, 100% of the spacer on the side of the pattern is removed. The oxide thickness on the active area is 4 nm and 5 nm on the side due to the lateral growth of the oxide. Microscopy observations on patterned wafers are in good agreement with expectation deduced from ellipsometry measurements on blanket samples. This indicates the robustness of the approach.

Figure 8 presents TEM images of the spacers after cyclic etching and diluted HF 1% treatment representing the bottom of gate spacers and the side of the active area, respectively. Figure 8 shows that the gate spacer's CD is mostly preserved: it presents a width of 9 nm and only 3 nm was etched by the process. An absence of foot at the bottom [Fig. 8(a)] and of parasitic spacers on the side of the active area [Fig. 8(b)] is also observed. The CD's preservation indicates that the growth of the chemically deposited lateral oxide played its role as a protector of the gate spacers by radical/ion provided by the plasma.

FIG. 8. TEM image of the zoom at the bottom of gate spacers (a) and zoom at the FinFET side and (b) after HF 1% 30 s.

Therefore, the developed chemistries with a cyclic approach allow after three etch cycles to fully etch 36 nm of parasitic spacers while conserving the gate spacer CD.

#### IV. SUMMARY AND CONCLUSIONS

In this paper, we have optimized a cyclic approach based on CH<sub>3</sub>F/O<sub>2</sub>/He/SiCl<sub>4</sub> hydrofluorocarbon chemistry for Si<sub>3</sub>N<sub>4</sub> spacers etching of 3D CMOS patterns. We first studied the parameters influencing Si<sub>3</sub>N<sub>4</sub> etching and oxide deposition on c-Si such as the O<sub>2</sub>/SiCl<sub>4</sub> ratio of a CH<sub>3</sub>F/O<sub>2</sub>/He hydrofluorocarbon chemistry with SiCl<sub>4</sub> addition, the source power and kinetics on blanket wafers. The variation of O2/SiCl4 ratio allows a wide window of oxide deposited thickness on c-Si and etched thickness of Si<sub>3</sub>N<sub>4</sub>. The choice of a ratio depends on the trade-off between depositing a sufficient amount of oxide on c-Si and obtaining a large Si<sub>3</sub>N<sub>4</sub> etch rate. Indeed, it must be sufficient to protect the active area by limiting the consumption of c-Si and have an etch rate of Si<sub>3</sub>N<sub>4</sub> high enough to limit the number of cycles. The study of kinetics has shown linear etching trends in Si<sub>3</sub>N<sub>4</sub> etching and oxide deposition on c-Si that can be used as a standard for setting etching times during cycles. Quasi in situ XPS analyses showed that the oxide layer deposited on Si<sub>3</sub>N<sub>4</sub> is a thin (less than 1 nm) fluorine-rich oxynitride SiO<sub>x</sub>N<sub>y</sub>F<sub>z</sub>. A mechanism for the formation of this oxide has been proposed. This small thickness coupled with a high bias voltage suggests that this reactive layer is constantly renewed by sputtering/deposition of this reactive layer, allowing continuous etching on Si<sub>3</sub>N<sub>4</sub>.

Finally, we applied the results of this optimization for the cyclic approach. The 3D topology of the patterns showed the necessity to use a cyclic approach to complete the etching of the parasitic

spacers on the side source and drain active area. The application of this chemistry during cycling has shown that a small number of cycles, such as two or three, is sufficient to complete the etching of the parasitic spacers while etching only 3 nm of lateral  $\mathrm{Si}_3\mathrm{N}_4$  constituting the gate spacers. The results are in accordance with the expectations of experiments carried out on blanket with a perfect control of the oxide deposited layer. In terms of perspective, a refined understanding of the mechanisms of deposition and etching must be pursued to further improve Si-recess.

#### **ACKNOWLEDGMENTS**

This work has been supported by the French National Research Agency (ANR) within the IMPACT program, under contract No. ANR-10-EQPX-33.

#### **REFERENCES**

<sup>1</sup>IEEE-IRDS, "International Roadmap for Devices and Systems 2020 update More Moore," More Moore, 2020, available at https://irds.ieee.org/editions/2020.

<sup>2</sup>F. Koehler, D. Triyoso, I. Hussain, S. Mutas, and H. Bernhardt, IOP Conf. Ser. Mater. Sci. Eng. 41, 012006 (2012).

<sup>3</sup>M. G. Blain, T. L. Meisenheimer, and J. E. Stevens, J. Vac. Sci. Technol., A 14, 2151 (1996).

<sup>4</sup>M. J. Kumar and S. G. Chamberlain, Solid State Electron. 39, 33 (1995).

<sup>5</sup>S. Lee, J. Oh, K. Lee, and H. Sohna, J. Vac. Sci. Technol., B **28**, 131 (2010).

<sup>6</sup>B. E. E. Kastenmeier, P. J. Matsuo, J. J. Beulens, and G. S. Oehrlein, J. Vac. Sci. Technol., A 14, 2802 (1996).

<sup>7</sup>Y. Ishii, K. Okuma, T. Saldana, K. Maeda, N. Negishi, and J. Manos, Jpn. J. Appl. Phys. **56**, 06HB07 (2017).

<sup>8</sup>J. S. Kim, B. S. Kwon, W. Heo, C. R. Jung, J. S. Park, J. W. Shon, and N.-E. Lee, J. Vac. Sci. Technol., A **28**, 755 (2010).

- <sup>9</sup>S. S. Kaler, Q. Lou, V. M. Donnelly, and D. J. Economoub, J. Vac. Sci. Technol., A **34**, 041301 (2016).

- H. Ohtake, T. Wanifuchi, and M. Sasaki, Jpn. J. Appl. Phys. 55, 086502 (2016).

T. C. Mele, J. Nulman, and J. P. Krusius, J. Vac. Sci. Technol., B 2, 684 (1984).

- 12Y. X. Li, P. J. French, and R. F. Wolffenbuttel, J. Vac. Sci. Technol., B 13, 2008

- (1995).

13 J. Son, S. Y. A. Efremov, G. Yeom, and K. Kwon, J. Nanosci. Nanotechnol. 14, 9534 (2014).

- <sup>14</sup>S. Engelmann, R. L. Bruce, E. A. Joseph, N. M. Fuller, W. S. Graham, E. M. Sikorski, M. Kohjasteh, and Y. Zhu, J. Vac. Sci. Technol., B 35, 051803 (2017)

- <sup>15</sup>H. Miyazoe *et al.*, J. Vac. Sci. Technol., B **36**, 032201 (2018).

- 16N. Possémé, M. Garcia-Barros, C. Arvet, O. Pollet, F. Leverd, and S. Barnola, J. Vac. Sci. Technol., A 38, 033004 (2020).

- <sup>17</sup>R. Blanc, F. Leverd, T. David, and O. Joubert, J. Vac. Sci. Technol., B 31, 051801 (2013).

- <sup>18</sup>L. Chen, L. Xu, D. Li, and B. Lin, Microelectron. Eng. **86**, 2354 (2009).

- <sup>19</sup>T. Ito, K. Karahashi, M. Fukasawa, T. Tatsumi, and S. Hamaguchi, J. Vac. Sci. Technol., A 29, 050601 (2011).

- <sup>20</sup>N. Yabumoto, M. Oshima, O. Michikami, and S. Yoshii, Jpn. J. Appl. Phys. 20, 893 (1981).

- <sup>21</sup>Y. Nakakubo, A. Matsuda, M. Kamei, H. Ohta, K. Eriguchi, and K. Ono, *Analysis of SI Substrate Damage Induced by Inductively Coupled Plasma Reactor with Various Superposed Bias Frequencies*, edited by A. Newman (Springer, New York, 2010), Vol. 66, pp. 62–68.

- <sup>22</sup>T. Ohchi, S. Kobayashi, M. Fukasawa, K. Kugimiya, T. Kinoshita, T. Takizawa, S. HamagushiI, Y. Kamide, and T. Tatsumi, Jpn. J. Appl. Phys. 47, 5324 (2008).

- <sup>23</sup>K. Eriguchi, A. Matsuda, Y. Nakakubo, M. Kamei, and H. Ohta, *IEEE*, Austin, TX, 18–20 May 2009 (IEEE, New York, 2009), pp. 101–104.

- <sup>24</sup>R. Blanc, F. Leverd, M. Darnon, G. Cunge, S. David, and O. Joubert, J. Vac. Sci. Technol., B 32, 021807 (2014).

- <sup>25</sup>M. Matsui, M. Morimoto, and N. Ikeda, Jpn. J. Appl. Phys. **54**, 06GB02 (2015).

- <sup>26</sup>N. Posseme, O. Pollet, and S. Barnola, Appl. Phys. Lett. **105**, 051605 (2014).

- <sup>27</sup>V. Renaud, C. Petit-Etienne, J.-P. Barnes, J. Bisserier, O. Joubert, and E. Pargon, J. Appl. Phys. **126**, 243301 (2019).

- <sup>28</sup>S. Kumakura, M. Tabata, and M. Honda, Jpn. J. Appl. Phys. 58, SEEB01 (2019).

- <sup>29</sup>O. Pollet, V. Ah-Leung, S. Barnola, and A. N. Posseme, J. Vac. Sci. Technol., A **38**, 063007 (2020).

- 30S. Ullal, H. Singh, V. Vahedi, and E. Aydil, J. Vac. Sci. Technol., A 20, 499 (2001)

- <sup>31</sup>U. Kortshagen, N. D. Gibson, and J. E. Lawler, J. Phys. D: Appl. Phys. 29, 1224 (1996).

- <sup>32</sup>M. Schaepkens, T. E. F. Standaert, N. Rueger, P. Sebel, G. Oehrlein, and J. Cook, J. Vac. Sci. Technol., A 17, 26 (1999).

- 33 N. Possémé, V. Ah-Leung, O. Pollet, C. Arvet, and M. Garcia-Barros, J. Vac. Sci. Technol., A 34, 061301 (2016).

- <sup>34</sup>K. Hanamoto, H. Yoshimoto, T. Hosono, A. Hirai, Y. Kido, Y. Nakayama, and R. Kaigawa, Nucl. Instrum. Methods B 40, 124 (1998).

- M. Seah and S. Spencer, Surf. Interface Anal. 33, 640 (2002).

- <sup>36</sup>R. Jung, J. Lee, G. Orosz, A. Sulyok, G. Zsolt, and M. Menyhard, Surf. Sci. 534, 53 (2003).

- <sup>37</sup>D. R. Lide, *Handbook of Chemistry and Physics*, 87th ed. (CRC, Boca Raton, FL, 2006).

- <sup>38</sup>T. E. F. Standaert, M. Schaepkens, N. Rueger, P. Sebel, G. Oehrlein, and J. Cook, J. Vac. Sci. Technol., A **16**, 239 (1998).

- <sup>39</sup>E. Fisher and P. Armentrout, J. Phys. Chem. **95**, 4765 (1991).

- <sup>40</sup>R. Basner, M. Gutkin, J. Mahoney, V. Tarnovsky, H. Deutsch, and K. Becker, J. Chem. Phys. 123, 054313 (2005).