# Multilayer OTS selectors engineering for high temperature stability, scalability and high endurance

C. Laguna, M. Bernard, N. Bernier, D. Rouchon, N. Rochat, J. Garrione, A. Jannaud, E. Nolot, V. Meli, N. Castellani, et al.

## ▶ To cite this version:

C. Laguna, M. Bernard, N. Bernier, D. Rouchon, N. Rochat, et al.. Multilayer OTS selectors engineering for high temperature stability, scalability and high endurance. IMW2021 - 2021 IEEE International Memory Workshop, May 2021, Dresden, Germany. pp.1-4, 10.1109/IMW51353.2021.9439590. cea-03331470

# HAL Id: cea-03331470 https://cea.hal.science/cea-03331470v1

Submitted on 1 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Multilayer OTS Selectors Engineering for High Temperature Stability, Scalability and High Endurance

C. Laguna<sup>1,2</sup>, M. Bernard<sup>1</sup>, N. Bernier<sup>1</sup>, D. Rouchon<sup>1</sup>, N. Rochat<sup>1</sup>, J. Garrione<sup>1</sup>, A. Jannaud<sup>1</sup>, E. Nolot<sup>1</sup>, V. Meli<sup>1</sup>, N. Castellani<sup>1</sup>, C. Sabbione<sup>1</sup>, G. Bourgeois<sup>1</sup>, M. C. Cyrille<sup>1</sup>, L. Militaru<sup>2</sup>, A. Souifi<sup>2</sup>, G. Navarro<sup>1,\*</sup> and E. Nowak<sup>1</sup>

<sup>1</sup>CEA, LETI, Univ. Grenoble Alpes, 38000 Grenoble, France.

<sup>2</sup>Univ. de Lyon, INL-UMR CNRS 5270, INSA Lyon, 69621 Villeurbanne, France.

\*contact author: gabriele.navarro@cea.fr

Abstract—We present the engineering of Ovonic Threshold Switching (OTS) Multilayer (ML) Selector device based on the stacking of N-doped SbSe and Ge layers. By tuning individual layers thicknesses and N content of the ML stack, we demonstrate the possibility to highly improve selector stability during integration Back-End-of-Line (BEOL) and to reduce device-to-device variability. We show how our OTS ML presents fundamental electrical characteristics that are compatible with the ones of standard bulk OTS achieved by co-sputtering technique, but enabling reliable switching operations up to 160°C with lower variability. We study by FTIR and Raman spectroscopy the layers structure revealing the high stability achieved in OTS ML wrt bulk OTS even after 3 hours at 400°C. In TEM/EDX analyses performed on cycled and annealed devices, we highlight the preserved integrity of the amorphous structure in OTS ML wrt bulk. Finally, OTS ML solution allows reliable endurance up to more than 10<sup>9</sup> cycles and improved yield in scaled devices thanks to a higher control of the layer structure and properties.

#### I. INTRODUCTION

With the gradual transition of modern computing systems towards memory-centric architectures, Storage Class Memory (SCM) becomes a necessary level of the memory hierarchy with the goal to provide a low read latency, non-volatile and cost effective interface between the memory (DRAM) and the storage (NAND Flash) [1]. Crossbar architectures has emerged as the best candidate for SCM applications, providing at the same time the requested high density with ultimate elemental cell area of 4F<sup>2</sup>, and overall the possibility to stack the memory layers in 3D. The success of the 3D Crossbar solutions recently presented [2, 3], was possible thanks to the introduction of a stackable amorphous selector called Ovonic Threshold Switching (OTS). OTS is the most promising Back-End-of-Line (BEOL) selector technology thanks to its high ON/OFF selectivity, high switching speed and endurance. In the last years several OTS materials have been proposed in order to meet the specifications in terms of switching reliability [4]–[7], raising the challenge of finding a solution that offers at the same time low variability of the electrical parameters, to enhance the reading window, and temperature stability to withstand the BEOL of the integration without compromising the integrity of the amorphous structure of the material. Moreover, the control of the morphology of the OTS layer becomes even more important in ultra scaled

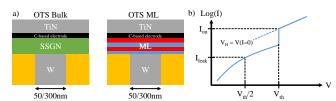

**Fig. 1.** a) Simplified description of our OTS ML compared to standard OTS. Devices with W bottom electrode with diameter of 300 nm down to 50 nm are investigated. b) Fundamental IV characteristic after forming of an OTS device and main electrical parameters.

devices, where also localized segregation and/or crystallization phenomena can be detrimental for the device reliability.

In this framework, we previously presented the OTS Multilayer (ML) solution, based on the stacking of SbSe (SS) and Ge layers selectively doped with N, showing how it opens the possibility to control the thermal stability of the OTS layer and to reduce the electrical parameters variability [8]. In this work, we present the engineering of our OTS ML in which we combine the fine tuning of the layers thickness and N doping, comparing its performances with the equivalent reference OTS bulk layer (Ge/N-doped SS or SSGN), matched in terms of global Ge, Sb, Se contents and designed in line with our previous studies on Ge-Se-Sb-N alloy (GSSN) [9] (**Fig. 1**). We report an excellent temperature stability for ML structure, providing the electrical parameters up to 160°C and after an annealing of 3 hours at 400°C. Thanks to Raman and FTIR spectroscopy, we highlight the main structural evolution of the layers at high temperature. In TEM/EDX analysis performed on OTS devices, we confirm the improved integrity of the amorphous structure achieved in OTS ML even after the annealing at 400°C. Endurance tests performed on both as fabricated (as fab) and annealed devices, bring out the correlation of the cycles numbers with the pulse duration, and the possibility to reliably achieve more than 10<sup>9</sup> cycles in OTS ML. Finally, scalability is investigated in devices down to 50 nm, showing a higher yield and lower variability in OTS ML.

## II. CHARACTERIZATION OF OTS ML SELECTORS

We fabricated OTS ML by alternative magnetron reactive sputtering from SS and Ge targets, selectively doped with N. A thin carbon layer is inserted between chalcogenide layer and titanium nitride top electrode to hinder Ti diffusion within the active layer during fabrication and during device operations. Electrical tests and statistics were performed on populations of 30 devices.

This work has been partially supported by European commission, French State and Auvergne-Rhône Alpes region through the funding of ECSEL 783176 WAKeMeUP Project part of IPCEI (Important Project of Common European Interest) on microelectronics and French Nano2022 program.

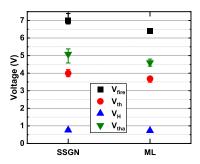

**Fig. 2.** SSGN and ML switching voltages measured on 30 devices after 100 cycles: fire voltage ( $V_{\rm fire}$ ), threshold voltage ( $V_{\rm th}$ ), holding voltage ( $V_{\rm H}$ ), threshold voltage after annealing of 30 min at 400°C ( $V_{\rm tha}$ ).

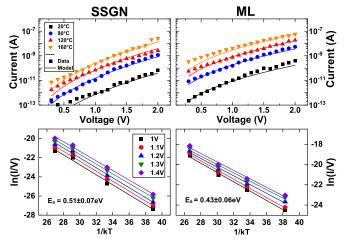

**Fig. 3.** Subthreshold conduction analysis (top graphs). Curves are fitted using Poole-Frenkel model for both materials. Activation energy is extracted for different voltages, finding compatible values in SSGN and ML (bottom graphs).

### A. OTS ML electrical characteristics up to 160°C

**Fig. 2** reports the comparison of voltages used for main operations in our selectors after 100 cycles. OTS ML matches the switching voltages of SSGN with slight differences, even after an annealing of 30 minutes at  $400^{\circ}$ C, after which a slight increase of the threshold voltage  $V_{th}$  is observed ( $V_{tha}$ ).

Subthreshold conduction study for different temperatures up to  $160^{\circ}\text{C}$  is reported in **Fig. 3**. The subthreshold current increases with temperature, being Poole-Frenkel conduction dominant in both materials [11]. From activation energy calculation, we observe a good compatibility between the two materials in terms of  $E_a$ , meaning an equivalent localization of the trap states in the gap in both bulk and ML, giving rise to close conduction mechanisms.

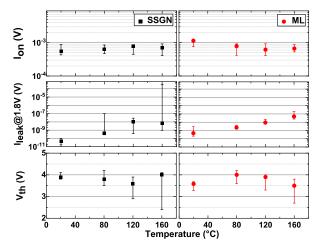

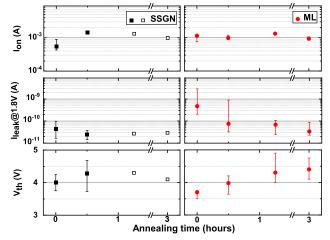

Main device parameters and their variability are reported in **Fig. 4**, following their evolution up to the operating temperature of  $160^{\circ}$ C. We can observe similar trends in the two materials, with median values almost stable for ON current ( $I_{on}$ ) and  $V_{th}$ , and an increase of the leakage current ( $I_{leak}$ ) as previously observed in subthreshold conduction analysis. However, a higher parameters variability is found in SSGN, starting already at  $80^{\circ}$ C.

**Fig. 4.** Median values measured for ON current ( $I_{on}$ ), leakage current measured at 1.8 V ( $I_{leak}$ ) and  $V_{th}$  at different operating temperatures, reported with error bars representing max and min values. Both materials shows functionality up to  $160^{\circ}C$ , however SSGN shows an increased variability wrt ML.

Fig. 5. Median values and errors bars representing max and min values for  $I_{\rm on}$ ,  $I_{\rm leak}$  and  $V_{\rm th}$  after different annealing steps at 400°C. Empty symbols for SSGN highlight the median values calculated for remaining functional devices (< 75%).

### B. OTS ML Stability at 400°C

In order to study the capability of our OTS devices to sustain aggressive BEOL thermal budget, we performed consecutive annealing procedures at 400°C up to a total time of 3 hours. In Fig. 5, we report the main OTS parameters measured after the different annealing steps. After about 1 hour of annealing, SSGN starts to show a degradation of the switching mechanism in more than 25% of the tested devices, likely related to the incoming crystallization of the layer. On the contrary ML shows perfect functionality even after 3 hours at 400°C. The decrease of Ileak and the increase of Vth are compatible with a gradual evolution of the ML morphology, not detrimental for the switching properties of the device till the integrity of the amorphous structure of the layer is preserved. Indeed, after the 3 hours annealing, the OTS ML tends to approach values for  $I_{leak}$  (< 0.1 nA) and  $V_{th}$  ( $\sim$  4.5V) close to the ones that bulk OTS presents after only 30 minutes of annealing. Therefore, the ML configuration helps delaying the crystallization and

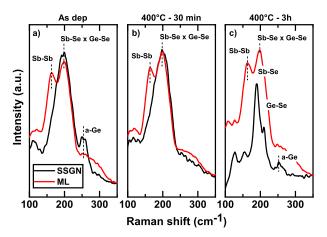

**Fig. 6.** Raman spectra for as deposited (as dep) SSGN and ML layers and after annealing at 400°C. After 3 hours at 400°C, SSGN shows a likely segregation of GeSe and SbSe compounds, whereas ML presents a spectrum close to the as dep one, confirming its improved structure stability.

segregation phenomena that are responsible for the loss of functionality of the devices.

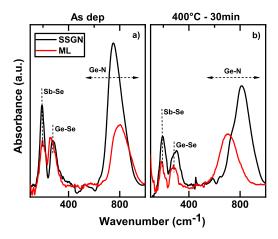

To support our hypothesis, we performed Raman and FTIR analyses on as deposited and annealed OTS layers reported in **Fig. 6** and **Fig. 7**. After 30 minutes of annealing, we observe a slight change in the main features highlighted in Raman spectra, and a shift of the Ge-N broad band, indicative of both an amorphous structural relaxation and GeN features reorganization. In particular, a shift of the Ge-N vibration modes towards higher wavenumbers, as observed in SSGN, could be due to a gradual change of Ge and N atoms arrangement, towards Ge-N features poorer in Ge content, driven by an already started phase segregation and following crystallization, as already observed in other chalcogenide based systems [12].

After 3 hours at 400°C, Raman spectum of SSGN shows the appearing of separated SbSe and GeSe peaks, that is a demonstration of an already advanced segregation and likely crystallization of the layer [13]. Indeed, Ge-Se and Sb-Se bonds are likely to form at high temperature [14] giving rise to separated stable phases. On the contrary, the spectrum of ML does not show significant changes. The localization of Ge-Se bonds at the interfaces between SS and Ge layers, the slower diffusion of Ge atoms implied in GeN features, and the retarded crystallization of SS layers due to their specific stoichiometry and thickness, delay the segregation process in the ML layer.

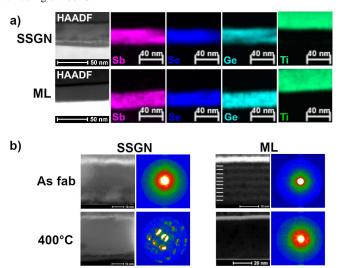

#### C. TEM/EDX analyses

We performed TEM/EDX analyses on devices after an electrical stress represented by more than 10<sup>6</sup> cycles (**Fig. 8a**). We can observe an overall homogeneous elemental distribution in both SSGN and ML, without any Ti contamination from the top electrode. The compatible morphology of the two layers, confirms the possibility to achieve at the forming operation, and then in the following of programming operations, the same composition in the formed region of the device in both layers. This is confirmed by the strong alignment observed in

Fig. 7. FTIR spectra of SSGN and ML as deposited and after a 30 minutes annealing at  $400^{\circ}\text{C}$ .

**Fig. 8.** a) TEM images (HAADF) and Sb, Se, Ge, Ti EDX maps performed on OTS devices after electrical stress (10<sup>6</sup> cycles). b) TEM and nanodiffraction patterns for as fab and annealed (400°C-30 min) devices.

electrical characteristics between the two materials. In TEM images and nanodiffraction patterns of **Fig. 8b**, we report the comparison of SSGN and ML devices before and after annealing at 400°C. SSGN shows crystalline patterns after annealing, compatibly with devices performances degradation previously highlighted. On the contrary, ML preserves the high layers integrity after fabrication and the amorphous structure even after the annealing at 400°C, confirming previous observations.

#### D. Endurance analysis

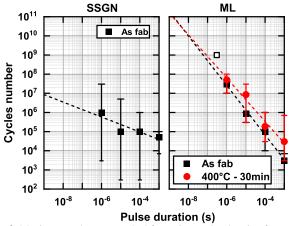

We studied the impact of pulse duration on endurance performances of as fab and annealed devices. As reported in **Fig. 9**, SSGN presents a high variability of the total cycles numbers before failure, that makes difficult the extrapolation of the possible endurance achievable at short pulse duration. After annealing at 400°C, SSGN devices present a limited endurance not overcoming 10<sup>3</sup> cycles. ML shows better performances and low variability on maximum cycles number achievable, even after annealing. This allows to more reliably

Fig. 9. Maximum endurance reached for a given pulse duration for as fab and annealed ( $400^{\circ}$ C-30min) SSGN and ML devices. Data are not reported for annealed SSGN, because of endurance limited at <  $10^{3}$  cycles. Experimental demonstration of more than  $10^{9}$  cycles in one as fab device for 300 ns pulse is reported with the empty symbol.

extrapolate an endurance of more than  $10^9$  cycles at reduced pulse duration, and to confirm in OTS devices the link between endurance and pulse energy. The possibility to achieve more than  $10^9$  cycles was experimentally verified for 300 ns wide pulses.

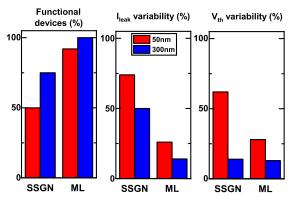

### E. Scalability

We compared the electrical behavior of our 50 nm and 300 nm devices integrating SSGN and ML layers. To be noticed, we used same initialization procedure for all the devices and same Ion as in Fig. 5, without triggering specific current control (i.e. higher device stress than potential real working conditions at lower current). In Fig. 10, we report the subthreshold analysis and the values measured for V<sub>th</sub> and I<sub>leak</sub>. Variability of the devices behavior appears in SSGN already from the subthreshold IV curves, compared with ML that confirms on the contrary the possibility to reduce I<sub>leak</sub> in scaled devices. Moreover, functional SSGN 50 nm devices show functionality degradation already after 10 cycles. Finally, we report in **Fig. 11** the total % of functional devices found for both SSGN and ML and the variability of main electrical parameters. As we can observe, OTS ML shows a less sensitivity to scaling wrt SSGN, demonstrated by a higher yield with more than 90% of functional devices and lower variability of electrical parameters in both studied devices dimensions.

## III. CONCLUSIONS

In this paper, we present the engineering of OTS ML, achieved thanks to fine tuning of layers thickness and N doping, targeting high temperature stability and low device-device variability. We demonstrate the good matching of electrical performances of OTS ML with standard bulk SSGN up to operating temperatures of  $160^{\circ}$ C. Thanks to an improved stability assured by the Multilayer structure, we show the capability of OTS ML to withstand a BEOL thermal budget of 3 hours at  $400^{\circ}$ C. To support the results, we provide electrical characterizations after annealing ( $I_{leak} < 0.1$  nA), together with

**Fig. 10.** IV subthreshold characteristics for 50 nm and 300 nm devices integrating SSGN and ML (top graphs). Median values for  $V_{th}$  and  $I_{leak}$  with error bars representing max and min values (bottom graphs). Empty symbols and dotted lines are used to represent the devices behavior despite a yield lower than 75% as described in Fig. 11 (i.e. SSGN 50 nm).

Fig. 11. Final % of functional devices for both 50 nm and 300 nm dimensions, and associated variability ((max-min)/median\*100) of  $I_{leak}$  and  $V_{th}$ .

Raman and FTIR spectroscopy showing the stability of the spectra, and TEM/EDX analyses. The higher yield of OTS ML wrt bulk OTS allows reliable endurance up to more than 10<sup>9</sup> cycles and reduced electrical parameters variability, confirmed even in scaled devices down to 50 nm. All these results, confirm the suitability of OTS ML solution for high stability in extreme BEOL thermal budget, ensuring a great control of device performances and variability down to nm scale devices.

#### REFERENCES

- [1] Taehoon Kim et al., IEEE Trans. Elec. Dev., vol. 67, no. 4, 2020.

- [2] Huai-Yu Cheng et al., J. Phys. D: Appl. Phys., 52, 473002, 2019.

- [3] Taehoon Kim et al., IEDM Tech. Dig., pp. 37.1.1-37.1.4, 2018.

- [4] H. Y. Cheng et al., in Proc. IEDM 2018, pp. 37.3.1-37.3.4, 2018.

- [5] S. Clima et al., Phys. Status Solidi RRL, vol. 14, pp. 1-10, 2020.

- [6] Y. Koo et al., Sci Rep 8, 11822, 2018.

- [7] A. Verdy et al., in Proc. IMW 2019,2-4, pp.1-4, 2019.

- 8] C. Laguna et al., in Proc. IMW 2020,pp. 1-4, 2020.

- [9] A. Verdy et al., in Proc. 2018 IEDM, 37.4.1-37.4.4, 2018.

- [10] W.C. Chien et al., in Proc. VLSI 2019, T60, 2019.

- [11] S. Jia et al., in Proc. IEDM 2020, pp. 1-4, 2020.

- [12] L. Prazakova et al., J. Appl. Phys., 128, 215102, 2020.

- [13] H. Wang et al., J. Non-Cryst. Solids, vol. 453, pp. 108-112, 2016.

- [14] N. Sharma et al., J. Non-Cryst. Solids, vol. 375, pp. 114-118, 2013.

- [15] M. Olivier et al., *Opt. Express*, vol. 4(3), pp. 252-540, 2014.

- [16] Z.G. Ivanova et al., Mat. Letters, vol. 57, pp. 1025-1028, 2002.

- [17] S. Sharda et al., J. Non-Cryst. Solids, vol. 362, pp. 136-139, 2013.