## A RISC-V ISA extension for ultra-low power IoT wireless signal processing

Hela Belhadj Amor, Carolynn Bernier, Zdenek Prikryl

#### ▶ To cite this version:

Hela Belhadj Amor, Carolynn Bernier, Zdenek Prikryl. A RISC-V ISA extension for ultra-low power IoT wireless signal processing. IEEE Transactions on Computers, 2021, 2021, pp.1-1. 10.1109/TC.2021.3063027. cea-03158876v2

### HAL Id: cea-03158876 https://cea.hal.science/cea-03158876v2

Submitted on 17 Mar 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A RISC-V ISA Extension for Ultra-Low Power IoT Wireless Signal Processing

Hela Belhadj Amor, Carolynn Bernier and Zdeněk Přikryl

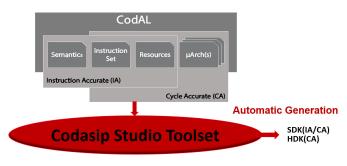

Abstract—This work presents an instruction-set extension to the open-source RISC-V ISA (RV32IM) dedicated to ultra-low power (ULP) software-defined wireless IoT transceivers. The custom instructions are tailored to the needs of 8/16/32-bit integer complex arithmetic typically required by quadrature modulations. The proposed extension occupies only 2 major opcodes and most instructions are designed to come at a near-zero energy cost. Both an instruction accurate (IA) and a cycle accurate (CA) model of the new architecture are used to evaluate six IoT baseband processing test benches including FSK demodulation and LoRa preamble detection. Simulation results show cycle count improvements from 19% to 68%. Post synthesis simulations for a target 22nm FD-SOI technology show less than 1% power and 28% area overheads, respectively, relative to a baseline RV32IM design. Power simulations show a peak power consumption of 380 μW for Bluetooth LE demodulation and 225 μW for LoRa preamble detection (BW = 500 kHz, SF = 11).

Index Terms—RISC-V ISA extension, IoT, software-defined radio, ultra-low power (ULP) transceiver architecture, Bluetooth, LoRa.

#### 1 Introduction

TIRELESS Internet of Things (IoT) connectivity solutions have been gaining exponential adoption rates and enabling new applications in a diverse range of verticals such as transportation, health, industry and agriculture. The huge diversity of IoT use cases has naturally spurred the development of dedicated communication protocols, from the physical layer to the networking layers. Indeed, since IoT endpoints are typically energy constrained devices, tailoring the communication protocol to an application's specific needs is a necessity, amplified by the fact that transmitting data is often the principal energy expenditure in the application's power budget. Thus, a wide variety of communication protocols have been proposed, each targeting a unique set of specifications: communication range, data bandwidth, power consumption, latency, up/down-link transmission requirements, target transceiver cost, and so on. Focusing on the physical layer (PHY), this has led to the emergence of a large number of IoT standards (and families of standards) such as RFID, Bluetooth, LoRa, Sigfox, EnOcean, Narrow-Band IoT, EC-GSM, LTE-M, IEEE 802.15.4-2015, IEEE 802.11,

Within this huge application space, many battery-powered and energy harvesting IoT solutions require ultra low-power integrated circuits (IC), and in particular in the wireless transceiver subsystem. To reach this goal, these circuits have until now mostly been implemented using dedicated hardware designs. Unfortunately, this leads to designs with very limited wireless reconfigurability, an important drawback in the context of quickly evolving IoT standards. Proprietary communication systems or those that are dedicated to long in-field deployment life-times, such as industrial or satellite IoT, also require reconfigurability to

less transceiver subsystem. To reach this goal, these lits have until now mostly been implemented using cated hardware designs. Unfortunately, this leads to gris with very limited wireless reconfigurability, an imant drawback in the context of quickly evolving IoT

A single-chip software-defined radio-frequency (RF) transceiver is therefore highly desirable provided it respects the power budget of the IoT wireless subsystem. While unfeasible until now, several current trends, including the heterogeneous multi-core paradigm and the uptake by in-

nodes.

dustry of the easily extendable open source RISC-V ISA [8], along with the continued improvements in CMOS scaling, concur to show that this idea's time has come.

adapt to changing protocol requirements. Finally, hardware

transceivers leave little room for PHY-layer experimentation

which is necessary to drive innovation in the field of next-

cost and power consumption of DSP and FPGA technolo-

gies, new software-defined radio (SDR) applications have

recently emerged [1]. For example, authors in [2] and [3]

use FPGA platforms to build agile cellular transceivers,

from 3G to 5G. The recent development of small and nano-

satellite systems has spurred interest in SDR for space-

borne multimode transceivers [4], [5], [6]. Closer to our

application, authors in [7] propose a reconfigurable IoT gate-

way able to address the multiplicity of IoT communication

standards. Unfortunately, the power consumption figures of

such systems, which typically couple a DSP and/or FPGA

chip for baseband and/or digital front-end processing with

an RF/analog front-end chip, are orders of magnitude above

those required by most IoT endpoints. This is due both to

the energy cost of transmitting signals between integrated circuits but also, and more importantly, to the fact that these

circuits generally offer too much reconfiguration potential

and are therefore over-specified for energy constrained IoT

Thanks to the important improvements in performance,

generation radio protocols.

To this end, this work makes the following contributions:

- We identify the digital processing requirements typical of IoT wireless baseband signals;

- We propose an instruction set extension for the RISC-V ISA tailored to the needs of wireless DSP and that

<sup>•</sup> Hela Belhadj Amor is now with Dolphin Design, Grenoble, France.

Carolynn Bernier is with the Digital Systems and Integrated Circuits Department of CEA, LIST, Grenoble, France. Email: carolynn.bernier@cea.fr

Zdeněk Přikryl is with Codasip s.r.o., Brno, Czech Republic.

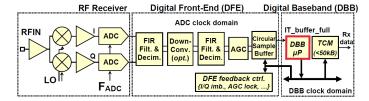

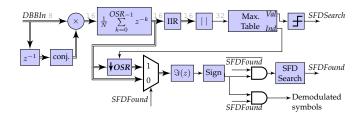

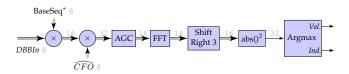

Fig. 1: Simplified architecture of software-defined RF receiver (reproduced from [9])

achieves high cycle count reductions with 'near zero' power overhead;

- Based on this new instruction set, a core dedicated to wireless DSP and that is fast and powerful enough to process complex sample streams in real-time while consuming only a fraction of the power of the complete ULP transceiver subsystem is designed;

- IoT protocol test bench simulations show important cycle count improvements with more than 50% obtained for the LoRa demodulation algorithm;

- Power consumption estimations based on post-synthesis simulations of the proposed core prove the feasibility of ultra-low power for two of the most popular IoT wireless protocols, Bluetooth LE and LoRa, and this even for one of the most computationally-intense versions of the LoRa protocol ( $SF=11,\ BW=500kHz$ ). This is achieved even without dynamic voltage scaling.

We believe that our work paves the way to making ultralow power software-defined radio a reality.

The rest of the paper is organized as follows: in Section 2, we discuss related work in the fields of ULP wireless signal processors and instruction set extensions for DSP. In Section 3, we discuss the properties of wireless DSP and the opportunity offered by the RISC-V ISA. In section 4, we present a RISC-V ISA extension for IoT signal processing. Six wireless test bench algorithms are described in Section 5 and evaluation results using the proposed architecture are presented in section 6.

#### 2 RELATED WORK

#### 2.1 Processors in the IoT landscape

In an embedded IoT platform, the application processor is responsible for executing the IoT application's task, e.g. read, store, process and decide when to transmit the sensor data. The large diversity of IoT applications and their often extreme demands in terms of power efficiency has spurred the development of a wide range of application processors. Even if we limit the discussion to those employing a variant of the RISC-V ISA, it is possible to find IoT processors targeting a power consumption in the nW range for battery-less applications [10], cores targeting the  $\mu$ W and mW range [11], cores specifically designed for flexibility over the 2-200 MHz range [12], and multi-core platforms targeting computing intensive edge applications [13].

In addition to this diversity, a recent trend has consisted in the development of heterogeneous, multi-core IoT platforms [11], [14], [15], [16] capable of offloading specific, high intensity tasks from the main application processor (e.g. security features, deep learning algorithms).

Since the processing of wireless signals is particularly demanding (to the point where it has historically typically been done using dedicated hardware), the trend towards heterogeneous multi-core platforms is an opportunity which can potentially also be seized by software-defined wireless transceivers. The challenge of developing such a tailor-made core capable of meeting the hard real-time constraints and high complexity of wireless DSP in an ultra-low power context is the focus of this present work.

#### 2.2 A tailor-made core for ULP wireless DSP

If, traditionally, the digital processing blocks in ULP transceivers have been implemented using dedicated or reconfigurable hardware, replacing these blocks by a processor implies carefully studying the energy cost of moving to software. This move to software has long been studied in high-end communication systems such as cellular and high data-rate systems where the flexibility required to address multiple communication standards has been a long-time requirement [17], [18], [19].

For ULP transceivers, where the power budget allowable to the processing of the digital baseband (DBB) signals is on the order of hundreds of  $\mu W$  to a few mW, the need for flexibility has partly been addressed by reconfigurable designs compatible with a limited number of wireless standards, typically two or three, often by sharing hardware blocks [20], [21], [22], [23]. Thus the ULP design space is still far from having achieved the flexibility offered by the software defined radio (SDR) paradigm, limiting the deployment potential of a given design in terms of addressable standards but also limiting the potential to create and deploy new digital baseband algorithms.

Conscious of this need, dedicated micro-architectures for ULP SDR have recently been proposed by [24] and [25]. To achieve ultra-low power, both of these approaches focus on the reduction of the SDR processor's working frequency. To this end, [24] proposes an architecture based on a custom Single Instruction Multiple Data (SIMD) unit, with a datapath that can be reduced to very small bit widths (4 or 8 bits), associated to a scalar unit. A different approach is explored in [25] which presents a 32-bit scalar architecture with application-specific instructions that reduce the number of required instructions from 10 to 4 for a typical frame detection algorithm. In both of these works, the choice of designing a dedicated machine implies that algorithms must be hand-coded in machine specific assembly code. This excludes the reuse of widely available software tool chains and DSP libraries. An alternative approach was proposed in our previous work [9] with a strategy based on small general purpose micro-architectures (including RISC-V). Thanks to advanced CMOS scaling and sufficiently high clocks, we showed that a timing and power consumption performance compatible with ULP IoT protocols can be achieved on these platforms, even without voltage scaling. However, these results were obtained for a relatively simple, mostly real-valued wireless test bench. Other IoT signaling protocols require higher computational resources due to the extensive use of complex signals. To address these higher complexity protocols, this present work exploits processor ISA customization.

A tailor-made core for ULP SDR therefore must be fast and powerful enough to process, in real-time, the complex sample stream produced (in RX) or required (in TX) by the transceiver front-end, while consuming only a fraction of the power of the complete transceiver subsystem, i.e. on the order of hundreds of µW to a few mW. To take advantage of the variations of complexity over time, the core must be able to put itself to sleep, ideally in a single cycle, while waiting for the next available block of samples. To further minimize power, the ROM section of the core's TCM (Fig. 1) should be implemented using either low-retention-current SRAM or using a high-speed embedded non volatile technology. In this way, the core's voltage supply can be switched off between successive frame transmissions (relatively rare in IoT systems). This also means that the core does not need to be optimized for leakage.

#### 2.3 Instruction set extensions for DSP

While the idea of extending the ISA of a processor to customize for a specific application is not new, in each case, the challenge consists in finding the optimal set of useful instructions. In the ultra-low power context which is ours, the challenge is further increased by ensuring that the proposed set comes at a near-zero power cost. Finally, the hard real-time constraints specific to wireless DSP must imperatively be met, implying that the speed burden imposed by the larger extended core must be acceptable.

The RISC-V instruction set architecture (ISA) is a standardized and open architecture specifically designed to support extensive user-level ISA extensions and specialized variants [8]. The RISC-V ISA is defined as a base integer ISA, which must be present in any implementation, plus optional standard and non-standard extensions. The base ISA is carefully restricted to a minimal set of instructions allowing for extremely energy efficient hardware implementations. Thus, highly energy efficient application-specific processors can be designed by adding a set of carefully chosen extensions, either standard or non-standard, to the base ISA. Partial customization of a standard ISA lowers the design effort to develop the necessary software tools, allows the use of a known, well tested architecture as a starting point to the new design and simplifies the reuse of existing DSP libraries.

For these reasons, the authors in [26] propose a RISC-V extension to the RV32IM ISA (32-bit integer base ISA with multiplication extension) for SDR. Similarly as in this work, the authors propose a set of custom instructions to accelerate complex-number arithmetic. To represent the real and imaginary parts of a complex number without changing the addressing mode and data width, 32-bit complex-data words are considered vectors of two 16-bit words. While the authors propose a number of instructions that are useful in typical complex DSP algorithms, such as complex ADD/SUB/MUL as well as complex radix-2 butterfly, this last being extensively used in FFT algorithms, the need for instructions such as CSMUL (complex-scalar multiply), CONJ (complex conjugate) or packed 8-bit arithmetic are questionable, as will be discussed below. By limiting the dynamic range of their instructions to 16 bits, the authors limit the applicability of their extension to low to medium

sensitivity protocols. Finally, no discussion on the impact of these new instructions on the processor's power consumption is provided.

At the time of this writing, the RISC-V community is considering the standardisation of a "P" extension intended for DSP acceleration and which includes packed-SIMD instructions targeting the segmentation of the integer registers into either two 16-bits or four 8-bits words. Packed-SIMD instructions require modifying the ALU to simultaneously work on vectors of two or four elements. Unfortunately, typical DSP ISA extensions, such as the one provided by [27] have a large instruction count, potentially larger than the base RISC-V ISA, implying a prohibitive energy cost. And of this large number of instructions, many are of little practical use in RF algorithms, as will be discussed below.

An alternative RISC-V extension is proposed in [28] targeting the processing of IoT real sensor data. The number of additional instructions is intentionally limited in order to minimize the impact on the core's power consumption (only +9% overhead with respect to the base RISC-V design.) As discussed at length in our previous work [9], the vectorial hardware extensions proposed are of limited interest for complex (versus real) data and the proposed hardware loop mechanism can rarely be used in our algorithms which typically contain conditional branches. However, for completeness, we included comparative results using this architecture in Tables 3 and 5. Our work in [9] also contains a detailed analysis of the advantages of RISC-V-based architectures over ARM-based ones for our targeted application.

## 3 WIRELESS BASEBAND DIGITAL SIGNAL PROCESSING

In this section, we introduce the background information related to wireless digital signal processing necessary for understanding the design strategy developed in Section 4. Indeed, a deep understanding of the requirements of such algorithms is required to design a minimal set of useful instructions.

#### 3.1 Software-defined ULP receiver architecture

Focusing on the receiver, which is computationally more complex than the transmitter, a software-defined RF architecture for ULP IoT signaling schemes is proposed in Figure 1. Indeed, while IoT PHY protocols differ in terms of modulation, signaling rate, coding scheme, etc., narrowband signaling schemes, i.e. occupying a maximum analog bandwidth on the order of a few MHz, share similar characteristics thus allowing the use of reconfigurable dedicated circuits in the RF, analog and digital front-end (DFE). The DFE performs filtering, decimation, optional down-conversion from an intermediate frequency (IF) and automatic gain control (AGC).

However, the wide variety of modulations and signaling schemes pleads for a software implementation of the baseband DSP operations required by each protocol. Placing the

1. Other important parts of physical layer receiver algorithms (deinterleaving, decoding, CRC, etc.) are not addressed in this work since they operate on demodulated data. Indeed, a DBB processor with a high frequency clock should be able to handle the delay specifications of these algorithms without difficulty.

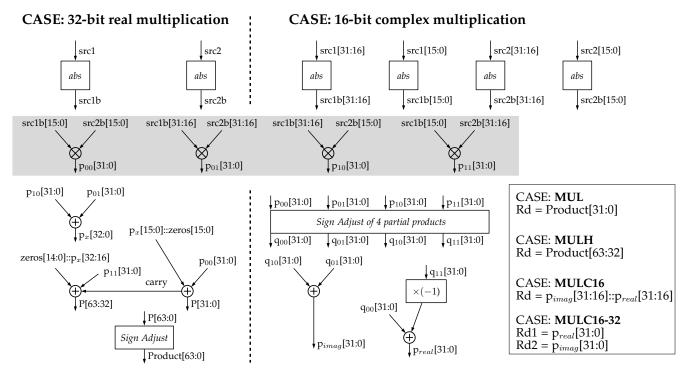

TABLE 1: Proposed ISA Extention for Wireless DSP

| Mnemonic                                   | Instruction                                         | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDC16 rd, rs1, rs2, imm                   | 16-bit Addition & Shift Right                       | rd.L = (rs1.L + rs2.L) >> imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ADDC101d, 181, 182, IIIllit                | Arithmetic Immediate                                | rd.H = (rs1.H + rs2.H) >> imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SUBC16 rd, rs1, rs2, imm                   | 16-bit Subtraction                                  | rd.L = (rs1.L - rs2.L) >> imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 50 50 10 10, 101, 102, Hilli               | To bit subtraction                                  | rd.H =(rs1.H - rs2.H)>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CRASC16 rd, rs1, rs2, imm                  | 16-bit Cross Add & Sub                              | rd.L = (rs1.L + rs2.H)>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                            |                                                     | rd.H = (rs1.H - rs2.L)>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CRSAC16 rd, rs1, rs2, imm                  | 16-bit Cross Sub & Add                              | rd.L = (rs1.L - rs2.H)>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                            |                                                     | rd.H = (rs1.H + rs2.L)>>imm<br>rd.L = rs1.L>>rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SRAC16 rd, rs1, rs2                        | 16-bit Shift Right Arithmetic                       | rd.H = rs1.H>>rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                            | _                                                   | rd.L = rs1.L>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SRAIC16 rd, rs1, imm                       | 16-bit Shift Right Arithmetic Immediate             | rd.H = rs1.H>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                            |                                                     | rd.L = rs1.L< <imm< td=""></imm<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SLLIC16 rd, rs1, imm                       | 16-bit Shift Left Logical Immediate                 | rd.H = rs1.H< <imm< td=""></imm<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MUL2ADD16-32 rd, rs1, rs2, imm             | Two "16x16" and Signed Addition                     | rd = [(rs1.L * rs2.L) + (rs1.H * rs2.H)]>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                            | if C=0: 8-bit complex multiplication,               | if $Hx = 1$ , $\{ix,qx\} = \{rsx.B2,rsx.B3\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MULC8-16 rd, rs1, rs2, H1, H2, C, imm      | conj=1                                              | if $Hx = 0$ , $\{ix,qx\} = \{rsx.B0,rsx.B1\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WOLC6-10 10, 181, 182, 111, 112, C, IIIIII | if C=1: 8-bit complex conjugate multiplication,     | rd.L = (i1 * i2 - conj * q1 * q2)>>imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                            | conj=-1                                             | rd.H = (i1 * q2 + conj * i2 * q1) >> imm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MULC16 rd, rs1, rs2, C                     | if C=0: 16-bit complex multiplication,<br>conj=1    | rd.L = (rs1.L*rs2.L)>>16 - conj*(rs1.H*rs2.H)>>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                            | if C=1: 16-bit complex conjugate multiplication,    | rd.H = (rs1.H*rs2.L)>>16 + conj*(rs1.L*rs2.H)>>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                            | conj=-1                                             | 10.11 - (151.11 152.11)>> 10 + conj (151.11 152.11)>> 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NEW CAY 22 14 12 4 2 C                     | if C=0: 16-bit complex multiplication,              | rd1 = (rs1.L * rs2.L - conj * rs1.H * rs2.H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MULC16-32 rd1, rd2, rs1, rs2, C            | conj=1                                              | ( and the state of |

|                                            | if C=1: 16-bit complex multiplication,              | rd2 = (rs1.H * rs2.L + conj * rs1.L * rs2.H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                            | conj=-1                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                            |                                                     | if $rs = 0$ , $rd = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |