# Annealing, Passivation and Contacting of Ion Implanted Phosphorus Emitter Solar Cells

Adeline Lanterne, Samuel Gall, Sylvain Manuel, Remi Monna, D. Ramappa,

M. Yuan, Pierrette Rivalin, Aurélie Tauzin

### ▶ To cite this version:

Adeline Lanterne, Samuel Gall, Sylvain Manuel, Remi Monna, D. Ramappa, et al.. Annealing, Passivation and Contacting of Ion Implanted Phosphorus Emitter Solar Cells. Energy Procedia, 2012, 27, pp.580 - 585. 10.1016/j.egypro.2012.07.113 . cea-02570730

## HAL Id: cea-02570730 https://cea.hal.science/cea-02570730

Submitted on 12 May 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Vailable online at www.sciencedirect.com

Energy Procedia 27 (2012) 580 - 585

Energy Procedia

### SiliconPV: April 03-05, 2012, Leuven, Belgium

## Annealing, Passivation and Contacting of Ion Implanted Phosphorus Emitter Solar Cells

A. Lanterne<sup>a</sup>\*, S. Gall<sup>a</sup>, S. Manuel<sup>a</sup>, R. Monna<sup>a</sup>, D. Ramappa<sup>b</sup>, M. Yuan<sup>b</sup>, P. Rivalin<sup>c</sup>, A. Tauzin<sup>c</sup>

<sup>a</sup>CEA-INES, Savoie Technolac, BP 332, 50 avenue du Lac léman, 73377 Le Bourget du Lac Cedex France <sup>b</sup>Varian Semiconductor Equipment, Applied Materials, 3050 Bowers Avenue, Santa Clara, CA 95054 United States <sup>c</sup>CEA-LETI, 17 rue des martyrs, 38054 Grenoble Cedex 9 France

#### Abstract

Recently, ion implantation doping technique has shown potential to improve silicon solar cell efficiency while reducing the number of process steps. In this context, we developed and studied a p-type silicon solar cells fabrication process with a phosphorus implanted emitter. The process is similar to the POCl<sub>3</sub> homogeneous diffusion process however replaces the high temperature gaseous diffusion and associated steps by an implantation step followed by an annealing to activate phosphorus dopants. We employed simulation results and advanced characterization to optimize the annealing temperature. The influence of this annealing temperature on the activated dopant profiles and on the crystal damage was highlighted. By adding an  $O_2$  flow during the annealing step, a SiO<sub>2</sub> layer was grown and an optimum SiO<sub>2</sub>/SiNx stack was used to improve passivation. Its benefits were quantified by comparison with the standard SiNx passivation. The influence of the implantation dopant density on the passivation quality was also studied. By using an adapted front screen-printed silver paste to contact this new implanted emitter profile we demonstrated an 18,73% certified solar cell efficiency on industrial 156x156 mm<sup>2</sup> pseudo square substrate.

© 2012 Published by Elsevier Ltd. Selection and peer-review under responsibility of the scientific committee of the SiliconPV 2012 conference. Open access under CC BY-NC-ND license.

Keywords: solar cells; ion implantation; phosphorus; passivation; thermal annealing; screen-printing

<sup>\*</sup> Corresponding author. Tel: +33 479 444 600

E-mail address: Adeline.LANTERNE@cea.fr

#### 1. Introduction

The idea of using ion implantation doping for solar cells fabrication appears in the 1980's [1], but it's only since the last year that its benefits in term of low \$/W solution were demonstrated by both a reduction of the cost of ownership and an improvement of cells performances [2,3]. As compared to the standard POCl<sub>3</sub> diffusion process, ion implantation allows to reduce the number of technological steps and to improve the quality of the emitter [4]. POCl<sub>3</sub> diffusion step and the phosphosilicate glass (PSG) removal (grown during diffusion) are replaced by a phosphorous ion implantation step followed by an activation annealing step. As implantation doping allows accurate control of dopants concentration. By decreasing the phosphorous surface concentration, the blue response can be improved thanks to the reduction of Auger recombination [5]. This doping technique also enhances the doping uniformity, the repeatability of the process and improves the emitter passivation by growing a high quality thermal oxide layer for free during the annealing step.

This paper successfully optimizes the main steps of the process, by advanced characterizations and simulations. First we focused on the annealing step to activate dopants and heal crystal damages, then on the SiO<sub>2</sub>/SiNx stack passivation quality and finally on the screen-printing metallization.

#### 2. Activation annealing temperature study

Industrial 156x156mm<sup>2</sup> p-type pseudo-squares Cz wafers with bulk resistivity of 8  $\Omega$ .cm were implanted with phosphorus ion on the VSEA "Solion<sup>TM</sup>" implanter after a KOH texture. Typical implantation doses were between 3E15 at.cm<sup>-2</sup> and 6E15 at.cm<sup>-2</sup> with implantation energies ranging from 5 KeV to 30 KeV. The wafers were then annealed during 1 hour at different temperatures from 780°C to 950°C with a step of dry oxidation. The emitter sheet resistances (R<sub>sheet</sub>) of the wafers were measured using a 4-point probe (Fig. 1). As expected the R<sub>sheet</sub> decreases when the temperature increases due to deeper diffusion of the dopant.

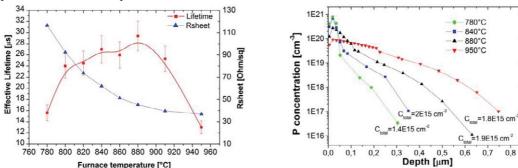

Fig. 1.  $R_{sheet}$  and effective lifetime at  $1.10^{16}$  cm<sup>-3</sup> minority carrier density, of the implanted emitter versus furnace temperature.

Fig. 2. Activated phosphorus concentration profile at different annealing temperatures measured by ECV.

Electrochemical Capacitance Voltage (ECV) profilings were performed on the sample, after removing the thermal oxide from the emitter, to obtain the activated phosphorus concentration profiles at different temperatures (Fig 2). The profiles show an acceleration of the diffusion with the temperature, leading to less concentrated at the surface and deeper profiles. The total concentration of activated phosphorus ( $C_{total_P}$ ) was calculated by integrating the ECV-curves. It increases between 780°C and 840°C (from 1,4.10<sup>15</sup> cm<sup>-2</sup> at 780°C to 2.10<sup>15</sup> cm<sup>-2</sup> at 840°C) showing the activation of more and more dopants. This

phenomenon seems to stop above 840°C where a slight decrease of  $C_{total P}$  is measured. Therefore the decrease of the  $R_{sheet}$  with the temperature is due to an increase of the the total concentration of activated phosphorus dopants up to 840°C and is only due to an increase of the electron mobility above 840°C. The mobility increases because for these high dopants concentrations, dopants act as scattering points and when the temperature increases, the dopants concentration and so the scattering points decrease [6].

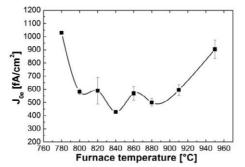

Fig. 3. Emitter saturation current density (J0e) at 1.10<sup>16</sup> cm<sup>-3</sup> minority carrier density versus furnace temperature.

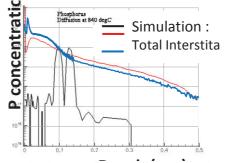

Fig. 4. Phosphorus and interstitials profiles after ion implantation and furnace annealing with oxidation at 840°C.

The effective minority carrier lifetime and the emitter saturation current density  $(J_{0e})$  were measured by quasi-steady state photoconductance (QSSPC) method on symmetrically doped (double side implanted) and passivated wafers also annealed at the same temperatures (see Fig. 1 and 3). The lifetime improves with an increase of the temperature up to 880°C beyond which it appears to degrade. This first improvement is partly due to the decrease of the J<sub>0e</sub> values up to 840°C, which corresponds to a reduction of the emitter recombination sites with the phosphorus activation. Simulations were made to further correlate this lifetime evolution with the crystal damages.

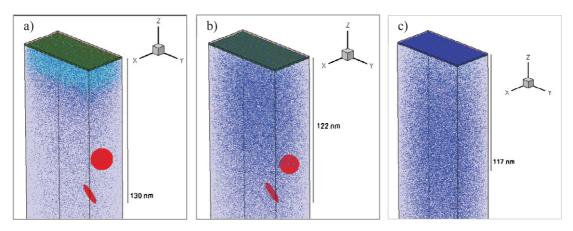

Sentaurus PROCESS simulations of the implantation step followed by the annealing and oxidation step were performed by Kinetic Monte Carlo modeling (KMC). The final position of clusters, dislocation loops and phosphorus atoms in the volume is shown on Fig. 5, (z direction corresponds to the depth of the substrate). The number of clusters (mainly inactive phosphorus atoms) decreases for each raise of the temperature, starting from 26600 clusters for an annealing at 780°C up to only 270 clusters for a 950°C annealing. This decrease improves the ratio of activated dopants at high annealing temperatures. Large dislocations loops (20nm) are also created during the first ramp-up of the annealing and disappear with increasing annealing temperatures. To estimate the concentration of interstitial in the dislocation loops, a section of the volume was made to extract the phosphorus and interstitial profiles, they are compared to the SIMS profiles at 840°C on Fig. 4.. Two interstitials concentration peaks of 1.10<sup>20</sup> cm<sup>-3</sup> are observed at the dislocation loops positions.

To summarize, the quality of the emitter improves with the temperature upto  $880^{\circ}$ C due to a higher rate of activated dopants and to a decrease of the dopants surface concentration. However the lifetime degradation for anneals above  $880^{\circ}$ C (shown in Fig. 1) cannot be explained by the simulation as it shows no residual defects. The decrease of the J<sub>0e</sub> above 900°C is a first contribution to this degradation but similar lifetime degradations were also measured on undoped bulk Cz control wafers annealed at 950°C and described in [6]. Temperatures below 880°C were chosen for the experimental part.

Fig. 5. Sentaurus Process simulations of a P implantation followed by an annealing at 780°C (a) at 880°C (b) and at 950°C (c). Cyan points correspond to phosphorus clusters, blue points to point defects (mainly substitutional phosphorus atoms) and red area to dislocation loops

#### 3. SiO<sub>2</sub>/SiNx Passivation

#### 3.1. Thickness optimization

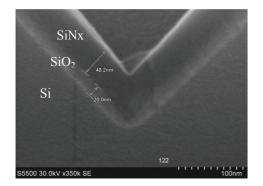

A high quality thermal oxide layer was grown on the emitter by adding an  $O_2$  flow during the annealing step. Its thickness was chosen between 10nm and 30nm by changing the oxidation time to improve the passivation without impacting the reflectivity [7]. SiO<sub>2</sub> and SiNx layer thicknesses were optimized by simulations until the minimum of reflectivity corresponds to a 600nm wavelength. For example, a 20nm oxide grown requires a 48nm nitride layer as shown in Figure 6.

Since the SiO<sub>2</sub> layer was grown on a highly doped emitter, its growth rate increased with the surface doping concentration [8]. As a consequence, if the implantation dose is reduced, the SiO<sub>2</sub> thickness decreases. In that case, either the oxidation time or the SiNx deposition time has to be adapted to maintain the minimum of reflectivity on 600 nm.

Fig. 6. MEB picture of the SiN/SiO2 passivation layers

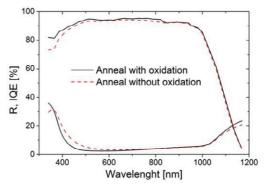

Fig. 7. IQE and reflectivity measurements on a 62 Ohm/sq implanted emitter with and without oxidation

#### 3.2. SiO<sub>2</sub>/SiN Stack benefits

The benefits of this added SiO<sub>2</sub> layer was quantified by the fabrication of complete solar cells with and without oxidation. Illuminated I-V characterization (AM1.5) reveals an improvement of both current and voltage with a SiO<sub>2</sub>/SiNx stack (+5mV of V<sub>oc</sub> gain and +0,8mA/cm<sup>2</sup> of J<sub>sc</sub> gain). The V<sub>oc</sub> improvement is explained by improved passivation of the SiO<sub>2</sub>/SiN stack as compared to the SiNx alone. This is more clearly seen in the IQE measurement (Fig. 7), which shows an improvement of the blue response with oxidation. Figure 7 also explains a part of the J<sub>sc</sub> improvement with the decreasing of the reflectivity under 700nm.

#### 3.3. Implantation dose influence

The implantation doses influence on the  $J_{0e}$  and the implied  $V_{oc}$  was studied. Three doses (A, B and C) between 2E15 at/cm<sup>2</sup> and 6E15 at/cm<sup>2</sup> were implanted with A > B > C. The first consequence of changing the implant dose is an increasing of the sheet resistance of the emitter (see Table 1).  $V_{oc \text{ implied}}$  at one suns and  $J_{0e}$  at 1E16 cm<sup>-3</sup> minority carrier density were measured on double side implanted and passivated wafers by QSSPC method. For each dose, the SiNx thickness was optimized. The measured values of the  $V_{oc \text{ implied}}$  and  $J_{0e}$  confirm the passivation improvement with +7mV between A and C doses.

Table 1. Implantation dose influence on  $R_{sheet}$ ,  $J_{0e}$  and  $V_{oc implied}$

| Dose | $R_{sheet}$ (Ohm/sq) | $J_{0e}$ (fA.cm <sup>-2</sup> ) | $V_{oc\ implied}\ (mV)$ |

|------|----------------------|---------------------------------|-------------------------|

| А    | 62                   | 540                             | 634                     |

| В    | 71                   | 334                             | 637                     |

| С    | 79                   | 302                             | 641                     |

#### 4. Front screen-printing (SP) paste

The next challenge is then to contact these low doped emitters. Metallization process optimization was performed by optimizing the silver paste.

The front SP silver paste has to pass through both passivation layers to contact the emitter without shunting the junction. As the implanted emitter profile is less concentrated at the surface and deeper than the diffusion doped emitter profile, the front SP paste has to be adapted. Different front pastes were tested. The contact resistivity was measured by Berger's method [9] on diffusion and implanted emitters for each paste. As shown in Table 2, the contact resistivity increases with the standard paste for implanted emitter as compared to diffused emitter. By employing a front Ag paste adapted to lower doped emitter we were able to reduce the contact resistivity and increase by  $13\%_{abs}$  the field factor (FF) leading to a FF of 77,9 %.

Table 2. Front SP paste comparison on diffusion and implant emitter

| Doping technique            | Front SP Paste | Contact resistivity (Ohm.cm <sup>2</sup> ) | FF (%) |

|-----------------------------|----------------|--------------------------------------------|--------|

| POCl <sub>3</sub> Diffusion | Standard       | 3,4.10 <sup>-3</sup>                       | 78.4   |

| Implantation                | Standard       | 9.10 <sup>-2</sup>                         | 65     |

| Implantation                | Adapted        | 3,6.10 <sup>-3</sup>                       | 77.7   |

With this adapted front paste, 3 batches of wafers were processed. A very good repeatability of the results was obtained with an average efficiency over 18,44% for each batch and a best solar cell certified by FhG-Callab at **18,73%** (Fig. 8).

Fig. 8. I-V curve of the 18,73% cell measured by FhG-Callab

#### 5. Conclusion

Our investigation of phosphorous emitters formed by implantation process has highlighted an optimum effective lifetime regime upto 880°C annealing temperature. This improvement was correlated with an increase of the activated dopants ratio and a decrease of the dopants surface concentration as compared to a phosphorous emitter formed by POCl<sub>3</sub> diffusion. We demonstrated the improved passivation effect of an oxide layer on the emitter, its impact on improved blue response in the cell, and the resultant improvements in voltage and currents. We pointed out the need for an adapted front SP paste to achieve good contact of implanted emitters. We were able to derive high efficiency solar cells with efficiencies of 18.73%. Further optimization should exceed 19% in the near future.

#### References

[1] M.B. Spitzer, S. P. Tobin, C. J. Keavney, IEEE Transaction on Electron Devices, ED 31, 546-550 (1984)

[2] A. Rohatgi & D. Meier, Photovoltaic International Journal 88-93 (2010).

[3] Yelundur, B. Damiani, V. Chandrasekaran, A. Adedokun, A. Payne, X. Wang, & al., 26th European Photovoltaic Solar Energy Conference and Exhibition, 831-834, (2011)

[4] R. Low, A. Gupta, N. Bateman, D. Ramappa, P. Sullivan, W. Skinner, & al., Photovoltaic Specialists Conference (PVSC), 2010 35th IEEE, 001440 - 001445 (2010)

[5] J. Dziewior, W. Schmid, Applied Physics Letters, 31 (5), 346-348 (1977)

[6] H.Boo, J-H. Lee, M. Gu Kang, K. D. Lee, S.Kim, H. C. Hwang, & al., International Journal of Photoenergy, Vol. 2012, ID 921908 (2012).

[7] J. Zhao, A. Wang & M. A. Green, IEEE Transaction on Electron Devices, 41(9), 1592-1594 (1994).

[8] H. Sunami, J. Electrochem. Soc. Solid-State Science and Technology, 125(6), 892-897 (1978).

[9] H. H. Berger, J. Eletrochem. Soc. 119 (4), 507-514 (1972).