## Application of temporary adherence to improve the manufacturing of 3D thin silicon wafers

K. Abadie, P. Montmeat, T. Enot, F. Fournel, M. Wimplinger

### ► To cite this version:

K. Abadie, P. Montmeat, T. Enot, F. Fournel, M. Wimplinger. Application of temporary adherence to improve the manufacturing of 3D thin silicon wafers. International Journal of Adhesion and Adhesives, 2019, 91, pp.123-130. 10.1016/j.ijadhadh.2019.03.009 . cea-02186447

### HAL Id: cea-02186447 https://cea.hal.science/cea-02186447

Submitted on 22 Oct 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial 4.0 International License

# APPLICATION OF TEMPORARY ADHERENCE TO IMPROVE THE MANUFACTURING OF 3D THIN SILICON WAFERS

K. Abadie<sup>1</sup>, P. Montméat<sup>2,3</sup>, T. Enot<sup>2,3</sup>, F. Fournel<sup>2,3</sup>, M. Wimplinger<sup>1</sup>

<sup>1</sup>EVGroup, DI Erich Thallner Strasse 1, 4782 St. Florian/Inn, Austria

<sup>2</sup>Univ. Grenoble Alpes, F-38000 Grenoble, France

<sup>3</sup>CEA, Leti, Minatec Campus, F-38054 Grenoble, France

#### Abstract

The presented work concerns the manufacturing of very thin silicon wafers for a 3D Integrated Circuit industrial purpose. One of the key parameters of the 3D integration is the adherence of the bonded structure which involves silicon wafers and a polymer adhesive as an intermediate layer. The scope of the paper is to determine the suitable adherence of the stack for a successful manufacturing onto industrial tools. For this purpose the dismounting capacity of the fully automated equipment EVG®850DB depending on the adherence energy is studied. Direct and polymer bonded silicon pairs are prepared. Their energies of adherence cover a large range of energy: from 0.3 to 14 J/m<sup>2</sup>. The automatic mechanical dismounting process is successful when the stack adherence is  $1.2 \text{ J/m}^2$  or lower. This value does not depend on the bonded structure type: direct bonded pairs or thinned polymer bonded pairs exhibit the same behavior regarding the dismounting capacity. And we demonstrate that the industrial manufacturing of 70 µm thin silicon wafers is possible if the adherence is  $0.4 \text{ J/m}^2$  to  $1.2 \text{ J/m}^2$ .

#### 1. Introduction

Industrial processes addressing the handling of ultra-thin wafers have been a major topic ever since it became clear that they are vital to a multitude of semiconductor applications such as MEMS, compound semiconductors, LEDs, fan-out WLP, CMOS image sensors (CIS) and, most recently, 3D-IC using TSV interconnects. And the thickness of the wafer is from 50 up to 200  $\mu$ m. Device manufacturing flows utilizing thinned wafers generally require temporary bonding onto a rigid carrier substrate to address the handling issues encountered with thin wafers. The rigid carrier substrate prevents fracture, warping, and folding of the device wafer. The device thinned wafer is separated from the carrier at the end of the integration process flow. The temporary adherence of the bonded structure appears as a key parameter of the 3D integration. The adherence has to be high enough to withstand the mechanical effort of back side processes and has to be weak enough to allow a safe separation (dismounting) of the bonded structure at the end of the integration. The goal of this study is to determine the process window in terms of temporary energy of adherence, using 300 mm silicon wafers in an industrial environment.

While significant technological progress has been made to guarantee reliable backside processing of thinned wafers<sup>i ii iii iv v vi</sup>, the dismounting step at the end of the process flow remains a key challenging step and various technologies have been developed:

- Laser dismounting : 3M®vii, TOK®viii or Shin-Etsu®ix,

- Room temperature dismounting : ZoneBOND®x xi and BrewerBOND®xii

- Thermal dismounting xiii xiv xv

The study focuses on the room temperature dismounting. In that case, a mechanical effort allows the separation between the carrier and the thin silicon wafer. A thermoplastic

adhesive is often used and a removal layer can be added to ensure an easy separation. After the dismounting, a cleaning step of the adhesive is necessary. In this field, EVGroup has developed the fully automated equipment EVG®850DB including a mechanical dismounting module.

The study falls into 2 parts.

First, the maximum temporary adherence is determined. The feasibility of dismounting onto the automatic equipment is discussed through the adherence of the bonded structure. To that end, direct bonded wafers and polymer bonded wafers are prepared with a large range of adherence energy. For both, temperature can be used as a parameter for controlling the adherence energy<sup>xvi xvii</sup> xvii.

Secondly, thin silicon wafers are manufactured with an antisticky layer to estimate the minimum temporary adherence. The bonding process is carried out with a polymer adhesive and a removal layer based on a fluorinated material.

#### 2. Experiments

All silicon wafers used in this paper are 300 mm silicon wafers. The initial thickness is 775  $\mu$ m.

#### 2.1 Polymer bonded structures

The adhesive is the Brewer BsiT09001A polymer. This is a commercial thermoplastic adhesive. It is decided to use the effect of the bonding temperature from 130°C to 250°C to alter the adherence energy for the study of the dismounting process.

$55 \,\mu\text{m}$  of adhesive are spin coated and cured onto the 300 mm silicon wafer. The bonding with another Si wafer is performed within an EVG®560 tool. In the bonding chamber, after evacuating the air bubbles and the residual solvent of the glue at a given temperature and  $10^{-5}$  mbar a bonding force of 6kN is then applied to the structure for 3 min.

Two bonded pairs are processed for each dismounting test performed later: one for bond strength measurement, one for thinning in order to generate the thin silicon wafer to be dismounted. The thinning of one silicon wafer of the bonded structure is done by a grinding process. The Si wafer is ground down to 80  $\mu$ m. The grinding is performed on a Disco Grind Polishing tool. A Z1 wheel (coarse grinding), a Z2 wheel (fine grinding) and finally a Z3 wheel (dry polishing) are used for thinning the silicon wafer. An edge-trimming at 1.5 mm is performed on a Disco Full Dicing tool with a 100  $\mu$ m width blade.

#### 2.2 Direct bonded structures

Two different kinds of 300 mm direct bonded wafers – hydrophilic  $(SiO_2/SiO_2)$  and hydrophobic (Si/Si) – are prepared.

After chemical cleaning, two silicon wafers with 145nm of thermal oxide are bonded under vacuum for the preparation of hydrophilic SiO<sub>2</sub>/SiO<sub>2</sub> bonded pairs, using an EVG®850LT equipment. Si/Si hydrophobic bonded pairs are also prepared using the same bonding process, but with a different chemical surface preparation: in this case, an HF-last precleaning is performed.

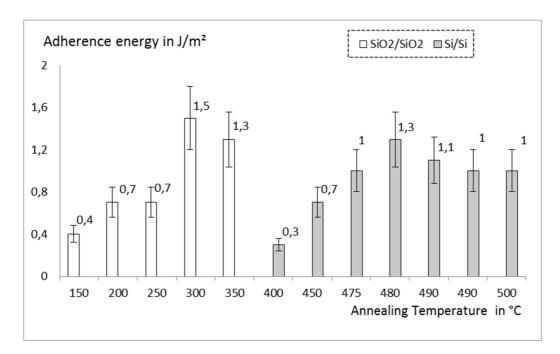

The bond strength must be predicted and controlled for the goals of the study. The dependence of bonding energy values versus the post bonding annealing temperature are already available in the literature <sup>vx xvi</sup>. Thus, the bonded structures are annealed at different temperatures depending on the direct bonded pair types in order to generate bonded pairs with different adherence energies. In the case of hydrophilic bonded pairs, an annealing process of 2 hours is performed at temperatures varying from 150°C to 350°C with 50°C

steps. In the case of hydrophobic bonded pairs, all the bonded pairs are firstly annealed at 400°C, with 3 hours steps at 100°C, 200°C, and 300°C, and a heating ramp of 0.75°C/min between steps. This first annealing step is used to avoid any bonding defect generation<sup>xix</sup>. Then, further annealing treatments are performed varying from 450°C to 500°C every 10°C.

#### 2.3 Acoustic microscopy

Acoustic microscopy is used to evaluate the quality of the bonding with a fully automatic SAMAuto PVA TEPLA acoustic microscope with an acoustic head frequency of 140 MHz.

#### 2.4 Adherence energy measurement

The adherence energy of the bonded stacks is obtained by the double cantilever beam (DCB) technique as described by Maszara <sup>xx</sup>. It relies on a blade insertion at the bonding interface. The measurements are performed in a clean room humid atmosphere in order to keep the impact of the water stress corrosion <sup>xv</sup>. Indeed, during the mechanical dismounting, the water stress corrosion will be involved. In case of direct bonded pairs, beams (2 cm width) are diced in the bonded pairs before annealing for more accurate results as the Maszara equation are made for beams and not for round wafer shape. In case of polymer bonded pairs, the dicing process may affect the adherence by annealing the polymer. Thus the adherence energy is evaluated from the full 300 mm wafers. In that case, for the calculation of the adherence energy, at first order, the geometrical effect is not taken into account. The polymer effect is also not considered (thickness and elastic properties)<sup>xxi</sup>. In case of thinned structures, we also postulate that the grinding process does not modify the adherence energy.

#### 2.5 Dismounting process

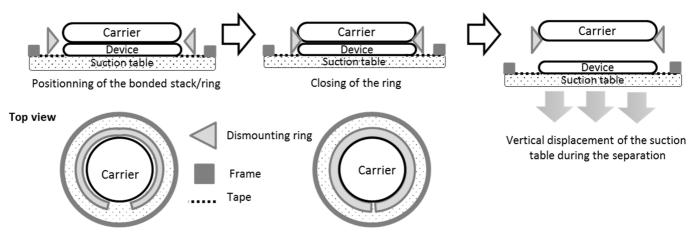

The EVG®850DB installed at CEA-Leti is devoted to mechanical dismounting processing. The bond pair is laminated on a frame with an adhesive tape thanks to an automatic laminator. The Furukawa tape SP-537T-230 is used on a 450 mm DISCO frame (thinned or device wafer stuck onto the tape). The system {frame + tape + bond pair} is brought to the dismounting station which includes a specific clamping ring used to securely hold the carrier wafer and to enable its separation from the device. The role of the clamping ring as well as the dismounting process are is illustrated in figure 1. The fragile thinned wafer mounted onto a frame is fixed onto the suction table. A vertical displacement of the suction allows the dismounting of the carrier. In the case of adhesive bonding, the dismounted part {frame + tape + device} is transferred into a wet cleaning station for the next process step which is targeted at removing the residual adhesive layer.

**Cross section**

Figure 1: Dismounting process in EVG850DB

2.6 Temporary bonding process based on an adhesive

Various thin silicon wafers are elaborated with a temporary bonding process. This process can be split into several steps:

- A temporary silicon carrier is elaborated with a removal layer. A silicon wafer is coated with a fluorinated polymer: Novec EGC 2702. The coating process is described in our previous study <sup>xxii</sup>

- Another silicon wafer (device) is coated with the Brewer adhesive BsiT09001A (55  $\mu m)$

- Both wafers are bonded together with an EVG®560 tool at 210°C, under vacuum and a force of 6 kN is applied

- The grinding of the device wafer is performed as presented in part 2.2. An edge trimming of 1.5 is done and the final target thicknesses of the thinned wafers are 250, 150 and 70  $\mu$ m.

- The dismounting of the thinned structure is done with an EVG® 850DB as presented in part 2.2. A chemical process with D-Limonene is done for removing the adhesive.

The topographies of the thin silicon wafers are evaluated with FRT Microproof® equipment. The Total Thickness Variation (TTV) value is determined as the thickness variation obtained from two 300 mm diameter profiles. No edge exclusion is used to determine the TTV value.

#### 3. Results and discussion

3.1 Polymer bonded pairs

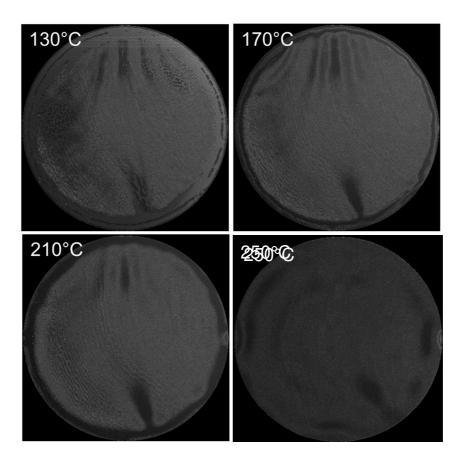

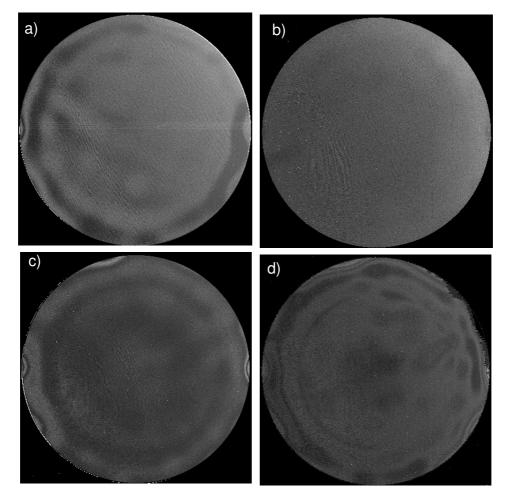

The acoustic images of various annealed stacks (130°C and 250°C) are presented in Figure 2.

Figure 2: Acoustic pictures of various polymer bonded structures

For each structure, no voids and delaminations are observed. Nevertheless, the stack obtained at 130°C exhibits a much more contrasted picture than the 250°C bonded structure. This is attributed to improved planarization enabled by lower adhesive viscosity resulting from the increased bonding temperature. However, it is checked that all bonded pairs (bonding temperature from 130°C to 250°C) do not exhibit defects at the bonding interface.

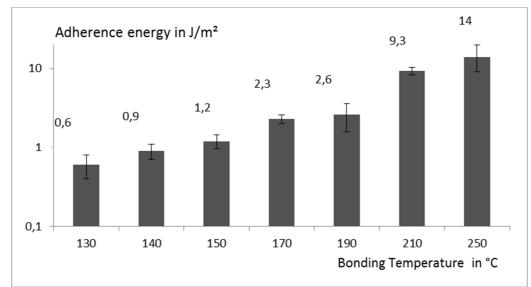

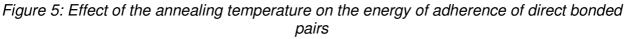

The temperature effect on the adherence energy is shown in Figure 3.

Figure 3: Effect of the bonding temperature on the energy of adherence of polymer bonded pairs

A strong impact of the bonding temperature on the adherence energy is obviously put in evidence. The energy strongly increases with increasing bonding temperature. The weakest energies (less than 1 J/m<sup>2</sup>) are obtained for bonding temperatures less than 150°C. A significant adherence energy increase is observed at 200°C where the energy reaches 9 J/m<sup>2</sup>. Such significant adherence energy has already been reported in the case of polymer bonding<sup>xxiii</sup>, <sup>xxiv</sup>, <sup>xxvi</sup>, <sup>xxvi</sup>. Basically, two phenomena can explain this behavior. First, the temperature modulates the type of chemical bonds at the bonding interface. The weakest energy involves dipolar or weak hydrogen bonds whereas the largest adherence energy (above 10 J/m<sup>2</sup>) corresponds to covalent bonds between the silicon surface and the polymer. The second phenomenon involved in this energy increase is linked to the polymer rearrangement at high temperature. High temperatures lead to a greater chain mobility and increase the number of bridging chains between the polymer and the silicon surface.

The large range of bonding adherence (0.6 to 14  $J/m^2$ ) allows determining the limit of the dismounting tool in terms of bonding energy.

The silicon wafer thinning is achieved down to 80  $\mu$ m. During the grinding, chipping appears for the stacks bonded at 130°C and 140°C. All the grinding processes performed on the stacks bonded from 150°C to 250°C are successful and no defect is observed on the thin silicon wafers. The appearance of defects at low temperature has been already discussed <sup>xix</sup> and can be attributed to a combined effect of a weak adherence and a bad planarization of the bonded structure. Nevertheless, these two damaged bonded pairs during grinding are also used for a dismounting test on the EVG®850DB.

#### 3.2 Direct bonded pairs

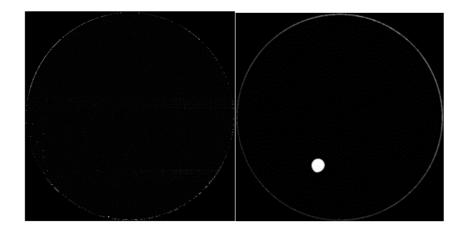

Acoustic image examples of direct hydrophobic and hydrophilic bonded pairs are presented in Figure 4.

Figure 4: Acoustic pictures of a SiO<sub>2</sub>/SiO<sub>2</sub> hydrophilic direct bonded stack (right) and a Si/Si hydrophobic direct bonded stack (left)

In the case of hydrophilic stacks (SiO<sub>2</sub>/SiO<sub>2</sub>), no defect is observed at the bonding interface. We have also checked that no more defects appear with the thermal treatment performed from 150°C up to 350°C. In the case of hydrophobic stacks (Si/Si), some small bonding defects are observed in the bonding interface (bubbles). They can be observed after a thermal treatment from 400°C up to 500°C. However, only one or two bonding defects are observed, as presented in figure 4. By choosing beams with defect-free bonding interfaces, it does not impact the bonding energy measurements. As the non-bonded area is very limited, it does not also impact the dismounting results.

The adherence energy values are presented in figure 5. For hydrophilic and hydrophobic stacks, the increase of the annealing temperature leads to an increase of the adherence energy. The behaviors are well correlated with other studies published elsewhere <sup>xv xvi</sup>. The bonding mechanisms are also identified and well known <sup>xxviii, xxix</sup>.

The dismounting feasibility can then be studied on two different structures:

- Polymer silicon bonded pairs (775  $\mu m$  and 80  $\mu m$  bonded with 55  $\mu m$  of adhesive) with an adherence of 0.6 to 14 J/m²

- Direct silicon bonded pairs (both 775  $\mu$ m) with an adherence of 0.4 to 1.5 J/m<sup>2</sup>

#### 3.3 Dismounting

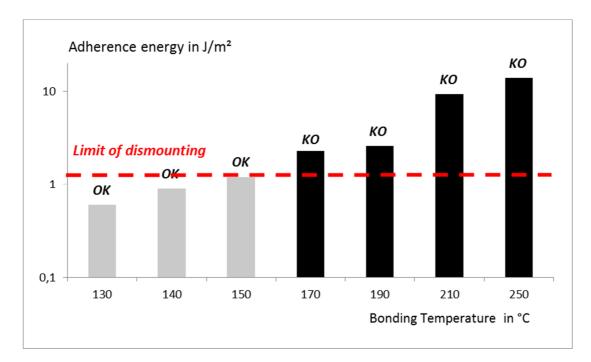

The automatic dismounting process is performed on both bonded pairs. Results are presented in Figure 6 and Figure 7.

In the case of the thinned polymer stacks (Figure 6), the dismounting is successful when the adherence energy is  $1.2 \text{ J/m}^2$  or less. For higher energies the process is stopped by the operator, because too much force is required and it may lead to breakage of both wafers during the dismounting process. When the dismounting is possible, the process is easy and safe. In particular, no defect is observed on the dismounted thin wafer obtained with a bonding temperature of  $150^{\circ}\text{C}$  ( $1.2 \text{ J/m}^2$ ).

In the case of direct bonded pairs (Figure 7), the dismounting is easy when the adherence energy is equal or lower than  $1.3 \text{ J/m}^2$ . Here again for higher energies, the process is stopped by the operator because of the risk of breakage.

Both limit values are similar and adherence energy of 1.2 J/m<sup>2</sup> seems to be the maximum bonded strength that can be reliably dismounted with the fully automated EVG®850DB equipment using 300 mm wafers.

Figure 6: Dismounting capacity of adhesive bondings in white = easy dismounting, in black = failed dismounting

Figure 7: Dismounting capacity of the bonded pairs, in white = easy dismounting, in black = failed dismounting

#### 3.4 Application to an adhesive based temporary bonding process

The acoustic picture of the bonding of the device with the carrier coated with the fluorinated polymer is presented in figure 8a. No voids are observed on the picture, which indicates that the carrier made of a fluorinated material is suitable for a 300 mm bonding process at 210°C.

The energy of adherence of the stack with the carrier is  $0,4 \text{ J/m}^2$  which is less adhesive than the stack with only silicon wafers (9,3 J/m<sup>2</sup> see part 3.1). The fluorinated polymer really acts as an antistick towards the adhesive layer. The weak value of adherence is less than 1.2 J/m<sup>2</sup> and the stack is thus supposed to be suitable for an easy dismounting.

The grinding of the bonded stacks are done down to 250, 150 and 70  $\mu$ m. All the bonded structures are able to undergo these processes: without any signs of delamination, cracking or chipping being observed on the thin wafer as shown on the acoustic pictures presented in Figure 8 b, c and d. The chosen carrier is thus compatible with a grinding process. It also indicates that the adherence of 0.4 J/m<sup>2</sup> is compatible with the mechanical effort induced during the grinding process.

Figure 8: Acoustic pictures of various 300 mm bonded structures a) after bonding, and after thinning down to b) 250μm, c) 150μm and d) 70 μm

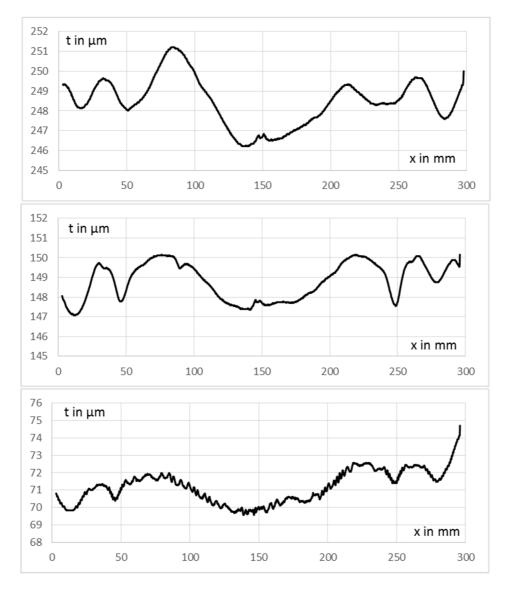

The morphologies of the thin wafers are presented in figure 9. The average thicknesses of the wafer is evaluated from two 300 mm profiles and are 248, 149 and 71  $\mu$ m for targets of 250, 150 and 70  $\mu$ m. The TTV values are respectively 5, 3 and 4  $\mu$ m for the 250, 150 and 70  $\mu$ m wafers. These values are very close and excellent. They demonstrate good thickness homogeneity of bonding and grinding processes.

Figure 9: Profiles of thin silicon wafers

The dismounting of the various stacks is very easy. Pictures of the dismounted 70  $\mu$ m thin wafer are shown in figure 10. No chipping or scale is observed on the thinned wafer. The cleaning of the glue does not break the structure any more. The dismounting of the 250 and 150  $\mu$ m wafer leads to the same results.

The carrier is thus suitable for an easy and safe automatic dismounting.

An adherence of 0.4  $J/m^2$  is suitable for a full temporary bonding process for thin wafer handling.

Figure 10: Pictures of the 70 µm wafer mounted onto a frame (left: before cleaning the adhesive and right: after cleaning the adhesive)

#### 4 Conclusion

The study deals with the manufacturing of very thin silicon wafers for 3D Integrated Circuits. The industrial manufacturing of thin silicon wafers involves a temporary bonding process with an adhesive.

The temporary adherence of the bonded structure appears as a key parameter of the process and we demonstrate that industrial manufacturing is possible if the adherence is 0,4 J/m<sup>2</sup> to 1,2 J/m<sup>2</sup>.

Otherwise, these results can be directly applied for 3D integration as a parameter for the integration flow. 1.2  $J/m^2$  represents the maximum adherence value suitable for an easy dismounting of a direct or adhesive bonded structure onto industrial equipment.

#### References

<sup>ix</sup> Seung-Woo Lee et al (2015) The effect of laser irradiation on peel strength of temporary adhesives for wafer bonding. International JournalofAdhesion&Adhesives57(2015)9–12

<sup>&</sup>lt;sup>i</sup> J. Charbonnier et al (2009) Integration of a temporary carrier in a TSV process flow, electronic components and technology conference 2009. ECTC 59:865–871

<sup>&</sup>lt;sup>ii</sup> K. Vial et al (2012) Challenges and solutions for ultra-thin (50 μm) silicon using innovative ZoneBOND<sup>TM</sup> process. Electron Packag Technol Conf (EPTC). 14:445–450

<sup>&</sup>lt;sup>iii</sup> P. Montméat et al (2015). Origin of the TTV of thin films obtained by temporary bonding ZoneBond® technology. Microsyst Technol (2015) 21:987–993

<sup>&</sup>lt;sup>iv</sup> C. Ferrandon et al (2013) Innovative wafer-level encapsulation and underfill material for silicon interposer application. Electron Compon Technol Conf (ECTC) 63:761–767

<sup>&</sup>lt;sup>v</sup> F. Niklaus et al (2003) Arrays of monocrystalline silicon micromirrors fabricated using cmos compatible transfer bonding. Jal of Micromechanical Syst 12:465

v<sup>i</sup> P. Montméat et al (2017) Study of a silicon/glass bonded structure with a UV-curable adhesive for temporary bonding applications. Microelectronic Engineering 173 (2017) 13–21

<sup>&</sup>lt;sup>vii</sup> 3M<sup>™</sup> Wafer Support System, available at http://multimedia.3m.com/mws/media/634385O/3mtm-wafer-support-system-brochure.pdf <sup>viii</sup> T. Fukushima et al (2014) Via-Last/Backside-Via 3D Integration Using a Visible-Light Laser Dismounting Technique. 4th IEEE International Workshop on Low Temperature Bonding for 3D Integration (LTB-3D), Tokyo

<sup>&</sup>lt;sup>x</sup> Q. Wang et al (2015) The effect of temporary bonding on post processing in TSV interposer manufacturing. Microsyst Technol (2015) 21:749–755

<sup>&</sup>lt;sup>xi</sup> A. Jourdain et al (2013) Integration and Manufacturing Aspects of Moving from WaferBOND HT-10.10 to ZoneBOND Material in Temporary Wafer Bonding and Dismounting for 3D Applications. 2013 Electronic Components & Technology Conference ZoneBOND® is a trademark of Brewer Science Inc., Rolla, MO, USA

xii A. Jourdain et al (2015) Single-release-layer Process for Temporary Bonding Applications in the 3D Integration Area. 2015 Electronic Components & Technology Conference

BrewerBOND® is a trademark of Brewer Science Inc., Rolla, MO, USA

xiii Ram K Trichur (2011) Thin Wafer Handling Technologies for Layer Transfer Processes in High-Brightness LED Manufacturing. Semicon WEST 2011

<sup>&</sup>lt;sup>xiv</sup> S. Pargfrieder et al (2008) Temporary Bonding and Dismounting Enabling TSV Formation and 3D Integration for Ultra-thin Wafers. 2008 10th Electronics Packaging Technology Conference

xvii Q.-Y. Tong et al Semiconductor Wafer Bonding: Science and Technology. The Electrochemical Society Series, 1999

<sup>xviii</sup> P. Montméat et al (2018) Polymer bonding temperature impact on the morphology and on the adherence energy of the bonded stack. Microsyst Technol (2018) 24:793–799

xix F. Fournel et al (2008) Low Temperature Wafer Bonding, ECS 2008 Symposium Wafer Bonding

xx P. Maszara et al (1988) Bonding of silicon wafers for silicon-on-insulator. J. Appl. Phys.64, 4943

xxi J. Guillemenet et al (2001) Crack propagation in adhesively bonded steel assemblies. Int. J. Adhes. Adhes., 21:77-83

<sup>xxii</sup> P. Montméat et al (2018) Development and adhesion characterization of a silicon wafer for temporary bonding. International Journal of Adhesion and Adhesives 82 (2018) 100–107

<sup>xxiii</sup> Kwang WO et al (2002) A low-temperature bonding technique using spin-on fluorocarbon polymers to assemble microsystems. J. Micromech. Microeng. 12 187–191

<sup>xxiv</sup> Cha D-Y et al (2010) Study on Low Temperature Bonding Technology for Optical PCB with Polymer Intermediate Layers. Journal of the Korean Institute of Electrical and Electronic Material Engineers, Vol. 23, No. 1, p. 29

<sup>xxv</sup> Shinohara H et al. (2007) Low-temperature Direct Bonding of Poly(methyl methacrylate) for Polymer Microchips. TRANSACTIONS ON ELECTRICAL AND ELECTRONIC ENGINEERING IEEJ Trans 2007; 2: 301–306

<sup>xxvi</sup> Mizuno J. et al (2005) Cyclo-olefin polymer direct bonding using low temperature plasma activation bonding. Proceedings of the 2005 International Conference on MEMS, NANO and Smart Systems

<sup>xxvii</sup> Imachi M. (1986) Effect of Bonding Temperature on The Interfacial Bonding Strength of Polyethylene / Polypropylene and Other Polymers. Journal of Polymer Science: Part C: Polymer Letters, Vol. 24, 537-540

<sup>xxviii</sup> U. Gösele et al (1999) Wafer bonding for microsystems technologie. Sensors and Actuators 74-1999, 161–168

xxix C. Ventosa et al (2008) Hydrophilic low-temperature direct wafer bonding. Journal of Applied Physics 104, 123524 (2008)

<sup>&</sup>lt;sup>xv</sup> K. Bioh et al (2009) Advanced Wafer Bonding Solutions for TSV Integration with Thin Wafers, International Conference on 3D Systems Integration (2009), pages 267-272

$x^{vi}$  F. Fournel et al (2012) Measurement of bonding energy in an anhydrous nitrogen atmosphere and its application to silicon direct bonding technology. Journal of Applied Physics, 111, 104907 (2012).