# Conditional Dispersive Readout of a CMOS Single-Electron Memory Cell

S. Schaal, S. Barraud, J. J. l. Morton, M. F. Gonzalez-Zalba

### ► To cite this version:

S. Schaal, S. Barraud, J. J. l. Morton, M. F. Gonzalez-Zalba. Conditional Dispersive Readout of a CMOS Single-Electron Memory Cell. Physical Review Applied, 2018, 9 (5), pp.054016. 10.1103/Phys-RevApplied.9.054016 . cea-02184791

## HAL Id: cea-02184791 https://cea.hal.science/cea-02184791

Submitted on 16 Jul 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Conditional Dispersive Readout of a CMOS Single-Electron Memory Cell

S. Schaal,<sup>1,\*</sup> S. Barraud,<sup>2</sup> J. J. L. Morton,<sup>1,3</sup> and M. F. Gonzalez-Zalba<sup>4,†</sup>

<sup>1</sup>London Centre for Nanotechnology, University College London, London WC1H 0AH, United Kingdom

<sup>2</sup>CEA, LETI, Minatec Campus, F-38054 Grenoble, France

<sup>3</sup>Department of Electronic and Electrical Engineering, University College London,

London WC1E 7JE, United Kingdom

<sup>4</sup>Hitachi Cambridge Laboratory, J.J. Thomson Avenue, Cambridge CB3 0HE, United Kingdom

(Received 24 October 2017; revised manuscript received 25 January 2018; published 10 May 2018)

Quantum computers require interfaces with classical electronics for efficient qubit control, measurement, and fast data processing. Fabricating the qubit and the classical control layer using the same technology is appealing because it will facilitate the integration process, improving feedback speeds and offering potential solutions to wiring and layout challenges. Integrating classical and quantum devices monolithically, using complementary metal-oxide-semiconductor (CMOS) processes, enables the processor to profit from the most mature industrial technology for the fabrication of large-scale circuits. We demonstrate a CMOS single-electron memory cell composed of a single quantum dot and a transistor that locks charge on the quantum-dot gate. The single-electron memory cell is conditionally read out by gate-based dispersive sensing using a lumped-element *LC* resonator. The control field-effect transistor (FET) and quantum dot are fabricated on the same chip using fully depleted silicon-on-insulator technology. We obtain a charge sensitivity of  $\delta q = 95 \times 10^{-6} e \text{ Hz}^{-1/2}$  when the quantum-dot readout is enabled by the control FET, comparable to results without the control FET. Additionally, we observe a single-electron retention time on the order of a second when storing a single-electron charge on the quantum dot at millikelvin temperatures. These results demonstrate first steps towards time-based multiplexing of gate-based dispersive readout in CMOS quantum devices opening the path for the development of an all-silicon quantum-classical processor.

DOI: 10.1103/PhysRevApplied.9.054016

#### I. INTRODUCTION

Multiple quantum computing platforms have already reached the level of few-qubit demonstrators [1,2] and are addressing the challenges of scaling up to larger arrays in order to implement error-correction protocols [3–5] and tackle practical problems. Besides the challenge of scaling up quantum devices reliably, a key area is the development of the interface between isolated quantum devices and the classical control and readout technology (which may include optics, microwaves, or dc electronics, depending on the technology platform) to perform control and readout of the quantum state of the system [6]. This quantum-classical interface ranges from low-level operations for implementing feedback and error correction up to high-level operations to run the quantum algorithm.

Amongst the most promising candidates for large-scale quantum computing are electron spins in semiconductor devices, particularly in isotopically purified silicon [7–10]. Silicon is attractive as a host material, as it offers long coherence times [9,11,12] and a variety of qubit

implementations and coupling geometries [9-11,13-22]. Silicon-based qubit implementations have advanced to a level which could allow fabricating of complex quantum circuits. These advances are reflected by the amount of recent architectural proposals addressing the challenges towards a fault-tolerant, large-scale, spin-based quantum computer, which include the development of a quantum-classical interface [23-29]. Silicon-based approaches can all, to varying degrees, leverage nanofabrication techniques used in the semiconductor industry, and they can make use of CMOS technology as the basic platform for qubit devices [13,16]. The small footprint of the qubit nanostructures themselves would allow for high-density integration of the qubits [14]; however, exploiting this potential to scale up to a large number of densely packed qubits brings formidable challenges in qubit addressing.

CMOS technologies provide a natural route towards tackling challenges in qubit addressing and the integration of control and readout electronics for large-scale quantum processors [30]. A recent proposal by Veldhorst *et al.* considers on-chip integration of quantum and classical hardware, with a CMOS-based quantum processor relying on quantum-dot spin qubits and transistor-based control circuits combined with charge storage and a scalable

simon.schaal.15@ucl.ac.uk

<sup>&</sup>lt;sup>T</sup>mg507@cam.ac.uk

gate-based readout scheme [24]. The architecture has similarities with the floating memory gates found in modern dynamic random-access memory (DRAM) chips [31]. In both cases, a key concept which underpins scalability is multiplexing: the ability to address arrays of  $2^n$  (qu)bits using O(n) leads. If, ultimately,  $10^8$  qubits will be necessary to solve practical problems in a fault-tolerant quantum computation protocol [32], then multiplexing would alleviate the prohibitively large number of lines needed to address each qubit independently.

On-chip multiplexing circuitry to address elements of an array of gate-defined quantum devices has been demonstrated in GaAs [33,34] [256 quantum point contacts (QPCs)] and Si/SiGe [35] (four quantum-dot devices). Similarly, a switching matrix for a high-frequency transmission line has been realized [29] showing routes towards controlling large-scale devices. In addition to device control, high-fidelity readout is an essential requirement, and for quantum-dot devices readout is commonly achieved by using nearby electrometers [36–38]. Gate-based readout [39–41] provides a more scalable alternative, taking the gate(s) that define the quantum dot and using them additionally as a sensor. For both separate and gate-based qubit readout, sensitivity and speed are improved by using radio-frequency (rf) techniques: coupling the sensor to a rf lumped-element resonant circuit. Recently, gate-based approaches have reached a sensitivity of  $37 \times 10^{-6} e \text{ Hz}^{-1/2}$ [42], comparable to rf electrometers [37,43,44].

Frequency-domain multiplexing using multiple lumpedelement circuits is a useful method to read out multiple sensors simultaneously; however, the scalability of this approach is limited by the accessible bandwidth of such circuits [45]. Time-based multiplexing allows for the subsequent readout of multiple gate-based sensors limited by the retention (refresh) time of individual cells and requires only a single resonant circuit tackling challenges towards readout of dense quantum-dot arrays.

In the context of circuit quantum electrodynamics transmission-line resonators are used to achieve strong coupling between photons and a superconducting artificial atom [46]. Recently, these approaches have been adapted to silicon-based quantum-dot devices achieving strong coupling [15,47–49] and dispersive readout [50] (with an increased accessible bandwidth due to operation at a few gigahertz), representing an alternative to rf electrometers and gate-based readout using lumped-element circuits.

#### **II. EXPERIMENTAL SETUP**

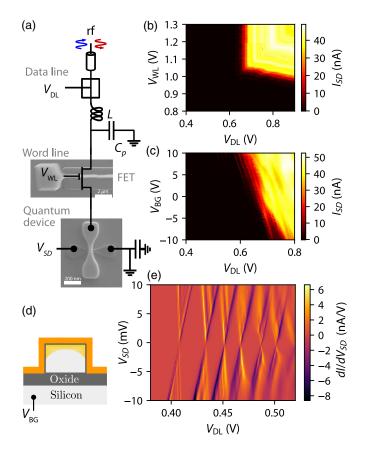

As envisioned by Veldhorst *et al.* [24], both the quantumdot device and the control field-effect transistor (FET) are fabricated using the same CMOS process and realized on the same chip (see Appendix A for details). The role of the FET is to retain a voltage at the quantum-dot gate in the *off* state (charge storage) in order to keep the number of electrons in the dot constant. Moreover it allows selective rf readout of the dot's charge state; i.e., gate sensing can be performed only when the FET is in the *on* state. The configuration presented here resembles that of a single DRAM cell in which the role of the charge-storage capacitor is now played by the quantum device, realized in a nanowire transistor (60-nm-wide channel, 30-nm gate), while the "access FET" in DRAM has the role realized by a micronwide channel transistor ("control FET") and the readout electronics is represented by the *LC* resonator. The measurement setup (see Appendix B for details) is depicted in Fig. 1(a), including SEM micrographs of both devices. The connection between the devices is made on chip using a short bond wire. Our experiment realizes a first step towards an integrated time-based multiplexing of gate-based reflectometry readout by demonstrating sensitive readout through the control FET in the *on* state combined

FIG. 1. Experimental setup and dc transport measurements: (a) Measurement circuit schematic, including SEM micrographs of the control FET and quantum device. Control and measurement signals are sent to the quantum device via the channel of a control FET. (b) Transport through the quantum device as a function of  $V_{DL}$  and  $V_{WL}$  yielding the threshold voltage of the control FET and quantum device at  $V_{BG} = 0$  V. (c) Turn-on characteristic of the quantum device as a function of  $V_{BG}$  when the FET is biased well above threshold at  $V_{WL} = 1.3$  V. (d) Cross-section illustration of the nanowire-based quantum device under high back-gate bias and near-threshold top-gate bias, such that a single quantum dot forms. (e) Coulomb diamonds indicating a single quantum dot in the quantum device at  $V_{BG} = 10$  V.

with floating-gate charge storage in the *off* state. Multiplexing can then be achieved by connecting additional cells consisting of a single switching FET and a quantum device (as the one demonstrated here) to the same highfrequency line sharing one single resonant and bias circuit.

In the nanowire transistor, we expect formation of quantum dots in the upper corners at cryogenic temperature due to an enhanced field effect under the gate [51]. At large positive back-gate voltage, the wave function of electrons in the corners is expected to extend farther into the center of the wire, resulting in a single extended quantum dot [see Fig. 1(d)] [52].

The combined quantum-classical CMOS circuit presented here has two primary inputs which, in analogy to a multiplexer or memory device, we refer to as the word and data (bit) line. The word line is connected to the gate of the control FET, while the data-line signal passes through the channel of the control FET and is applied to the gate of the quantum device. Source-drain transport through the quantum device can be measured directly and readout based on rf reflectometry can be performed (when the control FET gate voltage  $V_{\rm WL}$  is above threshold) by applying rf modulation via the data line [using an on-printed circuit board (PCB) bias tee] to an LC resonant circuit made from a surface mount inductor and the parasitic capacitance of the device  $C_p$ . The LC resonator response is amplified at multiple stages, followed by in-phase and quadrature demodulation (see Appendix B and Ref. [41] for details), from which the amplitude and phase of the reflected signal are obtained. The phase  $\Phi$  of the reflected signal is sensitive to small changes  $\Delta C$  in the capacitance of the quantum device, associated, for example, with the tunneling of single electrons:  $\Delta \Phi \approx$  $2Q\Delta C/C_T$  [53], with Q being the quality factor of the resonator and  $C_T$  being the total capacitance of the circuit, which includes the parasitic capacitance in parallel with the device capacitance.

#### **III. dc CHARACTERIZATION**

First, we characterize the quantum device and the control FET through transport measurements. We measure the source-drain current through the quantum device as a function of  $V_{DL}$  and  $V_{WL}$ , at a source-drain bias of  $V_{SD} = 1$  mV, observing the turn-on of the FET and quantum device in Fig. 1(b). When the control FET is operated below threshold (the off state), the gate of the quantum device is isolated from the signal on the data line. In this state of the circuit, the quantum device gate floats, allowing it to retain its charge over a timescale of a second, as we explore later on. For measurements where  $V_{WI}$  is ramped slowly [as in Fig. 1(b)], the quantum device gate voltage tends to 0 V when the control FET is off. Once the control FET is operated well above threshold, the transfer curve of the quantum device transistor can be measured, while a transition region is also apparent where the control FET is still strongly resistive. From Fig. 1(b), we estimate the threshold voltage of the quantum device  $V_{\rm th}^Q = 0.63$  V and the FET  $V_{\rm th}^{\rm FET} = 0.37$  V (at  $V_{\rm BG} = 0$  V). The control FET threshold voltage is calculated as  $V_{\rm th}^{\rm FET} = V_{\rm WL} - V_{\rm DL}$  at  $(V_{\rm WL}, V_{\rm DL}) = (1.02, 0.65)$  V and additionally depends on  $V_{\rm BG}$  (not shown).

An additional tuning parameter for the quantum device used here is the back-gate voltage  $V_{BG}$  applied to the substrate, which affects both the control FET and quantum device, as they are realized on the same chip.

In Fig. 1(c), we show the quantum-dot source-drain current as a function of  $V_{DL}$  and  $V_{BG}$  with the control FET biased at  $V_{WL} = 1.3$  V. While the quantum-dot device shows no transport at small  $V_{DL}$ , we see a turn-on at high  $V_{DL}$ . We observe that the turn-on threshold reduces as  $V_{BG}$ is increased. Close to threshold, we observe Coulomb oscillations which look very regular at large  $V_{BG}$ . Additionally, we note that the circuit *RC* time remains shorter than the acquisition time (20 ms) for all shown back-gate voltages.

Finally, in Fig. 1(e), we confirm the formation of a single few-electron quantum dot under the gate of the quantum device by measuring Coulomb diamonds at  $V_{BG} = 10$  V and  $V_{WL} = 1.3$  V. We observe a first addition energy of about 16 meV, showing strong confinement compatible with previous measurements [13,51].

#### **IV. rf CHARACTERIZATION**

We now move on to performing a gate-based rf readout of the quantum dot and evaluating the achievable charge sensitivity, considering the potential impact of the additional parasitic capacitance and dissipation from the control FET circuit.

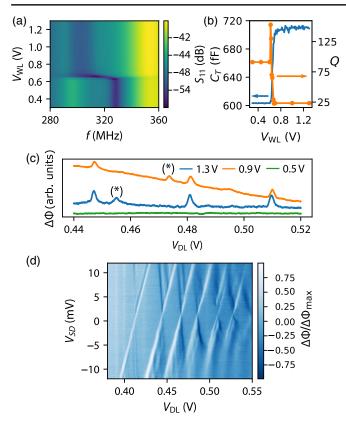

#### A. rf readout

First, we characterize the *LC* resonant circuit by measuring reflection ( $S_{11}$ ) as a function of  $V_{WL}$  [see Fig. 2(a)]. We observe a lowering of the resonance frequency when the control FET is operated above threshold ( $V_{WL} > 0.63$  V) due to the additional capacitance of the FET circuit that appears in parallel to  $C_p$ . Figure 2(b) shows the total capacitance  $C_T$  (assuming the nominal inductance L = 390 nH) and quality factor Q of the *LC* circuit obtained from Fig. 2(a). We estimate the contribution of the FET circuit at 105 fF. Additionally, we observe a reduction of Qwhen the FET is in the *on* state. The quality factor and capacitance play an important role in the phase response ( $\Delta \Phi \approx 2Q\Delta C/C_T$ ) [53] and sensitivity of gate-based dispersive readout, which is addressed later in this article.

Next, we examine the phase response of the resonant circuit as a function of the gate voltage on the control FET [see Fig. 2(c)], using rf modulation at frequency  $f_{\rm rf} =$  313 MHz and power  $P_{\rm rf} = -88$  dBm. Starting with the control FET well above threshold ( $V_{\rm WL} = 1.3$  V), in the strong accumulation regime, we observe three principal

FIG. 2. rf characterization and charge sensitivity: (a)  $S_{11}$  of the rf circuit as a function of  $V_{WL}$  (with  $V_{DL} = 0.4$  V and  $V_{BG} = 10$  V). (b) Total resonator capacitance  $C_T$  (with L = 390 nH) and quality factor Q as a function of  $V_{WL}$ . (c) Change in phase response for different  $V_{WL}$  values showing three Coulomb oscillations only when the control FET is operated above threshold. Features originating from charge transitions within the control FET itself are indicated (as asterisk). (d) Coulomb diamonds measured in the phase response ( $V_{BG} = 10$  V and  $V_{WL} = 1.3$  V), which is normalized with respect to the maximal change.

Coulomb peaks when ramping  $V_{DL}$  [the blue trace in Fig. 2(c)]. The peaks remain initially visible as  $V_{WI}$  is reduced, though a background signal begins to dominate as the control FET enters the weak-inversion regime, where the FET gate capacitance strongly depends on  $V_{\rm WL} - V_{\rm DL}$ . Since  $V_{DL}$  is modulated by the rf signal, this dependency is picked up in the dispersive response of the resonator as an additional change in capacitance and, in turn, produces an additional phase shift that depends on  $V_{DL}$ . Eventually, when  $V_{WL} < 0.5$  V, the control FET is below threshold and the dispersive response vanishes [the green trace in Fig. 2(c)]. We note the appearance of additional features in the scan (indicated by asterisks), which we identify with single-electron tunneling events in the control FET due to their  $V_{\rm WL}$  dependence. These features become more apparent when operating the control FET close to threshold. Figure 2(d) shows rf measurements (with the control FET well above threshold) demonstrating Coulomb diamonds of the quantum dot in the same voltage region as the transport measurements in Fig. 1(e). The correspondence between both sets of measurements shows that, in the strong accumulation regime, the FET channel has a negligible impact on the rf readout.

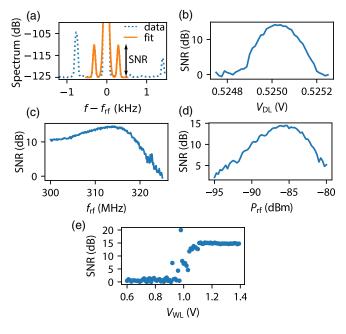

#### B. Charge sensitivity

To measure the charge sensitivity of the gate-based sensor with a control FET, we apply a small-amplitude signal of frequency  $f_s = 303$  Hz (in addition to the rf modulation at  $f_{\rm rf}$ ) onto the data line and monitor the signalto-noise ratio (SNR) in decibels of the sidebands appearing in the frequency spectrum at  $f_{\rm rf} \pm f_s$ . The peak amplitude of the signal (0.2 mV) corresponds to a change of  $\Delta q_{\rm rms} =$  $0.005\,78e$  in the charge on the quantum dot, where e is the charge of the electron. A typical spectrum in shown is Fig. 3(a). We optimize the sideband SNR by tuning the circuit parameters  $V_{\rm DL}$ ,  $f_{\rm rf}$ , and  $P_{\rm rf}$  as seen in Figs. 3(b)-3(d), respectively. First, we find the maximum sensitivity at the point of maximum slope in the response of the resonator,  $V_{\rm DL}=0.525$  V. The rf dependence, in Fig. 3(c), reveals a maximum at  $f_{\rm rf} = 313$  MHz and a 3-dB measurement bandwidth of 13 MHz, which translates into a loaded Q of 24 in the on state of the control FET, which is compatible with estimations obtained from Fig. 2(a). The optimal value for the rf power  $P_{\rm rf}$  is found

FIG. 3. Charge sensitivity of the gated rf readout: (a) Sidebands in the spectrum when operating at the point of maximum slope of a Coulomb oscillation with an equivalent excitation of 0.005 78*e* at 303 Hz superimposed on the data line. Signal-to-noise ratio (SNR) as a function of (b) data-line dc voltage  $V_{DL}$ , (c) carrier frequency  $f_{rf}$ , (d) carrier power  $P_{rf}$ , and (e) FET gate voltage  $V_{WL}$ . When not being swept, the following parameter values are used:  $V_{WL}=1.3$ V,  $V_{DL}=0.525$  V,  $f_{rf}=312$  MHz,  $P_{rf}=-85$  dBm.

to be -86 dBm. Finally, observing the SNR as a function of  $V_{\rm WL}$  [Fig. 3(e)], we identify two plateaus corresponding to the *on* and *off* states of the control FET. In the approximately linear transition between the plateaus, we observe multiple scattered data points, which we attribute to transitions in the weak-inversion regime of the FET [see the starred features in Fig. 2(c)]. Overall, using optimized circuit parameters, we obtain a SNR of 15.6 dB, which translates into a charge sensitivity of  $\delta q = \Delta q_{\rm rms} / (\sqrt{2B_{\rm SA}} \times 10^{\rm SNR/20}) = 95 \times 10^{-6} e \, {\rm Hz}^{-1/2}$  for the chosen spectrum analyzer bandwidth  $B_{\rm SA} = 50$  Hz. We study the impact of the control FET resistance ( $R_{\rm FET}$ ) on sensitivity in Appendix D.

In this experiment, the bandwidth of the charge sensitivity measurements is limited to 500 Hz due to low-pass filtering of the line used to deliver the sinusoidal signal  $f_s$ . However, the bandwidth of gate-based reflectometry is limited by the *LC* resonator bandwidth, which is about 10 MHz when the resonator is coupled to the quantum device.

The charge sensitivity obtained in this experiment is lower than typical rf-QPC devices [44] and demonstrates more than a factor of 50 improvement compared to GaAsbased gate sensors [39], and it is only a factor of 2.5 higher than previously reported in a similar device without a transistor circuit [42].

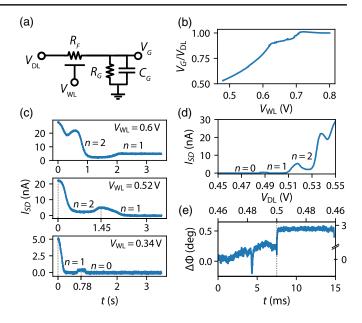

#### V. CHARGE STORAGE

For multiplexing of the quantum device gate signal to be effective, the gate must be able to store the charge for a time which is long compared to the inverse of the refresh rate. To measure the electron retention time in our circuit, we study the dynamics of the quantum device when switching the control FET on and off. Measurements are performed in a different pair of devices, with nominally identical dimensions to those used above. In Fig. 4(a), we present the equivalent circuit of the charge memory node, similar to a voltage divider for the data-line voltage  $V_{\rm DL}$  with the variable channel resistance of the FET,  $R_F$ , and gate leakage resistance,  $R_G$ , which represents dielectric losses through the gate oxide. Both resistances determine the voltage  $V_G = [R_G/(R_F + R_G)]V_{DL}$  appearing on the gate of the quantum device; the capacitance of this gate, represented by  $C_G$ , can be obtained from the gate-voltage spacing  $\Delta V_{DL}$  between consecutive Coulomb blockade oscillations plotted in Fig. 4(d). Using  $C_G^{n,n+1} =$  $e/\Delta V_{\rm DL}^{n,n+1}$ , where *n* is the number of electrons in the dot with respect to an unknown offset N, we obtain  $C_G^{0,1} =$ 6.2 aF and  $C_G^{1,2} = 7.0$  aF. In Fig. 4(b), we show the voltage division  $V_G/V_{DL}$  obtained by tracking the position of the Coulomb peak as a function of  $(V_{WL} - V_{DL})$ . We conclude that, at  $V_{WL} < 0.5$  V, the resistance of the control FET channel becomes greater than the gate leakage in the quantum device.

FIG. 4. Charge retention time and fast switching: (a) Equivalent circuit consisting of the variable control FET resistance  $R_F$  and quantum device gate leakage  $R_G$  and capacitance  $C_G$ . (b) Voltage divider characteristic of this circuit. (c) Demonstration of charge locking for different FET *off* states. Slow leakage of quantum-dot gate charge is observed. (d) Quantum device transfer characteristic. (e) Demonstration of rf sensing combined with fast switching of the control FET. Initially, the FET is biased above threshold and  $V_{\rm DL}$  is ramped from 0.46 to 0.50 V. Tunneling of the first electron onto the quantum dot is observed (left axis). After 7.5 ms, the FET is biased below threshold, leading to a large jump in phase due to the change in resonance frequency (right axis), while  $V_{\rm DL}$  is ramped back down. In the *off* state, no electron tunneling is observed.

The charging dynamics of the device is determined by the circuit RC time constant  $\tau = [(C_G R_G R_F)/$  $(R_G + R_F)$ ]. By switching the control FET from an on state to different off states and monitoring the resulting source-drain current through the quantum device, we study the dynamics of our circuit [see Fig. 4(c)]. In each case,  $V_{\rm DL}$  is kept constant at 0.6 V. By comparing the transient response with the quantum device transfer characteristic [Fig. 4(d)], we see that  $I_{SD}(t)$  reproduces the Coulomb oscillations, with the steady-state current determined by the voltage divider and  $V_{DL}$ . For  $V_{WL} = 0.6$  V as the off state,  $R_F < R_G$ , the discharging of the gate capacitor, occurs mainly through the control FET channel. For a more resistive off state of the control FET, as given by  $V_{\rm WI} =$ 0.34 V, discharging of the gate capacitor occurs mainly through gate leakage since  $R_F > R_G$  and the steady-state voltage on the quantum device gate  $V_G$  approaches zero.

Using the observed time dynamics of the current in Fig. 4(c), we characterize the single-electron retention time of the storage node through time lapses  $\Delta t^{n,n+1}$  between successive Coulomb oscillations, obtaining  $\Delta t^{1,2} = 1450$  ms and  $\Delta t^{0,1} = 780$  ms. These retention times can

be used to estimate the following circuit parameters:  $R_F(V_{WL} = 0.52 \text{ V}) = 3.1 \times 10^{18} \Omega$ ,  $R_F(V_{WL} = 0.34 \text{ V}) = 4.7 \times 10^{18} \Omega$ , and  $R_G = 3.5 \times 10^{18} \Omega$ . For the *RC* time constant, we find  $\tau^{1,2}$ ,  $\tau^{0,1} \approx 12$  s. These results provide valuable information to assess the suitability of time-multiplexing dispersive readout for large-scale quantum computing. First of all, these values compare quite favorably to state-of-the-art DRAM cells, which show a leakage resistance on the order of  $10^{15} \Omega$  [54] and a refresh time of 64 ms [55]. Moreover, the retention times reported here are well above the typical expected readout times of 100 ns of gate-based reflectometry [42] and the single-qubit coherence time of 28 ms in <sup>28</sup>Si substrates [9]. Considering typical operation times of spin qubits in silicon (1  $\mu$ s), this retention time will allow the addressing of  $10^6$  qubits before the voltage on one node needs to be refreshed.

As a demonstration towards time-multiplexed dispersive readout, we perform a rf reflectometry measurement followed by fast switching of the control FET [shown in Fig. 4(d)]. In the first part of the measurement cycle,  $V_{\rm DL}$ is ramped from 0.46 to 0.50 V while the control FET gate is on ( $V_{WL} = 1.2$  V), leading to a tunneling of the first electron onto the quantum dot. Then, after 7.5 ms, the control FET is switched to the off state ( $V_{WL} = 0.3$  V) and  $V_{DL}$  is ramped down to 0.46 V. As expected, no dispersive response from the quantum dot is measured during this time period, which can instead be used to measure another quantum device connected to the same data line via a different control FET. In this way, multiple qubits can be measured sequentially within the retention time of the charge-storage circuit. Considerations on the heat dissipation of this sequential approach are discussed in Appendix A.

#### **VI. CONCLUSION**

In conclusion, we demonstrate in this paper the integration of three elements likely to play key roles in a largescale spin-based quantum computer: a quantum device (quantum dot), a classical control device (field-effect transistor), and sensitive charge readout (electrical resonator). Two of these are fabricated on the same chip using CMOS technology, and there is the potential for the LCresonator to be made in a CMOS process [45,56]. High quality factors can be achieved by using superconducting TiN, which is already found in the gate stack of current CMOS transistors. Overall, we demonstrate a first step towards time-based multiplexing of gate-based radiofrequency reflectometry by demonstrating controlled rf readout of a single quantum dot with a charge sensitivity of  $\delta q = 95 \times 10^{-6} e \,\mathrm{Hz}^{-1/2}$ , combined with single-electron charge storage on the order of 1 s, providing motivation for further experiments on multiqubit circuits.

#### ACKNOWLEDGMENTS

We are grateful for the useful discussions with A. Rossi and N. J. Lambert. This research has received funding from the European Union's Horizon 2020 research and innovation program under Grant Agreement No. 688539 [57] and the Seventh Framework Programme (FP7/2007–2013) through Grant Agreement No. 318397 [58], as well as by the Engineering and Physical Sciences Research Council (EPSRC) through the Centre for Doctoral Training in Delivering Quantum Technologies (Grant No. EP/L015242/1) and UNDEDD (Grant No. EP/ K025945/1). M. F. G.-Z. acknowledges support from the Winton Programme for the Physics of Sustainability and Hughes Hall, University of Cambridge.

#### **APPENDIX A: FABRICATION DETAILS**

The CMOS transistors used in this work are fabricated on SOI substrates with a 145-nm buried oxide. The silicon layer is patterned to create the nanowires by means of optical lithography, followed by a resist trimming process. The gate stack consists of 1.9-nm HfSiON capped by 5 nm TiN and 50 nm polycrystalline silicon leading to a total equivalent oxide thickness of 1.3 nm. The Si thickness under the HfSiON/TiN gate is 11 nm. After gate etching, a SiN layer (10 nm) is deposited and etched to form a first spacer on the sidewalls of the gate. 18-nm-thick Si raised source and drain contacts are selectively grown before the source-drain extension implantation and activation annealing. A second spacer is formed followed by source-drain implantations, activation spike anneal, and salicidation [(Ni,Pt)Si].

#### **APPENDIX B: MEASUREMENT SETUP**

Measurements are performed at the base temperature of a dilution refrigerator (40 mK). Low-frequency signals ( $V_{SD}$ ,  $V_{\rm DL}$ ,  $V_{\rm WL}$ ) are delivered through filtered cryogenic loom, while a radio-frequency signal for gate-based readout is delivered through an attenuated and filtered coaxial line which connects to a on-PCB bias tee combining the rf modulation with  $V_{DL}$ . The resonator is formed from a 390-nH inductor and the sample's parasitic capacitance to ground in parallel with the device. The inductor consists of a surface mount wire-wound ceramic core (EPCOS B82498B series), and the PCB is made from 0.8-mm-thick Rogers RO4003C laminate with an immersion silver finish. The reflected rf signal is amplified at 4 K (QuinStar QCA-U350-30H) and room temperature, followed by guadrature demodulation (Polyphase Microwave AD0105B), from which the amplitude and phase of the reflected signal are obtained.

#### **APPENDIX C: HEAT DISSIPATION**

Although integration of quantum and classical CMOS devices promises major advantages in practical quantum computing architectures—for example, in addressing wiring challenges—this integration comes at a cost of managing the dissipation of heat from the classical control

circuits. We estimate the heat dissipation per device in our experiments, based on the dynamic power produced by the control FET, which is given by  $P = C_{\text{FET}} f_{\text{op}} \Delta V^2$ . We estimate  $C_{\text{FET}}$ , the FET capacitance, to be  $C_{\text{FET}} = 13$  fF, given the FET dimensions (50 nm  $\times$  10  $\mu$ m gate and 1.3 nm equivalent oxide thickness). The operation frequency  $f_{op}$  is limited by readout time, typically  $t = 1 \ \mu s$  for rf sensors, which determines the maximal frequency of 1 MHz. The largest voltage difference between the on and off states of the FET chosen in this experiment comes close to  $\Delta V = 1$  V. From this voltage change, we estimate a power dissipation of P = 13 nW per device, which can be treated as an upper bound as the dimensions, and thus the capacitance of the FET, the operation frequency, and the voltage difference  $\Delta V$  can all be reduced. Nevertheless, assuming a cooling power of 400  $\mu$ W at 100 mK, as is achieved in current dilution refrigerators, operation of at least 30 000 transistors would be possible at this temperature.

#### APPENDIX D: IMPACT OF CONTROL FET RESISTANCE

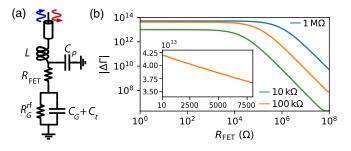

In this appendix, we calculate the impact of the control FET resistance on the gate-sensor sensitivity. We consider the circuit in Fig. 5(a). It schematically represents a singleelectron memory cell embedded in an *LC* resonator. Here, *L* represents a surface mount inductor, and  $C_p$  is the parasitic capacitance to ground of the cell.  $R_{\text{FET}}$  represents the source-drain resistance of the control FET. The parallel *RC* circuit after the FET represents the high-frequency equivalent circuit of the quantum-dot device, as seen from the gate electrode. The circuit consists of a constant geometric capacitor  $C_G$  combined with a variable capacitance  $C_t$  representing gate-voltage-dependent tunneling contributions and a resistor  $R_G^{\text{rf}}$  that parametrizes high-frequency dielectric losses. The reflection coefficient of this circuit is given by

FIG. 5. Impact of FET resistance on the sensitivity to device capacitance changes: (a) Equivalent circuit with the FET resistance  $R_{\text{FET}}$ , parasitic and FET capacitance  $C_p$ , and quantum device with losses  $R_G^{\text{rf}}$ , capacitance  $C_G$ , and variable tunneling capacitance  $C_I$ . (b) Reflection coefficient sensitivity to capacitance changes as a function of  $R_{\text{FET}}$  for different values of  $R_G^{\text{rf}}$  (logarithmic scale). (Inset) Linear scale of region of low resistance.

$$\Gamma = \frac{Z - Z_0}{Z + Z_0},\tag{D1}$$

where Z is the impedance of the circuit and  $Z_0$  the coaxialline impedance of 50  $\Omega$ .

Gate-based sensors are sensitive to capacitance changes associated with single-electron tunneling [59]. In our particular case, single-electron tunneling manifests as a variable capacitor  $C_t$ . We model the sensor's reflection sensitivity to changes in  $C_t$ ,

$$|\Delta\Gamma| = \left|\frac{\partial\Gamma}{\partial C_t}\Delta C\right|,\tag{D2}$$

and study the dependence on  $R_{\text{FET}}$  and  $R_G^{\text{rf}}$ . We see that  $|\Delta\Gamma|$  does not change drastically until the FET resistance becomes comparable to  $R_G^{\text{rf}}$  (note the logarithmic scale). At large  $R_{\text{FET}}$ ,  $|\Delta\Gamma|$  drops rapidly and the gate sensor becomes insensitive to changes in  $C_t$ . A small  $R_{\text{FET}}$  value is desired to maximize the sensitivity, as highlighted in the inset of Fig. 5(b), which shows a linear decrease of sensitivity of the reflection coefficient to capacitive changes (for  $R_G^{\text{rf}} = 100 \text{ k}\Omega$ ). The *on* state dc resistance of the control FET used in this experiment is on the order of 20 k\Omega.

- R. Barends *et al.*, Digitized adiabatic quantum computing with a superconducting circuit, Nature (London) **534**, 222 (2016).

- [2] Philipp Schindler, Daniel Nigg, Thomas Monz, Julio T. Barreiro, Esteban Martinez, Shannon X. Wang, Stephan Quint, Matthias F. Brandl, Volckmar Nebendahl, Christian F. Roos, Michael Chwalla, Markus Hennrich, and Rainer Blatt, A quantum information processor with trapped ions, New J. Phys. 15, 123012 (2013).

- [3] Julian Kelly *et al.*, State preservation by repetitive error detection in a superconducting quantum circuit, Nature (London) **519**, 66 (2015).

- [4] A. D. Córcoles, Easwar Magesan, Srikanth J. Srinivasan, Andrew W. Cross, M. Steffen, Jay M. Gambetta, and Jerry M. Chow, Demonstration of a quantum error detection code using a square lattice of four superconducting qubits, Nat. Commun. 6, 6979 (2015).

- [5] D. Ristè, S. Poletto, M.-Z. Huang, A. Bruno, V. Vesterinen, O.-P. Saira, and L. DiCarlo, Detecting bit-flip errors in a logical qubit using stabilizer measurements, Nat. Commun. 6, 6983 (2015).

- [6] David J. Reilly, Engineering the quantum-classical interface of solid-state qubits, npj Quantum Inf. 1, 15011 (2015).

- [7] Lars R. Schreiber and Hendrik Bluhm, Quantum computation: Silicon comes back, Nat. Nanotechnol. 9, 966 (2014).

- [8] M. Veldhorst, J. C. C. Hwang, C. H. Yang, A. W. Leenstra, B. de Ronde, J. P. Dehollain, J. T. Muhonen, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, An addressable quantum dot qubit with fault-tolerant control-fidelity, Nat. Nanotechnol. 9, 981 (2014).

- [9] M. Veldhorst, C. H. Yang, J. C. C. Hwang, W. Huang, J. P. Dehollain, J. T. Muhonen, S. Simmons, A. Laucht, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, A two qubit logic gate in silicon, Nature (London) 526, 410 (2015).

- [10] K. Eng, T. D. Ladd, A. Smith, M. G. Borselli, A. A. Kiselev, B. H. Fong, K. S. Holabird, T. M. Hazard, B. Huang, P. W. Deelman, I. Milosavljevic, A. E. Schmitz, R. S. Ross, M. F. Gyure, and A. T. Hunter, Isotopically enhanced triplequantum-dot qubit, Sci. Adv. 1, e1500214 (2015).

- [11] E. Kawakami, P. Scarlino, Daniel R. Ward, F. R. Braakman, D. E. Savage, M. G. Lagally, Mark Friesen, Susan N. Coppersmith, Mark A. Eriksson, and L. M. K. Vandersypen, Electrical control of a long-lived spin qubit in a Si/SiGe quantum dot, Nat. Nanotechnol. 9, 666 (2014).

- [12] Juha T. Muhonen, Juan P. Dehollain, Arne Laucht, Fay E. Hudson, Rachpon Kalra, Takeharu Sekiguchi, Kohei M. Itoh, David N. Jamieson, Jeffrey C. McCallum, Andrew S. Dzurak, and Andrea Morello, Storing quantum information for 30 seconds in a nanoelectronic device, Nat. Nanotechnol. 9, 986 (2014).

- [13] Matias Urdampilleta, Anasua Chatterjee, Cheuk Chi Lo, Takashi Kobayashi, John Mansir, Sylvain Barraud, Andreas C. Betz, Sven Rogge, M. Fernando Gonzalez-Zalba, and John J. L. Morton, Charge Dynamics and Spin Blockade in a Hybrid Double Quantum Dot in Silicon, Phys. Rev. X 5, 031024 (2015).

- [14] D. M. Zajac, T. M. Hazard, X. Mi, E. Nielsen, and J. R. Petta, Scalable Gate Architecture for a One-Dimensional Array of Semiconductor Spin Qubits, Phys. Rev. Applied 6, 054013 (2016).

- [15] X. Mi, J. V. Cady, D. M. Zajac, P. W. Deelman, and J. R. Petta, Strong coupling of a single electron in silicon to a microwave photon, Science **355**, 156 (2017).

- [16] R. Maurand, X. Jehl, D. Kotekar-Patil, A. Corna, H. Bohuslavskyi, R. Laviéville, L. Hutin, S. Barraud, M. Vinet, M. Sanquer, and S. De Franceschi, A CMOS silicon spin qubit, Nat. Commun. 7, 13575 (2016).

- [17] Bent Weber, Y. H. Matthias Tan, Suddhasatta Mahapatra, Thomas F. Watson, Hoon Ryu, Rajib Rahman, Lloyd C. L. Hollenberg, Gerhard Klimeck, and Michelle Y. Simmons, Spin blockade and exchange in Coulomb-confined silicon double quantum dots, Nat. Nanotechnol. 9, 430 (2014).

- [18] M. G. House, T. Kobayashi, B. Weber, S. J. Hile, T. F. Watson, J. van der Heijden, S. Rogge, and M. Y. Simmons, Radio frequency measurements of tunnel couplings and singlet-triplet spin states in Si:P quantum dots, Nat. Commun. 6, 8848 (2015).

- [19] Zhan Shi, C. B. Simmons, J. R. Prance, John King Gamble, Teck Seng Koh, Yun-Pil Shim, Xuedong Hu, D. E. Savage, M. G. Lagally, M. A. Eriksson, Mark Friesen, and S. N. Coppersmith, Fast Hybrid Silicon Double-Quantum-Dot Qubit, Phys. Rev. Lett. **108**, 140503 (2012).

- [20] Patrick Harvey-Collard, Ryan M. Jock, N. Tobias Jacobson, Andrew D. Baczewski, Andrew M. Mounce, Matthew J. Curry, Daniel R. Ward, John M. Anderson, Ronald P. Manginell, Joel R. Wendt, Martin Rudolph, Tammy Pluym, Michael P. Lilly, Michel Pioro-Ladriere, and Malcolm S. Carroll, in *Proceedings of the 2017 IEEE International*

*Electron Devices Meeting (IEDM), San Francisco, 2017* (IEEE, New York, 2017), p. 36.5.1.

- [21] T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, Mark Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, A programmable two-qubit quantum processor in silicon, Nature (London) 555, 633 (2018).

- [22] D. M. Zajac, A. J. Sigillito, M. Russ, F. Borjans, J. M. Taylor, G. Burkard, and J. R. Petta, Resonantly driven CNOT gate for electron spins, Science **5965**, eaao5965 (2017).

- [23] L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, and M. Veldhorst, Interfacing spin qubits in quantum dots and donorshot, dense, and coherent, npj Quantum Inf. 3, 34 (2017).

- [24] M. Veldhorst, H. G. J. Eenink, C. H. Yang, and A. S. Dzurak, Silicon CMOS architecture for a spin-based quantum computer, Nat. Commun. 8, 1766 (2017).

- [25] Charles D. Hill, Eldad Peretz, Samuel J. Hile, Matthew G. House, Martin Fuechsle, Sven Rogge, Michelle Y. Simmons, and Lloyd C. L. Hollenberg, A surface code quantum computer in silicon, Sci. Adv. 1, e1500707 (2015).

- [26] Joe O'Gorman, Naomi H. Nickerson, Philipp Ross, John J. L. Morton, and Simon C. Benjamin, A silicon-based surface code quantum computer, npj Quantum Inf. 2, 15019 (2016).

- [27] Guilherme Tosi, Fahd A. Mohiyaddin, Vivien Schmitt, Stefanie Tenberg, Rajib Rahman, Gerhard Klimeck, and Andrea Morello, Silicon quantum processor with robust long-distance qubit couplings, Nat. Commun. 8, 450 (2017).

- [28] G. Pica, B. W. Lovett, R. N. Bhatt, T. Schenkel, and S. A. Lyon, Surface code architecture for donors and dots in silicon with imprecise and nonuniform qubit couplings, Phys. Rev. B 93, 035306 (2016).

- [29] J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and D. J. Reilly, Cryogenic Control Architecture for Large-Scale Quantum Computing, Phys. Rev. Applied 3, 024010 (2015).

- [30] P. Clapera, X. Jehl, A. Corna, S. J. Ray, M. Sanquer, A. Valentian, and S. Barraud, Design and cryogenic operation of a hybrid quantum-CMOS circuit, arXiv:1503.03993.

- [31] Brent Keeth, R. Jacob Baker, Brian Johnson, and Feng Lin, DRAM Circuit Design: Fundamental and High-Speed Topics (John Wiley & Sons, New York, 2007), p. 440.

- [32] Austin G. Fowler, Matteo Mariantoni, John M. Martinis, and Andrew N. Cleland, Surface codes: Towards practical large-scale quantum computation, Phys. Rev. A 86, 032324 (2012).

- [33] H. Al-Taie, L. W. Smith, B. Xu, P. See, J. P. Griffiths, H. E. Beere, G. A. C. Jones, D. A. Ritchie, M. J. Kelly, and C. G. Smith, Cryogenic on-chip multiplexer for the study of quantum transport in 256 split-gate devices, Appl. Phys. Lett. **102**, 243102 (2013).

- [34] R. K. Puddy, L. W. Smith, H. Al-Taie, C. H. Chong, I. Farrer, J. P. Griffiths, D. A. Ritchie, M. J. Kelly, M. Pepper, and C. G. Smith, Multiplexed charge-locking device for large arrays of quantum devices, Appl. Phys. Lett. 107, 143501 (2015).

- [35] D. R. Ward, D. E. Savage, M. G. Lagally, S. N. Coppersmith, and M. A. Eriksson, Integration of on-chip

field-effect transistor switches with dopantless Si/SiGe quantum dots for high-throughput testing, Appl. Phys. Lett. **102**, 213107 (2013).

- [36] J. M. Elzerman, R. Hanson, L. H. Willems van Beveren, B. Witkamp, L. M. K. Vandersypen, and L. P. Kouwenhoven, Single-shot read-out of an individual electron spin in a quantum dot, Nature (London) 430, 431 (2004).

- [37] D. J. Reilly, C. M. Marcus, M. P. Hanson, and A. C. Gossard, Fast single-charge sensing with a rf quantum point contact, Appl. Phys. Lett. 91, 162101 (2007).

- [38] C. Barthel, M. Kjærgaard, J. Medford, M. Stopa, C. M. Marcus, M. P. Hanson, and A. C. Gossard, Fast sensing of double-dot charge arrangement and spin state with a radiofrequency sensor quantum dot, Phys. Rev. B 81, 161308(R) (2010).

- [39] J. I. Colless, A. C. Mahoney, J. M. Hornibrook, A. C. Doherty, H. Lu, A. C. Gossard, and D. J. Reilly, Dispersive Readout of a Few-Electron Double Quantum Dot with Fast rf Gate Sensors, Phys. Rev. Lett. **110**, 046805 (2013).

- [40] A. C. Betz, R. Wacquez, M. Vinet, X. Jehl, A. L. Saraiva, M. Sanquer, A. J. Ferguson, and M. F. Gonzalez-Zalba, Dispersively detected Pauli spin-blockade in a silicon nanowire field-effect transistor, Nano Lett. 15, 4622 (2015).

- [41] M. Fernando Gonzalez-Zalba, Sergey N. Shevchenko, Sylvain Barraud, J. Robert Johansson, Andrew J. Ferguson, Franco Nori, and Andreas C. Betz, Gate-sensing coherent charge oscillations in a silicon field-effect transistor, Nano Lett. 16, 1614 (2016).

- [42] M. F. Gonzalez-Zalba, S. Barraud, A. J. Ferguson, and A. C. Betz, Probing the limits of gate-based charge sensing, Nat. Commun. 6, 6084 (2015).

- [43] A. Aassime, G. Johansson, G. Wendin, R. J. Schoelkopf, and P. Delsing, Radio-Frequency Single-Electron Transistor as Readout Device for Qubits: Charge Sensitivity and Backaction, Phys. Rev. Lett. 86, 3376 (2001).

- [44] J. D. Mason, L. Gaudreau, S. A. Studenikin, A. Kam, B. Djurkovic, A. S. Sachrajda, and J. B. Kycia, A high speed radio-frequency quantum point contact charge detector for time resolved readout applications of spin qubits, Physica (Amsterdam) 42E, 813 (2010).

- [45] J. M. Hornibrook, J. I. Colless, A. C. Mahoney, X. G. Croot, S. Blanvillain, H. Lu, A. C. Gossard, and D. J. Reilly, Frequency multiplexing for readout of spin qubits, Appl. Phys. Lett. **104**, 103108 (2014).

- [46] A. Wallraff, D. I. Schuster, A. Blais, L. Frunzio, J. Majer, M. H. Devoret, S. M. Girvin, and R. J. Schoelkopf, Approaching Unit Visibility for Control of a Superconducting Qubit with Dispersive Readout, Phys. Rev. Lett. 95, 060501 (2005).

- [47] X. Mi, M. Benito, S. Putz, D. M. Zajac, J. M. Taylor, Guido Burkard, and J. R. Petta, A coherent spinphoton interface in silicon, Nature (London) 555, 599 (2018).

- [48] A. Stockklauser, P. Scarlino, J. V. Koski, S. Gasparinetti, C. K. Andersen, C. Reichl, W. Wegscheider, T. Ihn, K. Ensslin, and A. Wallraff, Strong Coupling Cavity QED with Gate-Defined Double Quantum Dots Enabled by a High Impedance Resonator, Phys. Rev. X 7, 011030 (2017).

- [49] N. Samkharadze, G. Zheng, N. Kalhor, D. Brousse, A. Sammak, U. C. Mendes, A. Blais, G. Scappucci, and L. M. K. Vandersypen, Strong spin-photon coupling in silicon, Science 359, 1123 (2018).

- [50] P. Scarlino, D. J. van Woerkom, A. Stockklauser, J. V. Koski, M. C. Collodo, S. Gasparinetti, C. Reichl, W. Wegscheider, T. Ihn, K. Ensslin, and A. Wallraff, Allmicrowave control and dispersive readout of gate-defined quantum dot qubits in circuit quantum electrodynamics, arXiv:1711.01906.

- [51] Benoit Voisin, Viet Hung Nguyen, Julien Renard, Xavier Jehl, Sylvain Barraud, François Triozon, Maud Vinet, Ivan Duchemin, Yann Michel Niquet, Silvano De Franceschi, and Marc Sanquer, Few-electron edge-state quantum dots in a silicon nanowire field-effect transistor, Nano Lett. 14, 2094 (2014).

- [52] A. C. Betz, S. Barraud, Q. Wilmart, B. Plaçais, X. Jehl, M. Sanquer, and M. F. Gonzalez-Zalba, High-frequency characterization of thermionic charge transport in silicon-oninsulator nanowire transistors, Appl. Phys. Lett. 104, 043106 (2014).

- [53] S. J. Chorley, J. Wabnig, Z. V. Penfold-Fitch, K. D. Petersson, J. Frake, C. G. Smith, and M. R. Buitelaar, Measuring the Complex Admittance of a Carbon Nanotube Double Quantum Dot, Phys. Rev. Lett. **108**, 036802 (2012).

- [54] David Tawei Wang, Modern DRAM memory systems: Performance analysis and a high performance, powerconstrained dram scheduling algorithm, Ph.D. thesis, University of Maryland, College Park, 2005.

- [55] JEDEC Solid State Technology Association, Report No. JESD79-2B, 2005.

- [56] J. Burghartz, D. Edelstein, M. Soytter, H. Ainspan, and K. Jenkins, in *Proceedings of the 1998 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, USA, 1998*, Digest of Technical Papers, 1st ed. (Cat. No. 98CH36156), Vol. 33 (IEEE, New York, 1998), p. 246.

- [57] See http://mos-quito.eu.

- [58] See http://www.tolop.eu.

- [59] R. C. Ashoori, H. L. Stormer, J. S. Weiner, L. N. Pfeiffer, K. W. Baldwin, and K. W. West, *N*-Electron Ground State Energies of a Quantum Dot in Magnetic Field, Phys. Rev. Lett. **71**, 613 (1993).