## Growth kinetics of Si on fullsheet, patterned and silicon-on-insulator substrates

J.M. Hartmann, A. Abbadie, M. Vinet, L. Clavelier, P. Holliger, D. Lafond,

M. N Séméria, P. Gentile

### ► To cite this version:

J.M. Hartmann, A. Abbadie, M. Vinet, L. Clavelier, P. Holliger, et al.. Growth kinetics of Si on fullsheet, patterned and silicon-on-insulator substrates. Journal of Crystal Growth, 2003, 257, pp.19-30. 10.1016/s0022-0248(03)01380-0. cea-01989757

## HAL Id: cea-01989757 https://cea.hal.science/cea-01989757v1

Submitted on 22 Jan 2019  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Available online at www.sciencedirect.com

Journal of Crystal Growth 257 (2003) 19-30

www.elsevier.com/locate/jcrysgro

# Growth kinetics of Si on fullsheet, patterned and silicon-on-insulator substrates

## J.M. Hartmann<sup>a,\*</sup>, A. Abbadie<sup>a</sup>, M. Vinet<sup>a</sup>, L. Clavelier<sup>a</sup>, P. Holliger<sup>a</sup>, D. Lafond<sup>a</sup>, M.N. Séméria<sup>a</sup>, P. Gentile<sup>b</sup>

<sup>a</sup> CEA-DRT, LETI/DTS, CEA/GRE-17, Avenue des Martyrs, F-38054 Grenoble Cedex 9, France <sup>b</sup>DRFMC, CEA/GRE-17, Avenue des Martyrs, F-38054 Grenoble Cedex 9, France

> Received 10 April 2003; accepted 13 May 2003 Communicated by R. Kern

#### Abstract

Using a reduced pressure-chemical vapor deposition cluster tool, we have studied the epitaxial growth of Si using either a silane or a dichlorosilane + hydrochloric acid chemistry on fullsheet, patterned and silicon-on-insulator (SOI) substrates. We have first of all developed a ("HF-last" advanced wet cleaning + low thermal budget (775°C, 2 min) in situ H<sub>2</sub> bake) combination that yields atomically smooth, contamination free Si starting surfaces for both fullsheet and patterned wafers. We have then modeled the low temperature Si growth rate (silane or dichlorosilane + hydrochloric acid chemistry) on fullsheet wafers. A similar growth rate activation energy is found for both chemistries, i.e.  $E_{GR} \sim 50 \text{ kcal mol}^{-1}$ . The growth rate dependency on the Si precursor flow is vastly different, however. Fitting this dependency with a simple power law, a value of 0.36 is indeed associated to dichlorosilane, versus 0.92 for silane. The HCl etching rate is characterized by an activation energy  $E_{ER} \sim 34 \text{ kcal mol}^{-1}$ , with a 0.52 power law dependency on the HCl flow. On patterned wafers, we have demonstrated that a deposited Si thickness limit (20 nm) exists at 775°C for high  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  mass flow ratios. This limit disappears when (i)  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  is reduced (ii) the growth temperature is increased to 800°C. Finally, we have highlighted the specifics of the growth on SOI wafers. A significant growth rate reduction (compared to bulk Si) has been evidenced on ultra-thin Si over-layer SOI wafers. It gets less and less pronounced as the buried oxide layer gets thinner and/or the Si over-layer thickness increases. © 2003 Elsevier B.V. All rights reserved.

PACS: 81.15.Gh; 81.15.Aa; 68.55.-a

Keywords: A1. Fullsheet; A1. Patterned and SOI wafers; A1. Si growth kinetics; A1. Surface preparation; A3. Reduced pressurechemical vapor deposition

#### 1. Introduction

In the last few years, there has been significant interest in SiGe epitaxial growth on silicon

\*Corresponding author.

substrates, because Si/SiGe heterostructures allow band gap engineering to be used in conjunction with silicon technology [1] in field effect transistors [2,3], photodetectors [4], etc.

We propose in this paper a study of the growth kinetics of Si in reduced pressure-chemical vapor deposition (RP-CVD) on fullsheet, patterned and

E-mail address: jmhartmann@cea.fr (J.M. Hartmann).

<sup>0022-0248/03/\$ -</sup> see front matter  $\odot$  2003 Elsevier B.V. All rights reserved. doi:10.1016/S0022-0248(03)01380-0

silicon-on-insulator (SOI) substrates. Two precursor chemistries were used: either silane [5] or dichlorosilane + hydrochloric acid [6]. It is possible using the latest chemistry (i.e. the chlorinated one) to selectively grow high quality Si [7–10] layers inside the Si windows of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>-masked Si wafers, making it useful for the formation of Si raised sources and drains [11,12]. The knowledge of the specifics of the growth of Si on SOI wafers will be put to good use for the deposition of tensile-strained Si layers on top of nearly fully relaxed SiGe-on-insulator (SGOI) substrates [13–15].

As far as the experimental results are concerned, the article is organized as follows. We will first focus on the surface preparation (ex situ wet cleaning followed by an in situ low temperature H<sub>2</sub> bake) of fullsheet and patterned wafers prior to epitaxy. We will then present a semi-empirical modeling of the low temperature Si growth rate on fullsheet wafers for the hydrogenated and the chlorinated chemistries. We will highlight the specifics of the selective epitaxial growth of Si with the dichlorosilane+hydrochloric acid chemistry on patterned wafers. We will notably focus on the role of the growth temperature and of the  $F(HCl)/F(SiH_2Cl_2)$  mass flow ratio on the Si thickness that can be deposited inside the Si windows. Finally, we will quantify on SOI wafers the impact of both the buried oxide and Si overlayer thickness on the Si growth kinetics.

#### 2. Experimental details

We have grown the Si layers with an Epi Centura RP-CVD industrial cluster tool (manufactured by Applied Materials). The Si(001) substrates used are nominal ( $\pm 0.25^{\circ}$ ) and slightly p-type doped (resistance in the 7–10 $\Omega$ cm range). During the growth, the wafer lies horizontally on top of a circular SiC-coated susceptor plate that rotates to improve thickness uniformity. The substrate is heated by two banks of 20 tungsten-halogen lamps (maximum power: 2kW each) located above and below the susceptor assembly. It is therefore heated by thermal radiation coming from the upper lamps bank, as well as by thermal

conduction from the susceptor underneath. Temperature monitoring and control is ensured through the lower pyrometer, i.e. the one which is looking at the backside of the susceptor plate on which the wafer lies. The reading is therefore independent of the nature of the substrate (fullsheet, patterned or SOI). It is only the heat transfer by radiation from the upper lamp-bank that can be affected by changes in wafer surface emissivity during Si deposition [16]. In our study, the growth pressure was always 20 Torr. The flow of H<sub>2</sub> carrier gas was set at a fixed value of a few tens of standard liters per minute (slms), which was not altered throughout all the experiments. Pure dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub> or DCS) and pure silane  $(SiH_4)$  were used as the sources of Si.

A Akrion Gama One automated wet bench was used for the ex situ cleaning of our substrates. The secondary ion mass spectrometry (SIMS) measurements were carried out on a Cameca IMS 5f spectrometer. Cs<sup>+</sup> primary ions were used for carbon, oxygen, fluorine and germanium depth profiling, with an impact energy of 2 keV. The atomic masses monitored were those of  $Cs_2C^+$  $(133 \times 2 + 12 = 278 \text{ amu}), \text{ Cs}_2\text{O}^+$   $(133 \times 2 + 16 =$ 282 amu),  $Cs_2F^+$  (133 × 2+19=285 amu) and  $Cs_2Si^+$  (133 × 2 + 28 = 294 amu) [17]. Cross-sectional transmission electron microscopy imaging was performed on an Akashi EM-002B (fitted with an ultra-high resolution pole piece) that was operated at 200 kV. A Digital Instrument 3100 SPM platform fitted with a camera was used for the tapping-mode atomic force microscopy (AFM) imaging of the surface morphology. Scanning tunneling microscopy (STM) was carried out in ultra-high vacuum using an Omicron apparatus. Finally, spectroscopic ellipsometry (SE) measurements were carried on a SE 1280 Ellipsometer from KLA-Tencor.

The Si thickness deposited was determined in three different ways depending on the nature of the substrate:

• On bulk, fullsheet wafers, the 200 mm wafer was scaled on a micro-balance prior and just after the epitaxy step. The average thickness deposited on a 200 mm wafer is then given by:  $t(cm) = \Delta m/(\pi R^2 \rho) (\Delta m \text{ is the weight difference})$  (g), R (=10 cm) is the radius of the wafer and  $\rho = 2.328 \text{ g/cm}^3$  is the Si density).

- On bulk, patterned wafers, the Si thickness deposited was determined through a step height difference measurement in AFM at the boundary between a Si window and the dielectric masking material [18].

- On SOI wafers, the Si thickness deposited is determined through a differential measurement in SE of the Si over-layer thickness before and after the epitaxy step.

#### 3. Surface preparation

It is of the utmost importance when growing layers epitaxially on fullsheet, patterned or SOI wafers to start from a mono-crystalline Si surface free of any particles or contaminants.

We have used a variant, which we have named "EpiClean" [18], of the so-called "Low Consumption Front End of Line" (LC-FEOL) wet cleaning [19] to prepare the surface of our samples. This cleaning, whose last three steps are a 2.5 min dip into a HF:HCl:De-ionised water (DIW) bath  $(0.2/1/100 \text{ at } 23^{\circ}\text{C})$  followed by a DIW rinse and an Iso-Propylic Alcohol vapor drying [18], generate "HF-last", Si(001) passivated surfaces [20], i.e. surfaces with dangling bonds being mostly occupied by H or F atoms that are stable for a few tens of minutes in ambient conditions, enabling sample transfer and loading. An H<sub>2</sub>-bake, typically between 800°C and 900°C for a few tens of seconds up to a few minutes [11,21–26], will lead to the removal of any C, O or F residual atoms and to the formation of smooth [24,27]  $(2 \times 1)$ :H reconstructed surfaces that are much more stable in the air [28] (up to 40 h [29]).

Several groups have tried to minimize the thermal budget necessary for the  $H_2$  bake [21,25,26,30]. What has been found on fullsheet wafers is that an optimized wet clean [last step: 1:1000 HF(49%):deionized water] followed by an  $H_2$  bake at 800°C for 2 min is sufficient at 10 Torrs to produce oxygen and carbon-free Si surfaces [26]. We have tried to extend those findings for patterned wafers.

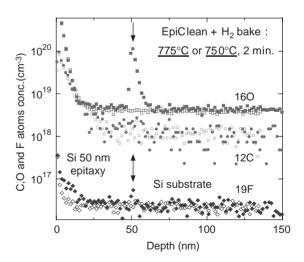

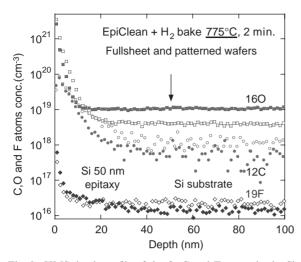

We have therefore cleaned fullsheet and patterned wafers with the above-mentioned "Epi-Clean" wet cleaning, loaded those samples inside the load-locks of our cluster tool, then purged those load-locks with N<sub>2</sub>. The samples have then been transferred over to the RP-CVD chamber, where they have been submitted at 20 Torrs to an  $2 \min H_2$  bake at either 775°C or 750°C, followed by the deposition of 60 nm of Si at 750°C using SiH<sub>2</sub>Cl<sub>2</sub>. We have profiled in SIMS (see Figs. 1 and 2) the C, O and F atoms in those samples. No peak has been observed for those elements at the Si epilayer/substrate interface at 775°C, this whatever the nature of the substrates (fullsheet or patterned). Meanwhile, 750°C seems to be too small a temperature (at least for  $2 \min H_2$ bakes) to get rid of those impurities, as attested by the peaks in SIMS at the interface between the Si epilayer and the substrate on a fullsheet wafer (see Fig. 1). For the sake of completeness, it should nevertheless be mentioned that no such peaks were observed for this bake temperature of 750°C on the corresponding patterned wafer. The temperature boundary between cleaned and contaminated wafers must therefore be slightly above 750°C.

Fig. 1. SIMS depth profile of the O, C and F atoms in the Si epilayers grown on fullsheet wafers after a ex situ "EpiClean" wet cleaning followed by an in situ H<sub>2</sub> bake either at either 775°C (open symbols) or at 750°C (full symbols) for 2 min (P = 20 Torrs).

Fig. 2. SIMS depth profile of the O, C and F atoms in the Si epilayers grown on either a fullsheet wafer (open symbols) or a patterned wafer (full symbols) after a {ex situ "EpiClean" wet cleaning +  $H_2$  bake at 775°C, 20 Torrs for 2 min} surface preparation. SIMS profiling was carried out inside a large Si window for the patterned wafer.

This conclusion is supported by the finding of Brabant et al. [30], who have found that neither a 10 min nor a 20 min bake under H<sub>2</sub> at 750°C does enable to completely get rid of the interfacial oxyde. They have indeed obtained in SIMS a small O peak at the interface (maximum:  $\sim 10^{19} (\sim 10^{18})$  cm<sup>-3</sup>, integrated dose:  $2.5 \times 10^{12} (2.34 \times 10^{11})$  cm<sup>-2</sup> for a 10 min (20 min) H<sub>2</sub> bake at 750°C). No C peak was obtained in both cases, however.

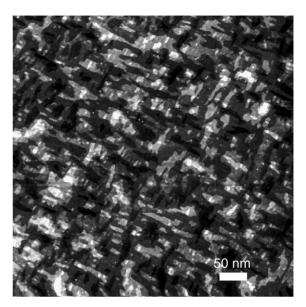

A STM image of the surface of a fullsheet wafer that has been cleaned ex situ using the "EpiClean" process followed by an in situ H<sub>2</sub> bake at 775°C for 2 min is plotted in Fig. 3. The surface is atomically smooth, with mono-atomic steps either straight ( $S_A$ -type) or meandering ( $S_B$ -type) [31,32] delimiting either (1 × 2) or (2 × 1)-reconstructed, a few tens of nm wide, terraces. The root mean square roughness of that surface is equal to 0.9 Å.

We can therefore conclude that an "EpiClean" ex situ wet clean followed by an in situ  $H_2$  bake at 775°C, 20 Torrs for 2 min is an efficient, low-thermal budget combination to obtain atomically smooth surfaces free of any residual contamination.

Fig. 3. STM image  $(500 \text{ nm} \times 500 \text{ nm})$  of the surface of a blanket Si(001) substrate that has been cleaned ex situ with an "EpiClean" recipe followed by an in situ H<sub>2</sub> bake at 775°C for 2 min. Sample bias voltage: +2.8 V, tunneling current: 80 pA.

#### 4. Si growth kinetics on fullsheet wafers

## 4.1. The dichlorosilane+hydrochloric acid chemistry

Simply speaking, the growth of Si using a  $SiH_2Cl_2 + HCl$  chemistry is expected to take place according to the following three equations [9,33]:

• SiH<sub>2</sub>Cl<sub>2</sub> thermally dissociates in the gas phase into SiCl<sub>2</sub> and H<sub>2</sub>:

$$SiH_2Cl_2(g) \rightleftharpoons SiCl_2(g) + H_2(g)$$

(1)

• Deposition of Si occurs through the reduction of the adsorbed SiCl<sub>2</sub> on a free surface site by hydrogen:

$$SiCl_2^* + H_2(g) \rightarrow Si(s) + 2HCl(g)$$

<sup>(2)</sup>

• If enough additional external HCl is added to the system at a given pressure and temperature, silicon etching occurs through:

$$\mathrm{Si}^{*} + 2\mathrm{HCl}(g) \rightarrow \mathrm{Si}\mathrm{Cl}_{2}^{*} + \mathrm{H}_{2}(g) \tag{3}$$

If the quantity of HCl added to the system is optimized, silicon atoms are removed on a patterned wafer from the dielectric mask before they form stable polysilicon nuclei. The SEG of Si can therefore be visualized as a sum of the growth effect, which is dependent of the abundance of adsorbed SiCl<sub>2</sub>, and the etching effect, which is dependent upon the partial pressure of HCl.

The low-temperature  $(750^{\circ}C \le T \le 850^{\circ}C)$  Si growth rate modelling we have adopted here is based on the work of Kongetira et al. [33]. They have fitted their Si growth rate dependence on the SiH<sub>2</sub>Cl<sub>2</sub> and HCl partial pressures, on the growth temperature and pressure with the following semiempirical expression:

GR (

$$\mu$$

m/min)

$$=\frac{k_{\rm GR}(\rm DCS)e^{-E_{\rm GR}(\rm DCS)/k_{\rm B}T}(P_{\rm DCS})^{z}(P_{\rm H_{2}})^{x}}{\Delta}$$

$$-\frac{k_{\rm ET}e^{-E_{\rm ET}/k_{\rm B}T}(P_{\rm HCl})^{y}}{\Delta}$$

where  $E_{GR}$  (DCS) and  $E_{ET}$  are activation energies for the growth and for the etching of Si, respectively.  $k_{GR}$  (DCS) and  $k_{ET}$  are rate constants for the growth and for the etching of Si, respectively.  $\Delta$  is a pressure-related factor. Having been fixed arbitrarily by Kongetira et al. to 1 for a growth pressure of 40 Torrs, it has been found to vary linearly with the growth pressure (in Torrs) in the following manner:  $\Delta = 0.06P - 1.4$ .  $P_{DCS}$ ,  $P_{H_2}$ and  $P_{HCl}$  are the incoming flows' partial pressures (in Torrs).  $k_B$  and T are the Boltzmann constant and the absolute growth temperatures, respectively. x has been fixed to 1.0 in Kongetira et al.'s work.

We have consequently made the following assumptions for the modeling of our experimental data:  $\Delta$  is arbitrarily fixed to 1.0 at 20 Torrs (instead of 40 Torrs), x is equal to 1.0. Let us now focus on the determination of  $E_{\text{GR}}$ ,  $k_{\text{GR}}$  and z. Without any incoming flow of HCl, the Si growth rate is given by:

GR<sub>without added HCl</sub>(nm/min)

$$= k_{\rm GR}(\rm DCS)e^{-E_{\rm GR}(\rm DCS)/k_BT}(P_{\rm DCS})^{z}(P_{\rm H_2}).$$

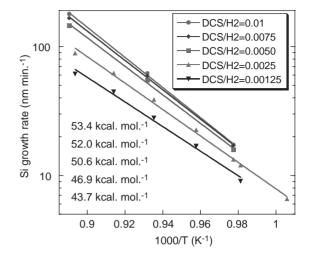

Using an Arrhenius plot of the Si growth rate without HCl as a function of the reverse absolute temperature (see Fig. 4), it is quite easy to determine  $E_{\text{GR}}$  (DCS).  $E_{\text{GR}}$  (DCS) has been found

Fig. 4. Arrhenius plot of the Si growth rate as a function of the reverse absolute temperature for several  $F(SiH_2Cl_2)/F(H_2)$  mass flow ratios. The associated activation energies  $E_{GR}$  (DCS) are reported in the figure.

to increase monotonously from 43.7 up to  $53.4 \text{ kcal mol}^{-1}$  with the SiH<sub>2</sub>Cl<sub>2</sub> partial pressure, which is to the best of our knowledge the first time that such a behavior is reported. A mean value of 49.3 kcal mol<sup>-1</sup> is associated to  $E_{\text{GR}}$  (DCS), to be compared to the 52.2 kcal mol<sup>-1</sup> value of Kongetira et al. [33]. This exponential dependence of the Si growth rate on the reverse absolute temperature is in fact related to the desorption of hydrogen from the silicon surface in order for silicon atoms to be incorporated. An activation energy of 47 kcal mol<sup>-1</sup> has indeed been found for hydrogen desorption from a Si(100) surface [34].

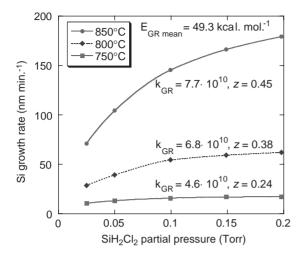

We have then plotted at 750°C, 800°C and 850°C the Si growth rate without HCl as a function of the DCS partial pressure in order to determine  $k_{\text{GR}}$  (DCS) and z (see Fig. 5). Mean values of  $6.4 \times 10^{10}$  and z = 0.36 are associated to those two constants. Our z value is half the one of Kongetira et al. (0.7).

We thus have three unknowns remaining,  $E_{\text{ET}}$ ,  $k_{\text{ET}}$  and y. The Si growth rate with some HCl added is given by:

GR<sub>with some HCl added</sub>(nm/min)

$$= k_{\rm GR}(\rm DCS)e^{-k_{\rm GR}(\rm DCS)/k_BT}(P_{\rm DCS})^{z}(P_{\rm H_2})$$

$$-k_{\rm ET}e^{-k_{\rm ET}/k_BT}(P_{\rm HCl})^{y}.$$

Fig. 5. Si growth rate at 750°C, 800°C and 850°C as a function of the dichlorosilane partial pressure. The associated  $k_{\text{GR}}$  (DCS) and z values are given next to each curve.

The etching rate by HCl is thus given by (for a given value of the  $SiH_2Cl_2$  flow):

$ER (nm/min) = k_{ET}e^{-E_{ET}/k_BT}(P_{HCl})^{y}$ = GR<sub>without HCl</sub> added - GR<sub>with some HCl</sub> added.

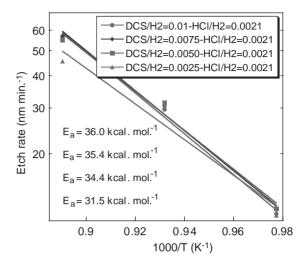

Proceeding in the same way as before (Arrhenius plot of the etching rate as a function of the reverse absolute temperature, see Fig. 6), values for  $E_{\rm ET}$  can be obtained. A mean value of 34.3 kcal mol<sup>-1</sup> is associated to this etching rate activation energy, to be compared to the 31.1 kcal mol<sup>-1</sup> value of Kongetira et al.

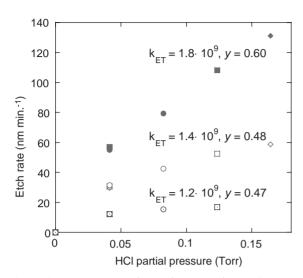

We have then plotted at 750°C, 800°C and 850°C the Si etching rate as a function of the HCl partial pressure to determine  $k_{\text{ET}}$  and y (see Fig. 7). Mean values of  $1.4 \times 10^9$  and y = 0.52 are associated to those two constants. Our y value is much lower than the one of Kongetira et al. (1.2).

The Si growth rate (at 20 Torrs on blanket wafers) as a function of the  $SiH_2Cl_2$  and HCl partial pressures (in Torr) and of the absolute temperature is thus given by:

$$GR(nm/min) = 6.4 \times 10^{10} e^{-49.3 \text{ kcal mol}^{-1}/k_{B}T} \times (P_{DCS})^{0.36} (P_{H_{2}}) - 1.4 \times 10^{9} \times e^{-34.3 \text{ kcal mol}^{-1}/k_{B}T} (P_{HCl})^{0.52}.$$

Fig. 6. Arrhenius plot of the Si etch rate by HCl as a function of the reverse absolute temperature for several  $F(\text{SiH}_2\text{Cl}_2)/F(\text{H}_2)$  mass flow ratios. The associated activation energies  $E_{\text{ER}}$  are reported in the figure.

This expression is valid in the low-temperature, H-desorption limited regime (i.e.  $T \leq 850^{\circ}$ C).

#### 4.2. The silane chemistry

By analogy with the model adopted just above for the dichlorosilane + hydrochloric acid chemistry, we have decided to use for the low-temperature ( $700^{\circ}C \leq T \leq 800^{\circ}C$ ) modeling of the Si growth rate with a silane chemistry the following equation:

#### GR(nm/min)

$$= k_{\text{GR}}(\text{SiH}_4) e^{-E_{\text{GR}}(\text{SiH}_4)/k_{\text{B}}T} (P_{\text{SiH}_4})^{W} (P_{\text{H}_2})$$

We have determined from an Arrhenius plot of the Si growth rate as a function of the reverse absolute temperature (as in Fig. 4) the growth activation energy  $E_{\rm GR}$  (SiH<sub>4</sub>) for several silane mass flows ( $F({\rm SiH}_4)/F({\rm H}_2)$  in between 0.0025 and 0.01). In opposition to dichlorosilane, the growth activation energy does not really depend upon the silane flow. A value of  $50.0 \pm$ 0.8 kcal mol<sup>-1</sup> is found for  $E_{\rm GR}$  (SiH<sub>4</sub>), very close to the mean activation energy found for the dichlorosilane chemistry, i.e.  $E_{\rm GR}$  (DCS)= 49.3 kcal mol<sup>-1</sup>.

Fig. 7. Si growth rate at 750°C, 800°C and 850°C as a function of the hydrochloric acid partial pressure. The associated  $k_{\rm ER}$ and y values are given next to each curve. Lozenges, squares and circles correspond to  $F({\rm SiH_2Cl_2})/F({\rm H_2})$  mass flow ratios equal to 0.01, 0.0075 and 0.0050, respectively. Full symbols (open symbols, open symbols with a dot in the middle) correspond to 850°C (800°C, 750°C) etch rates.

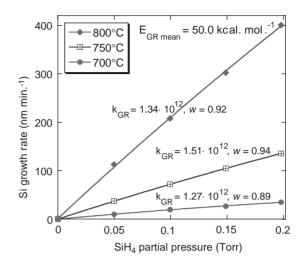

We have then plotted at 700°C, 750°C and 800°C the Si growth rate as a function of the SiH<sub>4</sub> partial pressure in order to determine  $k_{\text{GR}}$  (SiH<sub>4</sub>) and w (see Fig. 8). Mean values of  $1.4 \times 10^{12}$  and w = 0.92 are associated to those two constants. We thus have a close to linear  $(w = 0.92 \rightleftharpoons 1.0)$ dependency of the Si growth rate on the silane partial pressure (in agreement with previously reported results [35]), in stark contrast with the DCS, for which the dependency is strongly sublinear (z = 0.36). The fact that the growth rate is higher for silane that for dichlorosilane at a given temperature for the same mass flows [5] is partially accounted for by a rate constant more than twenty times higher for silane than for dichlorosilane ( $k_{GR}$  $(SiH_4) = 1.4 \times 10^{12}$  versus  $k_{GR}$  (DCS) =  $6.4 \times 10^{10}$ ).

The Si growth rate (at 20 Torrs on blanket wafers) as a function of the  $SiH_4$  partial pressure (in Torr) and of the absolute temperature is thus given by:

$GR(nm/min) = 1.4 \times 10^{12} e^{-50.0 \text{ kcal mol}^{-1}/k_{B}T} (P_{SiH_{4}})^{0.92} (P_{H_{2}}).$

Fig. 8. Si growth rate at 750°C, 800°C and 850°C as a function of the silane partial pressure. The associated  $k_{\text{GR}}$  (SiH<sub>4</sub>) and w values are given next to each curve.

This expression is valid in the low-temperature, H-desorption limited regime (i.e.  $T \leq 800^{\circ}$ C).

## 5. Selective epitaxial growth of Si on patterned wafers

We have also studied the low-temperature selective epitaxial growth of Si on patterned wafers using a dichlorosilane + hydrochloric acid chemistry. 92% of the surface area of those patterned wafers is covered by a 250 nm-thick LOCOS (LOCal Oxydation of Silicon) type thermally grown SiO<sub>2</sub> film. Si windows of varying sizes and shapes (mainly rectangular however, with sides along the  $\langle 110 \rangle$  directions) have been defined by optical lithography on each of the 49 dies (18 mm × 18 mm area each) of those patterned wafers. Those windows are approximately 110 nm below the surface of the LOCOS-covered parts of the wafers.

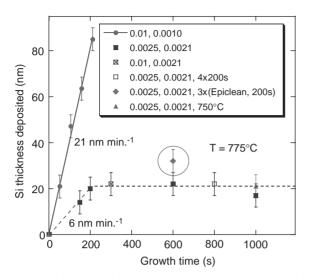

It is quite easy when plotting the Si deposited thickness as a function of the growth time to determine the associated growth rates (see Fig. 9). As far as the growth of Si using a dichlorosilane+hydrochloric acid chemistry is concerned, we have found on patterned wafers at  $775^{\circ}$ C

Fig. 9. Si thickness deposited inside  $(110 \,\mu\text{m} \times 110 \,\mu\text{m})$  Si windows of patterned wafers using a dichlorosilane + hydrochloric acid chemistry as a function of the growth time. The  $F(\text{SiH}_2\text{Cl}_2)/F(\text{H}_2)$  and the  $F(\text{HCl})/F(\text{H}_2)$  mass flow ratios are (from left to right) the first and the second numbers next to each type of symbol in the figure insert, respectively. The Si layer of the  $4 \times 200$  s sample has been deposited in 4 times 200 s, separated by growth interrupts under H<sub>2</sub> for 50 s. The Si layer of the  $3 \times (\text{EpiClean}, 200 \,\text{s})$  sample has been deposited in three times 200 s of growth, separated by ex-situ wet "EpiClean" wet cleaning. The growth temperature was always 775°C, except for one sample (for which it was 750°C).

significant differences between high and low  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  mass flow ratios (see Fig. 9).

For a  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  mass flow ratio equal to 0.1 (i.e.  $F(\text{SiH}_2\text{Cl}_2)/F(\text{H}_2) = 0.01$  and  $F(\text{HCl})/F(\text{H}_2) = 0.001$ ), the deposited thickness increases as expected linearly with the deposition time, with an associated growth rate of 21 nm min<sup>-1</sup>, very close to the one found on fullsheet wafers. Adding some HCl to SiH\_2Cl\_2 effectively suppresses at 775°C any *global* or *local* loading effect (i.e. the growth rate increase when switching between blanket and patterned wafers, and on patterned wafers between large and small Si windows).

With a  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  mass flow ratio equal to 0.8 (i.e.  $F(\text{SiH}_2\text{Cl}_2)/F(\text{H}_2) = 0.0025$  and  $F(\text{HCl})/F(\text{H}_2) = 0.0021$ ), we are faced at 775°C (and 750°C) with a limitation of the Si thickness deposited inside the Si windows of our patterned wafers at 20 nm. What is quite puzzling however is

that over the first 200s of the growth, the Si growth rate is very close to that found on fullsheet wafers (i.e.  $6 \text{ nm min}^{-1}$ ). Keeping in mind that the balance between the pure growth rate by SiH<sub>2</sub>Cl<sub>2</sub> and the etch rate by HCl might be affected by the fact that we are using patterned wafers, we have multiplied by four the SiH<sub>2</sub>Cl<sub>2</sub> mass flow with the same HCl mass flow (Si growth rate increase on fullsheet wafers from 6 up to  $14 \,\mathrm{nm\,min^{-1}}$ ), with no apparent effects. Growing for 800s in 4 times 200s separated by 50s of growth interrupt under  $H_2$  (hypothesis that the etch rate becomes more important than the pure growth rate over time on patterned wafers) does not enable to exceed this 20 nm limit either. Thinking that this 20 nm limit might be due to some chemical poisoning of the surface, we have also tried after 200 s of growth to take the wafer out of the cluster tool, clean-up the surface with the "EpiClean" recipe, re-load it, bake it with H<sub>2</sub> and deposit Si for another 200 s, then do this sequence all over again. This way, we have obtained (instead of the nominal  $3 \times 20$  nm = 60 nm) a Si deposited thickness slightly above 30 nm, which sort of validates at 775°C for high  $F(HCl)/F(SiH_2Cl_2)$  mass flow ratios this "chemical poisoning of the surface" theory. It should be noted that this 20 nm limit disappears (for the same SiH<sub>2</sub>Cl<sub>2</sub> and HCl mass flows) at 800°C [18].

We have however to be sure that this 20 nm deposited thickness limit is not an experimental artifact linked to an unintended etch of the LOCOS during the growth and thus to a step height measurement which is meaningless. We have therefore exposed 22 nm thick SiO<sub>2</sub> layers (grown at 800°C using a  $SiH_4 + N_2O$  chemistry onto Si(001)) to either a H<sub>2</sub> flow at  $1100^{\circ}$ C for up to  $300 \,\mathrm{s}$  or to a  $\mathrm{HCl} + \mathrm{H}_2$  gaseous mixture  $(F(HCl)/F(H_2) = 0.0021)$  at 800°C for up to 1000 s. The thickness difference as measured by SE is at most 0.25 nm, meaning that almost no thermally stable SiO<sub>2</sub> is consumed during a hightemperature H<sub>2</sub> bake (prior to epitaxy) or a selective epitaxial growth using a  $SiH_2Cl_2 + HCl$ chemistry. Similar conclusions were reached in the past by Oldham and Holmstrom [36] or Watts and Neudeck [37] (albeit at higher temperatures or higher growth pressures).

#### 6. Si growth kinetics on SOI wafers

Finally, we have worked on the growth of silicon (using either a) on SOIs substrates. Stateof-the-art SOI wafers from SOITEC with miscellaneous buried SiO<sub>2</sub> (BOX) and Si over-layers' thickness were used for this study. The eventual thinning of the Si over-layer (from for example the typical 2000 Å thickness of commercial wafers available nowadays down to 100 Å) was carried out thanks to several {dry oxidation-wet deoxidation} cycles.

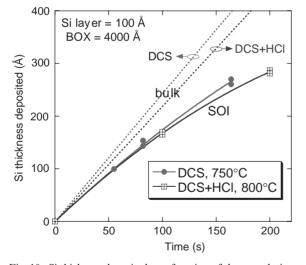

We have plotted in Fig. 10 the Si thickness deposited as a function of the growth time on bulk and on ultra-thin Si over-layer SOI substrates, this for a dichlorosilane only chemistry at  $750^{\circ}$ C or a dichlorosilane + hydrochloric acid chemistry at  $800^{\circ}$ C. The Si growth rate (slope of the curves) is significantly lower on those ultra-thin SOI wafers than on bulk wafers for both chemistries. What is also quite obvious is that the Si growth rate decreases with the thickness deposited on those ultra-thin SOI substrates, as attested by the slope reduction with time.

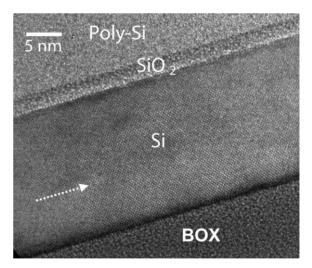

We have studied some of those ultra-thin SOI samples on which an epitaxy step was carried out using miscellaneous structural characterization methods. After the deposition of several tens of nm of Si, the surface is smoother, as attested by the lower root mean square roughness than prior to epitaxy: 0.9 Å versus 1.7 Å (AFM,  $(1 \mu m \times 1 \mu m)$ ) fields). No C, O or F contamination peak was observed in SIMS at the interface between the Si epilayer and the ultra-thin Si layer underneath for the kind of low thermal budget surface preparation described in Section 3 ( $800^{\circ}$ C,  $2 \min H_2$  bake). No interfacial contamination layer is observed in cross-sectional TEM either (see Fig. 11). The Si layer is perfect at the atomic scale, as attested by the absence of any defects such as stacking faults, etc. and by the prolongation of the atomic columns of the ultra-thin Si over-layer in the Si epilaver overhead.

A beneficial side effect of using an epitaxy step to thicken up the Si over-layer lays in the *macroscopic* smoothening of the surface. Indeed, the thickness standard deviation over a 200 mm substrate is typically of the order of 17% just after

Fig. 10. Si thickness deposited as a function of the growth time on un-patterned bulk (dotted lines) and ultra-thin (Si: 100 Å, BOX: 4000 Å) SOI wafers (symbols linked by full lines). The  $F(SiH_2Cl_2)/F(H_2)$  and the  $F(HCl)/F(H_2)$  mass flow ratios are equal to 0.0025 and 0.0021, respectively. The growth temperatures are equal to 750°C and 800°C for the dichlorosilane only and the dichlorosilane + hydrochloric acid chemistries, respectively.

Fig. 11. Cross-sectional high-resolution transmission electron microscopy image of an ultra-thin SOI wafer on which an epitaxy step was carried out (sample subsequently capped by  $3 \text{ nm of SiO}_2$  and 75 nm of poly-Si). The dotted arrow shows the approximate boundary between the Si epilayer and the Si seed layer underneath.

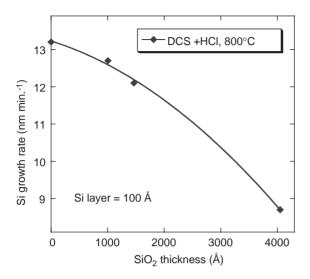

Fig. 12. Si mean growth rate (over 200 s of growth time) on ultra-thin (Si over-layer: 100 Å) SOI wafers as a function of the buried SiO<sub>2</sub> thickness. The  $F(SiH_2Cl_2)/F(H_2)$  and the  $F(HCl)/F(H_2)$  mass flow ratios are equal to 0.0025 and 0.0021, respectively. The growth temperature is equal to 800°C.

the several {dry oxidation-wet de-oxidation} thinning cycles necessary to bring the Si over-layer thickness from 2000 Å down to 100 Å. After an epitaxy of 100 Å of Si, it drops down to only 3% (49 points wafer mapping in SE).

We have also studied the impact of the BOX thickness upon the growth rate of Si for the SiH<sub>2</sub>Cl<sub>2</sub>+HCl chemistry at 800°C. Not unexpectedly, the Si growth rate converges towards the bulk value as the buried oxide gets thinner and thinner, as illustrated in Fig. 12. In the same manner, the growth rate, lower than the bulk value for ultra-thin SOI wafers (as illustrated in Fig. 10), increases with the Si over-layer thickness towards the bulk value. Indeed, the mean growth rate (over a 200 s growth time) on 100 Å thick Si over-layers is equal to  $8.7 \text{ nm min}^{-1}$  for the SiH<sub>2</sub>Cl<sub>2</sub>+HCl chemistry at 800°C (buried oxide thickness: 4000 Å). It goes up to  $12.3 \text{ nm min}^{-1}$  for 1400 Åthick Si over-layers. For bulk Si, it is equal to  $13.2 \,\mathrm{nm}\,\mathrm{min}^{-1}$ .

To the best of our knowledge, only one other study has dealt with the growth kinetics of Si of SOI wafers [38]. On thicker SOI wafers (4000 Å BOX, 500 Å thick Si over-layers), they have found that the growth rate, while being slightly lower than the bulk value for the first 1500 Å of Si deposited (as in Fig. 10), increased more or less monotonously with the deposited thickness. For 4500 Å of Si deposited, it was 25% higher than the bulk value. The behavior was explained in terms of wafer surface absorptivity and emissivity changes as the Si over-layer got thicker and thicker (see Ref. [38]).

#### 7. Conclusion

Using a RP-CVD cluster tool, we have studied at a growth pressure of 20 Torr the growth kinetics of Si on fullsheet, patterned and SOI wafers using either a dichlorosilane+hydrochloric acid or a silane chemistry.

We have first of all developed a ("HF-last" advanced wet cleaning + an 800°C, 2 min in situ  $H_2$  bake) low-thermal budget combination that yields atomically smooth, C, O and F free Si starting surfaces for both fullsheet and patterned wafers.

We have then modeled semi-empirically the Si growth rate with a dichlorosilane + hydrochloric acid chemistry on fullsheet wafers. It is given at 20 Torrs as a function of the SiH<sub>2</sub>Cl<sub>2</sub>, H<sub>2</sub> and HCl partial pressures (in Torr) and of the absolute temperature T by

GR (nm/min)

=

$$6.4 \times 10^{10} e^{-49.3 \text{ kcal mol}^{-1}/k_{\text{B}}T} (P_{\text{DCS}})^{0.36} (P_{\text{H}_2})$$

$- 1.4 \times 10^9 e^{-34.3 \text{ kcal mol}^{-1}/k_{\text{B}}T} (P_{\text{HCl}})^{0.52}.$

This expression is valid in the low-temperature, H-desorption limited regime (i.e. T < 1100 K). Using silane instead of dichlorosilane as the Si gaseous precursor leads to the following dependency of the Si growth rate at 20 Torrs on the SiH<sub>4</sub> partial pressure and the absolute growth temperature T (valid for T < 950 K):

GR (nm/min)

$$= 1.4 \times 10^{12} \mathrm{e}^{-50.0 \,\mathrm{kcal \, mol^{-1}/k_B T}} (P_{\mathrm{SiH}_4})^{0.92} (P_{\mathrm{H}_2})^{0.92}$$

On patterned wafers, we are faced at  $775^{\circ}$ C (and  $750^{\circ}$ C) with a limitation of the Si thickness deposited selectively inside the Si windows at

20 nm for high  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  mass flow ratios. This limit (thought to be due to some sort of chemical poisoning of the surface) disappears when (i) the growth temperature is increased up to 800°C (ii) the  $F(\text{HCl})/F(\text{SiH}_2\text{Cl}_2)$  mass flow ratio is substantially decreased at 775°C.

Finally, we have found that the growth rate is significantly lower on ultra-thin Si over-layer SOI wafers than on bulk ones. The difference between the two kinds of substrates gets less and less pronounced as the buried oxide layer gets thinner and/or the Si over-layer thickness increases. A Si over-layer thickened by an epitaxy step is of high crystalline quality, with a flatter surface and a higher thickness spatial homogeneity over the wafer surface than just after the thinning-down cycles.

#### Acknowledgements

G. Rabillé is gratefully acknowledged for his help in operating the Epi Centura and for the studies of the possible etching effects of  $SiO_2$  by  $H_2$ or HCl studies. The authors would also like to thank Dr. V. Loup for fruitful discussions. This work was carried out inside the Silicon Technology Department of LETI, CEA-Grenoble.

#### References

- R. Hull, J.C. Bean, Germanium Silicon: physics and materials, in: R.K. Willadson, E.R. Weber (Eds.), Semiconductors and Semimetals, Vol. 56, Academic Press, San-Diego, 1999.

- [2] F. Schäffler, Semicond. Sci. Technol. 12 (1997) 1515.

- [3] T.E. Whall, E.H.C. Parker, Thin Solid Films 368 (2000) 297.

- [4] L. Colace, G. Masini, G. Assanto, IEEE J. Quantum Electron. 35 (1999) 1843.

- [5] J.M. Hartmann, V. Loup, G. Rolland, P. Holliger, F. Laugier, C. Vannuffel, M.N. Séméria, J. Crystal Growth 236 (2002) 10.

- [6] J.M. Hartmann, F. Champay, V. Loup, G. Rolland, M.N. Séméria, J. Crystal Growth 241 (2002) 93.

- [7] J.L. Regolini, D. Bensahel, J. Mercier, Mater. Sci. Eng. B 4 (1989) 407.

- [8] M.R. Goulding, Mater. Sci. Eng. B 17 (1993) 47.

- [9] J.T. Fitch, J. Electrochem. Soc. 141 (1994) 1046.

- [10] L. Vescan, Mater. Sci. Eng. B 28 (1994) 1.

- [11] I.J. Raajmakers, H. Sprey, A. Storm, T. Bergman, J. Italiano, D. Meyer, J. Vac. Sci. Technol. B 17 (1999) 2311.

- [12] K. Miyano, I. Mizushima, K. Ohuchi, A. Hokazano, Y. Tsunashima, Jpn. J. Appl. Phys. 38 (1999) 2419.

- [13] L. Huang, J.O. Chu, D.F. Canaperi, C.P. D'Emic, R.M. Anderson, S.J. Koester, H.S. Philip Wong, Appl. Phys. Lett. 78 (2002) 1267;

L. Huang, J.O. Chu, S.A. Goma, C.P. D'Emic, S.J. Koester, D.F. Canaperi, P.M. Mooney, S.A. Cordes, J.L. Speidell, R.M. Anderson, H.S. Philip Wong, IEEE Trans. Electron. Dev. 49 (2002) 1566.

- [14] T. Mizuno, N. Sugiyama, T. Tezuka, S. Takagi, Appl. Phys. Lett. 80 (2002) 601;

T. Tezuka, N. Sugiyama, S. Takagi, T. Kawakubo, Appl. Phys. Lett. 80 (2002) 3560.

- [15] N. Sugii, S. Yamaguchi, K. Washio, J. Vac. Sci. Technol. B 20 (2002) 1891.

- [16] J. Pejnfors, S.-L. Zhang, J.V. Grahn, M. Östling, T.Winzell, in: M.D. Allendorf, M.L. Hitchman (Eds.), Chemical Vapor Deposition PV 2000-13, Vol. XV. The Electrochemical Society Proceedings Series, Pennington, NJ, 1999, p. 403.

- [17] P. Holliger, F. Laugier, J.C. Dupuy, Surf. Interface Anal. 34 (2002) 472.

- [18] J.M. Hartmann, A. Abbadie, F. Bertin, G. Rolland, F. Laugier, M.N. Séméria, P. Besson, P. Gentile, J. Crystal Growth, submitted for publication.

- [19] P. Besson, C. Cowache, J.M. Fabri, F. Tardif, A. Beverina, Diffusion Defect Data Part B 76–77 (2001) 199;

P. Besson, C. Cowache, J.M. Fabri, F. Tardif, A. Beverina, in: Proceedings of the Fifth International Symposium on Ultra-Clean Processing of Silicon Surfaces (UCPSS'00), Ostend, Belgium, 2000, p. 199.

- [20] B.S. Meyerson, F.J. Himpsel, K.J. Uram, Appl. Phys. Lett. 57 (1990) 1034.

- [21] T.Y. Hsieh, K.H. Jing, D.L. Kwon, T.H. Koshmieder, J.C. Thomspon, J. Electrochem. Soc. 139 (1992) 1971.

- [22] K. Oda, Y. Kiyota, J. Electrochem. Soc. 143 (1996) 2361.

- [23] C.L. Wang, S. Unnikrishnan, B.Y. Kim, D.L. Kwong, A.F. Tasch, Appl. Phys. Lett. 68 (1996) 108.

- [24] C.L. Wang, S. Unnikrishnan, B.Y. Kim, D.L. Kwong, A.F. Tasch, J. Electrochem. Soc. 143 (1996) 2387.

- [25] M. Caymax, S. Decoutere, E. Röhr, W. Vandervorst, M. Heyns, H. Sprey, A. Storm, J.-W. Maes, Solid State Phenom. 65–66 (1999) 237.

- [26] M.S. Carroll, J.C. Sturm, M. Yang, J. Electrochem. Soc. 147 (2000) 4652.

- [27] O. Vatel, S. Verhaverbeke, H. Bender, M. Caymax, F. Chollet, B. Vermeire, P. Mertens, E. André, M.M. Heyns, Jpn. J. Appl. Phys. Part2 (32) (1993) L1489.

- [28] H. Bender, S. Verhaverbeke, M. Caymax, O. Vatel, M.M. Heyns, J. Appl. Phys. 75 (1994) 1207.

- [29] M.C. Hersam, N.P. Guisinger, J.W. Lyding, D.S. Thompson, J.S. Moore, Appl. Phys. Lett. 78 (2001) 886.

- [30] P. Brabant, J. Wen, J. Italiano, T. Landin, N. Cody, L. Haen, in: Poster Presentation during the ISTDM 2003 Conference, Nagoya, Japan, 15–17th January 2003.

- [31] Y.W. Mo, M.G. Lagally, Surf. Sci. 248 (1991) 313.

- [32] B. Voigtländer, T. Weber, P. Šmilauer, D.E. Wolf, Phys. Rev. Lett. 78 (1997) 2164;

- B. Voigtländer, Surf. Sci. Rep. 43 (2001) 127.

- [33] P. Kongetira, G. Neudeck, C.G. Takoudis, J. Vac. Sci. Technol. B 15 (1997) 1902.

- [34] K. Sinniah, M.G. Sherman, L.B. Lewis, W.H. Weinberg, J.T. Yates Jr., K.C. Janda, Phys. Rev. Lett. 62 (1989) 567.

- [35] W.A.P. Claassen, J. Bloem, J. Crystal Growth 51 (1981) 443.

- [36] W.G. Oldham, R. Holmstrom, J. Electrochem. Soc. 114 (1967) 4.

- [37] J.S. Watts, G.W. Neudeck, J. Vac. Sci. Technol. B 14 (1996) 1670.

- [38] J. Pejnefors, S.-L. Zhang, H.H. Radamsson, M. Östling, Electrochem. Solid State Lett. 4 (2001) G98.