# Performance and Design Considerations for Gate-All-Around Stacked-NanoWires FETs

S. Barraud, V. Lapras, B. Previtali, M. Samson, J. Lacord, S. Martinie, M.-A Jaud, S Athanasiou, F. Triozon, O. Rozeau, et al.

# ▶ To cite this version:

S. Barraud, V. Lapras, B. Previtali, M. Samson, J. Lacord, et al.. Performance and Design Considerations for Gate-All-Around Stacked-NanoWires FETs. 2017 IEEE International Electron Devices Meeting (IEDM), Dec 2017, San Francisco, United States. 10.1109/IEDM.2017.8268473. cea-01973409

# HAL Id: cea-01973409 https://cea.hal.science/cea-01973409v1

Submitted on 8 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Performance and Design Considerations for Gate-All-Around Stacked-NanoWires FETs

S. Barraud¹, V. Lapras¹, B. Previtali¹, M.P. Samson², J. Lacord¹, S. Martinie¹, M.-A. Jaud¹, S. Athanasiou¹, F. Triozon¹, O. Rozeau¹, J.M. Hartmann¹, C. Vizioz¹, C. Comboroure², F. Andrieu¹, J.C. Barbé¹, M. Vinet¹, and T. Ernst¹¹CEA, LETI, MINATEC campus and Univ. Grenoble Alpes, 38054 Grenoble, France, email: <a href="mailto:sylvain.barraud@cea.fr">sylvain.barraud@cea.fr</a>

<sup>2</sup> STMicroelectronics, 850 rue J. Monnet, 38920 Crolles, France

Abstract—This paper presents recent progress on Gate-All-Around (GAA) stacked-NanoWire (NW) / NanoSheet (NS) MOSFETs. Key technological challenges will be discussed and recent research results presented. Width-dependent carrier mobility in Si NW/NS and FinFET will be analyzed, and intrinsic performance and design considerations of GAA structures will be discussed and compared to FinFET devices with a focus on electrostatics, parasitic capacitances and different layout options. The results show that more flexibility can be achieved with stacked-NS transistors in order to manage power-performance optimization.

## I. INTRODUCTION

Gate-All-Around (GAA) FETs have long been recognized as offering the best solution to short-channel-effects (SCE) with a high current drivability per layout footprint due to 3D vertically stacked channels [1-4]. Moreover, horizontal GAA NW and NS also have the advantage of being fabricated with minimal deviation from FinFET (FF) devices in contrast to vertical NWs which require more disruptive technological changes. For these reasons, the GAA stacked-wire MOSFET architecture is today regarded as an attractive option to push CMOS scaling beyond 7/5nm nodes. Although the first 3D GAA stacked-wires transistors were demonstrated ten years ago [1-4], significant progress have been reported last year [5-6] with aggressive 44/48nm CPP (Contacted Poly Pitch) ground rules [7]. In this paper, we will first discuss recent progress on the fabrication of GAA stacked-wires FETs. Then, we shall be paying particular attention to intrinsic performances and design considerations of GAA structures (NW and NS) for an optimal performance and power efficiency vs. FF.

## II. SCALING AND DEVICE ARCHITECTURE

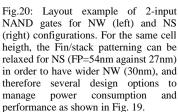

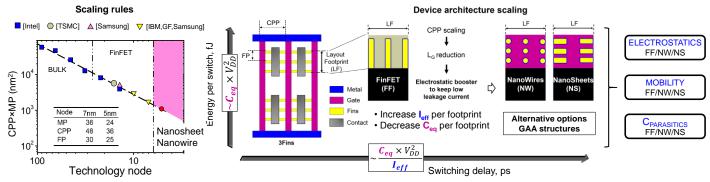

For several decades, the Si CMOS technology has enabled manufacturers to produce integrated circuits with everincreasing levels of performance and functionality. For example, **Fig. 1** presents the scaling rules of CPP and metal pitch (MP) from 90nm-*Bulk* to 7nm-*FinFET* architectures. If chipmakers seek to extend FinFET scaling at the 5nm node and beyond, they will likely need to move to the evolutionary alternative of GAA MOSFET architecture in order to keep low leakage current as the gate length gets smaller. Over the last year, GAA stacked-NW/NS MOSFETs were successfully demonstrated with a replacement metal gate (RMG) process [5-7]. GAA stacked-NWs FETs, which are close to the RMG FinFET technology, have nevertheless specific technical requirements. They are numbered "1 to 5" in **Fig. 2**. The fabrication started with the epitaxial growth of (*Sio.7Geo.3/Si*)

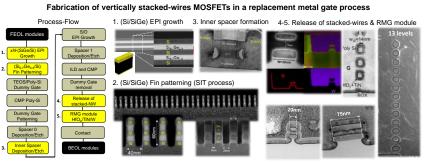

multilayers with ideally sharp interfaces. Then, dense arrays of fins were patterned to fabricate stacked-wires FETs. Multiple patterning techniques were used in order to meet the density targets of advanced nodes. After that, dummy gates and spacers were defined prior to the anisotropic etching of the (SiGe/Si) multilayers. Then, the SiGe layers were partially etched selectively to the Si ones to form inner spacers well-aligned and correctly dimensioned as shown in Fig. 2. Such spacers are essential in order to minimize parasitic capacitance. Finally, the Si wires were released during the RMG module prior to conformal HfO2/TiN/W gate deposition. Nanowire widths up to 50nm [7] and even 75nm [6] were reported and the possibility to stack up to 13 NW levels without any strain relaxation was demonstrated [8]. In order to evaluate the benefits of GAA structures (NW and NS), the carrier mobility, electrostatics and parasitics should holistically be assessed from power/performance optimization perspective. This is discussed in the next sections. Fig. 3 shows the guideline proposed to benchmark FinFET and GAA architectures. The dimensions of devices are consistent with recent experimental results reported in ref. [7]. The layout footprint (LF), the fin and stack thickness as well as the fin-to-fin space (S={LF-N× $W_{Fin}$ }/{N-1}) are assumed constant for the three devices.

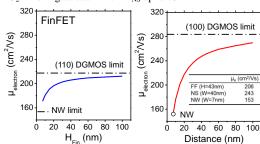

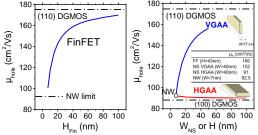

# III. CARRIER MOBILITY

Although electrostatic control is excellent in GAA NW FETs as the gate length becomes smaller, significant changes in transport properties associated to atomically small (<10nm) dimensions can alter device performance. The size-dependent carrier mobility in 3D multi-gate devices is primarily governed by facet-dominated transport [9-10] with high (resp. low) electron mobility in the (100) (resp. (110)) plane and high (resp. low) hole mobility in the (110) (resp. (100)) plane. Meanwhile, mobility in conventional NWs is often the worst due to additional quantum confinement effects resulting in rapid degradation in mobility at smaller size due to phonon and surface roughness scattering [11-14] (Fig. 4). Basically, as shown in **Figs. 5-6**, the computed carrier mobility interpolates between the Si NW and thin film limits [15]. For electrons, [110] n-FETs with width W>H show larger mobilities than those with H>W. This can be explained by band structure effects [16]. The  $\Delta$  valleys split into light (m\*=0.19m<sub>0</sub>)  $\Delta_z$ valleys at  $\Gamma$  and heavier (m\*=0.55m<sub>0</sub>)  $\Delta_{x,y}$  valley off  $\Gamma$ . In the strong inversion regime, the electron gas is mostly confined in the light  $\Delta_z$  valleys on the top and bottom (001) facets, and in the heavier  $\Delta_{x,y}$  valleys on the lateral (110) facets. Therefore, wide [110] Si NS (W<sub>NS</sub>>20nm) with dominant (001) facets

(W>H) perform better than tall [110] Si fin with dominant (110) facets (W<H). The trends are opposite for p-FETs, with a significant hole mobility improvement in [110] p-FET with H>W. Horizontal GAA NS for n-FETs and vertical GAA NS for p-FETs turn out to be the most effective solutions to promote electron and hole transport, respectively.

# IV. PERFORMANCE AND DESIGN CONSIDERATIONS

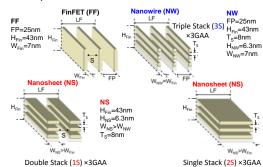

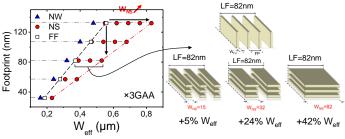

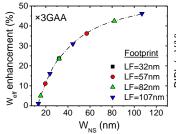

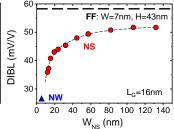

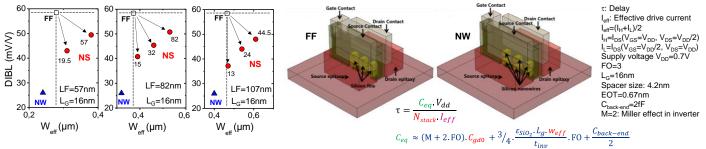

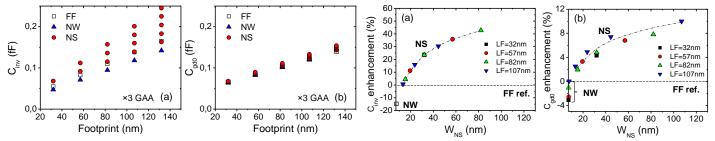

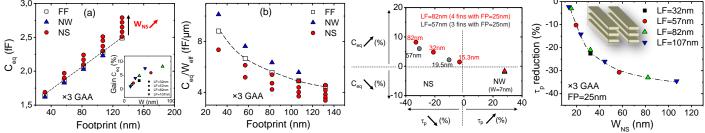

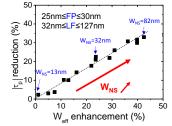

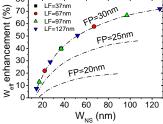

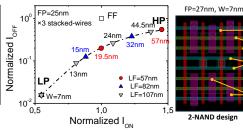

In early days of CMOS, the FinFET technology alleviated several important challenges associated with the aggressive scaling of planar bulk CMOS devices. Such a strategy allowed to preserve robustness to SCE, but more importantly resulted in improved circuit delay owing to 3D integration and vertical channel orientation. This allowed the transistors to deliver more performance due to higher effective width (W<sub>eff</sub>) per footprint. This idea must continue to be considered for GAA structures [17-18]. As shown in **Fig. 7**, the GAA NS structures could instead be used to maximize the effective width for a given layout footprint, which will improve the drive current without increasing power density. As compared to FinFET, the conventional square (or round) NW has a lower Weff for a given layout footprint while the effective width can be significantly enhanced with wide and thin NS compared to conventional FinFETs, as shown in Fig. 8. A large footprint allows wider NS which yields higher W<sub>eff</sub> and ultimately better performances while maintaining Drain-Induced-Barrier-Lowering (DIBL) lower than in short-channel FinFET devices, as shown in Fig. 9. Basically, the DIBL vs. W<sub>eff</sub> for a given footprint are plotted in Fig. 10 to clearly emphasize the trade-off between the channel electrical width which govern the intrinsic performance of devices (modulated by the carrier mobility discussed above) and the immunity to SCE. In considering three layout footprints and a 16nm gate length, Fig. 9 shows that GAA stacked-NS can be thought of as a practical compromise between speed and power dissipation. However, to make the best of GAA stacked-NS structures, effective current I<sub>eff</sub> enhancement achieved by higher  $\mu_{\text{eff}}$  and  $W_{\text{eff}}$  should not be canceled by an excessive increase in parasitic capacitances. This argument is often to the fore when arguing against the development of stacked-NW/NS transistors. Indeed, a significant increase of parasitic capacitance will impact circuit performance by increasing the load capacitance Ceq defined in Fig. 11 and increasing the switching delay  $\tau_p$ . Fig. 12 summarizes the calculation of gateto-channel capacitance (C<sub>inv</sub>) in inversion regime and gate-todrain capacitance (Cgd0) of FinFET and GAA structures used in this work. While there are inevitably an increase of C<sub>inv</sub> for wider GAA NS structures due to increased W<sub>eff</sub>, the C<sub>gd0</sub> capacitance is less sensitive to a change in width of NS [18]. The rate of increase in  $C_{inv}$  and  $C_{gd0}$  capacitances for FinFET is shown in Fig. 13. +28% improvement in C<sub>inv</sub> is achieved against only 6% in C<sub>gd0</sub> at 40nm width (W<sub>NS</sub>). Since the gateto-drain capacitance depends slowly on W<sub>NS</sub>, and assuming the same wiring load capacitance of back-end of line (Cback-end) for the three devices (FF, NW and NS), the metric  $C_{eq} \times V_{DD}/I_{eff}$ must be improved at constant layout footprint. I<sub>eff</sub> represent the effective current and is defined in Fig. 11. The effective capacitance C<sub>eq</sub> defined as the sum of the three contributions  $(C_{inv}, C_{gd0})$  and  $C_{back-end}$  is shown in **Fig. 14**. The larger the footprint will be (allowing wide width of NS), the larger C<sub>eq</sub> will be due to the effective width enhancement. However, it should be noted that C<sub>eq</sub> normalized by W<sub>eff</sub> can be significantly reduced for wide NS widths. Likewise, the switching delay has been calculated for different layout footprints. The delay and C<sub>eq</sub> reduction over FinFET is shown in Fig. 15 for LF=57nm (resp. 82nm) related to a 3-fins library cell (resp. 4-fins library cell). C<sub>eq</sub> is reduced for NWs (W=7nm) but no delay reduction is achieved, while performance can be significantly improved for nanosheet design having wider wires. A delay reduction of around 20% is expected for W<sub>NS</sub>~30nm. As shown in Fig. 16 and Fig. 17, nanosheets have a more effective width for a given footprint and therefore drive a capacitive load better [6,17,18]. The benefit offered by GAA stacked-NS enabling to relax the fin pitch by using double or triple stack to match or overcome the effective width at constant footprint may be reduced when considering ultra-scaled standard cell height with small fin pitch and few fins. The reduction of fin number and fin pitch (Fig. 18) will result in lower NS width: the W<sub>eff</sub> enhancement and the  $\tau_p$  reduction may then be minimized. Finally, a fine tuning of NS width with EUV lithography would tentatively result in improved power/performance management through the modulation of threshold voltage and subthreshold slope, as shown in Fig. 19. For a given cell height, Fig. 20 give an example of 2-input NAND gate with two possible wire widths (7 and 30nm).

#### V. CONCLUSION

Obviously, the technological challenges facing the development of a new technology platform featuring GAA nanosheet transistors are still numerous (shape optimization with reduced roughness, inner spacer, access optimization and strain management). Nonetheless, some significant experimental advances have been made recently and show the high competitiveness of this technology for future technology nodes. Nanosheet transistors offers more freedom to designers for the power-performance optimization thanks to a fine tuning of the device width.

# ACKNOWLEDGMENT

This work was partly funded by the French Public Authorities through the NANO 2017 program and EQUIPEX FDSOI11. It is also partially funded by the SUPERAID7 (grant N° 688101) project.

### REFERENCES

[1] T. Ernst et al., IEDM, 10.1109/IEDM.2006.346955, 2006, [2] L.K. Bera et al., IEDM, 10.1109/IEDM.2006.346841, 2006, [3] C. Dupré et al., IEDM, 10.1109/IEDM.2008.4796805, 2008, [4] E. Bernard et al., VLSI, pp. 16-17, 2008, [5] H. Mertens et al., VLSI, 10.1109/VLSIT.2016.7573416, 2016, [6] S. Barraud et al., IEDM, 10.1109/IEDM.2016.7838441, 2016, [7] N. Loubet et al., VLSI, 10.1109/VLSIT.2017, 2017, [8] T. Ernst et al., Micro. Eng., vol. 88, pp. 1198-1202, 2011, [9] J. Chen et al., VLSI, pp. 32-33, 2008, [10] J. Chen et al., VLSI, pp.175-176, 2010, [11] Y.M. Niquet et al., ULIS, pp.49-52, 2012, [12] N. Neophytou et al., PRB, 84, pp. 085313-185313-15, 2011, [13] S. Jin et al., JAP, 102, pp.083715—1 083715-14, 2007, [14] M.V. Fischette al., JAP, 80, pp. 2234-2252, 1996, [15] Z. Zaiping et al., IEEE TED, 64, pp. 2485-2491, 2017, [16] Y.M. Niquet et al., NanoLetters, 12, pp. 3545-3550, 2012, [17] S.-D. Kim et al., S3S, 10.1109/S3S.2015.73335212015, [18] L. Gaben et al., SSDM, 2015, [19] J. Lacord et al., IEEE TED, 63, pp. 781-786, 2016.

Fig.1: (Left) Standard cell area scaling vs. technology node. (Right) The CMOS scaling is governed by the Contacted Poly Pitch (CPP) in the x-direction and the Metal Pitch (MP) in the y-direction. At 5nm node, two GAA structures (NW and NS) can be proposed as an alternative to FinFET. Electrostatics confinement, carrier mobility and parasitics need to be investigated in order to minimize the effective load capacitance (C<sub>eq</sub>) and/or maximize the effective drive current (I<sub>eff</sub>).

Fig.2: Process flow of stacked-NW/NS FETs. The steps numbered '1' to '5' are specific technical requirements for NW/NS FETs (as compared to FinFET devices). Cross-sectional Transmission Electron Microscopy (TEM) images are shown at various stages of the fabrication process. (1) Growth of (Si/SiGe) superlattices with 3 levels of Si layers stacked upon one another; (2) Etching of (Si/SiGe) fins with a SIT process; (3) Stacked-wires FETs after the integration of inner spacers and (4-5) stacked-NS FETs with a HfO<sub>2</sub>/TiN/W gate stack with  $W_{\rm NS}$  up to 75nm.

Fig.3: Guideline for benchmarking FinFET and GAA stacked-NW/NS architectures. For a given footprint (LF) and Fin thickness ( $H_{\rm Fin}$ ), several GAA Nanosheets structures (single-, double-, triple-stack, etc.) can be considered to overcome FinFET performance thanks to higher effective width. S is defined as (LF-N×W<sub>Fin</sub>)/(N-1).

Fig.4: Experimental data of surface-roughness limited mobility (N<sub>inv</sub>=10<sup>13</sup> cm<sup>-2</sup>) vs. W<sub>wire</sub> at 10K.

Fig.5: (Left)  $\mu_{electron}$  (N $_{inv}=10^{13}cm^{-2})$  vs.  $H_{Fin}$  for [110] FinFET transistors (W=7nm). (Right)  $\mu_{electron}$  vs.  $W_{NS}$  for [110] GAA NW and NS FETs (H=7nm). The horizontal doted lines are the reference in (110) and (100) double-gate FET.

Fig.6: (Left)  $\mu_{hole}$  ( $N_{inv}=10^{13}cm^{-2}$ ) vs.  $H_{Fin}$  for [110] FinFET transistors (W=7nm). (Right)  $\mu_{hole}$  vs.  $W_{NS}$  or H for [110] horizontal (HGAA, H=7nm) and vertical (VGAA, W=7nm) GAA FETs.

Fig.7: In contrast to NWs and FinFETs, a significant increase in  $W_{\rm eff}$  can be achieved with GAA NS transistors for a given footprint (LF). The wider  $W_{\rm NS}$  will be, the higher the effective width enhancement will be. Computations done for a stack of 3 GAA with the dimensions of devices given in Fig. 3.

Fig.8:  $W_{eff}$  enhancement (compared to FF with FP=25 nm) vs.  $W_{NS}$  for different layout footprints (LF). Here,  $H_{NS}$ = $H_{NW}$ =6.3nm (cf. Fig. 3).

Fig.10: DIBL vs. Weff for three layout footprints. A better compromise between high Weff and low DIBL is achieved for GAA stacked-NS structures. If low DIBL is shown for NW, W<sub>eff</sub> is strongly reduced vs NS. H<sub>NS</sub>=H<sub>NW</sub>=6.3nm (cf. Fig. 3).

Fig.11: Bird view of FinFET and stacked-NW structures used for TCAD simulations of parasitic capacitances and delay computation. The effective load capacitance  $C_{\text{eq}}$  results from (i) the gatedrain capacitance C<sub>gd0</sub>, (ii) the inversion capacitance and (iii) the back-end component [19]. A thin SiN spacer width is considered ( $W_{spacer}$ =4.2nm). Other device dimensions are given in Fig. 3.

Fig. 12: Inversion (a) and gate-to-drain (b) capacitances vs. layout footprint for FF and stacked-NW/NS structures. As compared to FF (with FP=25nm) devices, an increase of W<sub>NS</sub> for a constant footprint results in a C<sub>inv</sub> enhancement due to higher  $W_{\text{eff}}$ . However, a small improvement of  $C_{\text{gd0}}$  is observed as  $W_{\text{NS}}$  increases.

Fig.13:  $C_{inv}$  (a) and  $C_{gd0}$  (b) enhancement over FinFET (with FP=25nm) for stacked-NS/NW structures. Capacitances are calculated for different layout footprints (LF). Whatever the LF,  $C_{inv}$  and  $C_{gd0}$  increase with  $W_{NS}$  (+ 28% improvement for  $C_{inv}$  against only + 6% for  $C_{gd0}$  at  $W_{NS}$ =40nm).

Fig.14: (a) Effective load capacitance  $C_{\text{eq}}$  as a function of LF for FF (with FP=25nm) and stacked-NW/NS structures. The larger the footprint is, the wider the NS will be, resulting in larger  $C_{\text{inv}}$  contribution at high  $W_{\text{eff}}$ . However, the normalized effective load capacitance is significantly reduced for NS (b).

Fig.15:  $\tau_p$  and  $C_{eq}$  reduction over FinFET (with FP=25nm) technology for different LF. A  $\tau_{\text{p}}$  reduction of ~20 % is expected at W<sub>NS</sub>=30nm.

Fig.16: Delay reduction over FF technology (with FP=25nm) different footprints (LF). The delay reduction is mainly dependent on  $W_{NS}$ .

Fins

Dumm

NS

2-NAND design

FP=54nm, W<sub>NS</sub>=30nm

Fig.17: Whatever the FP and LF values,  $\tau_p$  is reduced in NS as  $W_{\text{eff}}$ increases, with over improvement devices. Wider NS yield reduced

Fig.18: Effective width enhancement (compared to FF devices related to different fin pitch FP) vs. W<sub>NS</sub> for different layout footprints (LF). The fin pitch reduction results in lower WNS values and therefore lower effective The switching width. delay reduction will then be less.

Fig.19: Normalized I<sub>OFF</sub> vs. I<sub>ON</sub> current (over FinFET FP=25nm) for  $L_G=16nm$ . A tuning of the NS width allows one to modulate the threshold voltage and the substhreshold slope, enabling a better performance-power optimization.