## Vertically Stacked-NanoWires MOSFETs in a Replacement Metal Gate Process with Inner Spacer and SiGe Source/Drain

S. Barraud, V. Lapras, M. P. Samson, L Gaben, L. Grenouillet, V Maffini-Alvaro, Y. Morand, J Daranlot, N. Rambal, B Previtalli, et al.

### ▶ To cite this version:

S. Barraud, V. Lapras, M. P. Samson, L Gaben, L. Grenouillet, et al.. Vertically Stacked-NanoWires MOSFETs in a Replacement Metal Gate Process with Inner Spacer and SiGe Source/Drain. 2016 IEEE International Electron Devices Meeting (IEDM), Dec 2016, San Francisco, United States. 10.1109/IEDM.2016.7838441. cea-01973383

## HAL Id: cea-01973383 https://cea.hal.science/cea-01973383

Submitted on 8 Jan 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Vertically Stacked-NanoWires MOSFETs in a Replacement Metal Gate Process with Inner Spacer and SiGe Source/Drain

S. Barraud<sup>1</sup>, V. Lapras<sup>1</sup>, M.P. Samson<sup>2</sup>, L. Gaben<sup>1,2</sup>, L. Grenouillet<sup>1</sup>, V. Maffini-Alvaro<sup>1</sup>, Y. Morand<sup>2</sup>, J. Daranlot<sup>1</sup>, N. Rambal<sup>1</sup>, B. Previtalli<sup>1</sup>, S. Reboh<sup>1</sup>, C. Tabone<sup>1</sup>, R. Coquand<sup>1</sup>, E. Augendre<sup>1</sup>, O. Rozeau<sup>1</sup>, J. M. Hartmann<sup>1</sup>, C. Vizioz<sup>1</sup>, C. Arvet<sup>2</sup>, P. Pimenta-Barros<sup>1</sup>, N. Posseme<sup>1</sup>, V. Loup<sup>1</sup>, C. Comboroure<sup>2</sup>, C. Euvrard<sup>1</sup>, V. Balan<sup>1</sup>, I. Tinti<sup>1</sup>, G. Audoit<sup>1</sup>, N. Bernier<sup>1</sup>, D. Cooper<sup>1</sup>, Z. Saghi<sup>1</sup>, F. Allain<sup>1</sup>, A. Toffoli<sup>1</sup>, O. Faynot<sup>1</sup>, and M. Vinet<sup>1</sup>

<sup>1</sup>CEA, LETI, MINATEC campus and Univ. Grenoble Alpes, 38054 Grenoble, France, email: <a href="mailto:sylvain.barraud@cea.fr">sylvain.barraud@cea.fr</a>

<sup>2</sup> STMicroelectronics, 850 rue J. Monnet, 38920 Crolles, France

Abstract—We report on vertically stacked horizontal Si NanoWires (NW) *p*-MOSFETs fabricated with a replacement metal gate (RMG) process. For the first time, stacked-NWs transistors are integrated with inner spacers and SiGe sourcedrain (S/D) stressors. Recessed and epitaxially re-grown SiGe(B) S/D junctions are shown to be efficient to inject strain into Si *p*-channels. The Precession Electron Diffraction (PED) technique, with a nm-scale precision, is used to quantify the deformation and provide useful information about strain fields at different stages of the fabrication process. Finally, a significant compressive strain and excellent short-channel characteristics are demonstrated in stacked-NWs *p*-FETs.

#### I. INTRODUCTION

The vertically stacked wires MOSFET architecture pushes further the scaling limits of the CMOS technology [1-4]. Now deemed as a possible extension to FinFET, it offers multiple benefits. A low I<sub>OFF</sub> current is indeed expected, thanks to multigate electrostatic control, with a high current drivability due to 3D vertically stacked channels [3-5]. Obviously, major roadblocks still remain to reach higher performances, in particular, stress boosters and parasitic capacitances. Gate-All-Around (GAA) MOSFETs based on Si NWs that call upon RMG FinFET process technology were recently reported [6-7]. Nevertheless, none of them demonstrated the integration of inner spacers which is key in order to reduce gate-source/drain capacitances in such a 3D integration process. In this work, we introduced, for the first time, inner spacers and SiGe S/D in a RMG stacked wires process. Wider, thinner and stacked wire structures have been proven to be efficient to match or exceed FinFETs performance due to higher W<sub>eff</sub>/footprint ratio [8-9]. The strain engineering requires also dedicated optimization because of the opportunities brought to the channel to relax. The morphological strain evolution along the fabrication process will be presented thanks to PED technique [10] and then, we will quantify electrical performance of stacked-NWs p-FETs.

#### II. DEVICE FABRICATION

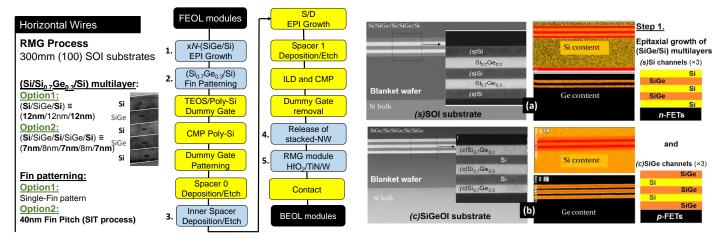

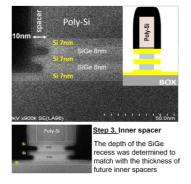

The RMG process flow for vertically stacked-NWs MOSFETs is presented in **Fig. 1**. The transistors are processed on 300 mm SOI substrates. GAA stacked-NWs FETs, which are close to the RMG FinFET technology, have nevertheless specific technical requirements. They are numbered "1 to 5" in

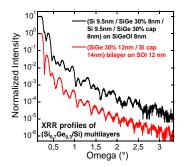

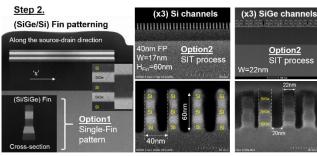

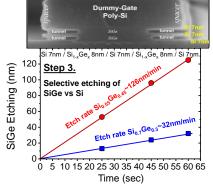

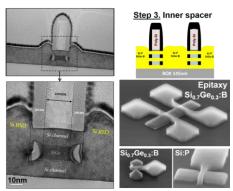

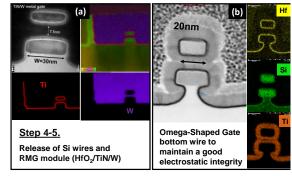

Fig. 1. The fabrication starts with the epitaxial growth of  $(Si_{0.7}Ge_{0.3}/Si)$  multilayers on blanket SOI substrates. Growth pressure was 20 Torr, while the growth chemistry changed between SiGe (SiH<sub>2</sub>Cl<sub>2</sub> + GeH<sub>4</sub>) and Si (SiH<sub>4</sub>), in order to have satisfying growth rates at 650°C [11]. Different Si/SiGe stacks have been investigated: (i) a (Si/SiGe/Si)-stack for which the two Si channels and the sacrificial SiGe layer have thicknesses around 12 nm and (ii) a (Si/SiGe/Si/SiGe/Si) multilayer with lower layer thicknesses (7 nm for Si and 8 nm for the SiGe layers). They should yield two and three stacked Si channels, respectively. Fig. 2a (resp. 2b) shows TEM images and Energy-Dispersive X-ray (EDX) spectroscopy maps of (SiGe/Si) multilayers grown on strained-SOI (resp. SiGeOI) substrates in order to have  $\times 3$  tensile strained Si channels for n-FETs (resp.  $\times 3$  compressive strained SiGe channels for p-FETs). X-ray reflectivity (XRR) measurements were performed on each multilayer in order to have a precise determination of individual layer thicknesses (Fig. 3). Then, individual and dense arrays of fins were patterned to fabricate stacked-NWs FETs. The Sidewall Image Transfer technique (SIT) was used in order to meet the density targets of advanced nodes. Fig. 4 shows TEM images after etching of (SiGe/Si)-fins along transverse and longitudinal directions. Our SIT-based patterning technique yields 40 nm-pitch fins which are 60 nm high and roughly 20 nm wide. After that, dummy gates and spacers were defined prior to the anisotropic etching of the (SiGe/Si) multilayers. Then, the SiGe layers were partially etched selectively to the Si ones. Etching rates and selectivity of SiGe were studied on (Si/SiGe/Si/SiGe/Si) stacks with low layer thicknesses (7 nm for Si and 8 nm for SiGe) (Fig. 5). An excellent selectivity was achieved even for thin Si and SiGe layers. Then, the depth of the SiGe recess was adjusted to match the thickness of future inner spacers (Fig. 6). A nitride layer was deposited in the cavities with a thickness optimized for the spacer etch sequence that followed. Fig. 7 shows TEM images of stacked-NWs FETs with inner spacers well-aligned and correctly dimensioned. The process then continued with the epitaxial growth of Si<sub>0.7</sub>Ge<sub>0.3</sub>:B raised-S/D [12]. The Si wires were released during the RMG fabrication module. This selective etch process was followed by a conformal HfO<sub>2</sub>/TiN/W deposition (**Fig. 8**). An optimized  $\Omega$ -shaped gate Si channel was used for bottom wire to maintain a good electrostatic integrity (Fig. 8b).

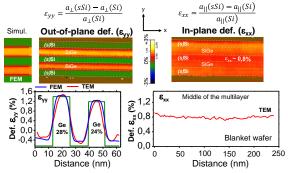

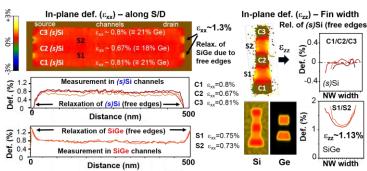

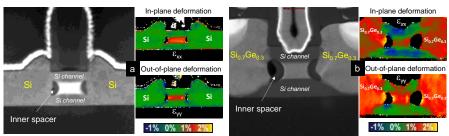

#### III. STRAIN CHARACTERIZATION AND MODELING

Of all the challenges that we face for GAA stacked-NWs FETs, one of the most important is the strain engineering which is used to improve short-channel performances. We have thus imaged strain fields at different stages of our fabrication process. Strain maps were obtained by TEM using the PED technique. Interpretation of the results in terms of elastic strains and stresses required some modeling. In TEM, it is indeed mandatory to consider the specimen thickness to account for elastic relaxation [13]. Hence, we developed 3D Finite Element Method (FEM) based models that include the anisotropy of the system and the materials. Stress relaxation is taken into account by building thin-foil geometries with free lateral faces. Strain values were taken as average values along the specimen thicknesses and projected in 2D as in the experiments [14]. Computations, as experiments, are presented with respect to a relaxed Si ref. In Fig. 9, we present strain maps for a blanket stack grown on a sSOI substrate. The measured deformation  $\varepsilon_{vv}$ and  $\varepsilon_{xx}$  are shown together with the TEM lamella calculations. The reconstruction of the bulk (before lamella relaxation) resulted from a validated TEM-specimen model. The vertical profiles extracted from the strain maps show that the Si layers are seen as being slightly compressed in the growth direction (by approx. -0.4%). This is due to the fact that the Si is in-plane  $(\varepsilon_{xx})$  tensile-strained by around 0.8%. The Ge-content in the SiGe layers is adjusted in the TEM-specimen model, to fit the experiments, allowing therefore to extract Ge-content in the layers. We determined that the first layer contained 24% of Ge and the second 28%. In **Fig. 10**, we present  $\varepsilon_{xx}$  and  $\varepsilon_{zz}$  strain results after fin patterning. Strain relaxation effects are seen on the free edges of the structure. The  $\varepsilon_{xx}$  map shows that, as expected on a sSOI substrate, the sSi and the SiGe layers have larger in-plane lattice parameters than the Si ref.. Horizontal profiles from the three sSi channels have been extracted. In the center, the in-plane tensile strain is still around 0.8%, consistently with measurements on blanket wafers. However, the integration of inner spacers may induce a strain relaxation after the anisotropic etching of (SiGe/Si) superlattices (see Fig. 6). Then, SiGe(B) raised-S/Ds can be used to inject significant amounts of compressive strain in Si channels. This is well observed in Fig. 11b. The level of in-plane deformation in Si p-channels became close to 1%. Meanwhile, no strain was generated by using Si raised-S/Ds (Fig. 11a). Note in Fig. 11a, that the sacrificial SiGe layer between the two Si channels has larger lattice parameter than the Si ref. ( $\varepsilon_{xx} = 1.3\%$ ). This shows that the SiGe has partially relaxed during the integration of the inner spacers. Indeed, similar levels of deformation than those obtained on relaxed SiGe at free edge locations (see Fig. 10) are shown. This result suggests that an optimized engineering of process-induced stress techniques such as SiGe S/Ds (for p-FET) can be efficient in 3D stacked-NWs devices.

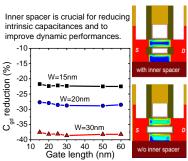

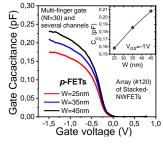

#### IV. ELECTRICAL CHARACTERISTICS

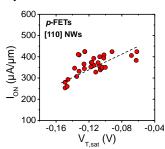

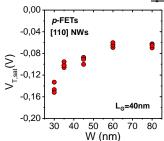

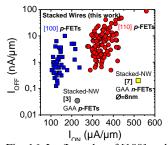

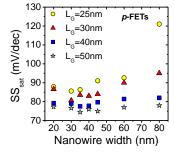

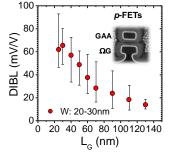

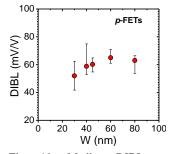

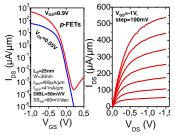

Before discussing the performances of stacked-NWs FETs, we show, in Fig. 12, the benefit of inner spacers in order to reduce parasitic capacitances. This is a particularly important point since thin and wide nanowires are expected to enhance drive current by increasing the effective width [8,9]. Gate capacitance vs  $V_{GS}$  of stacked wires p-FETs with W=25-45 nm and 500 nm gate length is shown in **Fig. 13**. The CV curves, obtained from a multi-fingers gate and an array (#120) of stacked wires, show a consistent dependence on the top view wire width, W. In Fig. 14, a linearity is well observed between the saturation threshold voltage  $V_{T,sat}$  and the  $I_{ON}$  current (normalized by the channel perimeter). This indicates that the increase of I<sub>ON</sub> current (for 25nm<L<sub>G</sub><70nm) takes place under SCE. The impact of top view channel-width on V<sub>T,sat</sub> is shown in Fig. 15. An increase of confinement potential as W is reduced leads to higher V<sub>T,sat</sub>. Low values of V<sub>T,sat</sub> are explained by the compressive strain induced by the SiGe S/D. The I<sub>ON</sub> vs I<sub>OFF</sub> current is plotted in **Fig. 16** for [100] and [110] Si channels. The latest results of GAA stacked-NWs are reported [3, 7]. Improved performance of p-FETs devices is achieved along the [110] direction. This is explained by the compressive strain induced by the SiGe S/Ds which strengthens the light holes of the highest valence bands by pushing heavy holes subbands down. The subthreshold slope SS<sub>sat</sub> and the impact of W and L<sub>G</sub> on the DIBL are shown in Figs. 17, 18 and 19. These results indicate that well-controlled SCE are achieved down to L<sub>G</sub>=25 nm. Finally, **Fig. 20** show the transfer and output characteristics of stacked-NWs p-FET with L<sub>G</sub>=25 nm and W~30 nm. The device shows high performance in terms of SS<sub>sat</sub> (80 mV/dec), DIBL (50 mV/V) and  $I_{ON}$  current (400  $\mu$ A/ $\mu$ m at  $V_{DD}=0.9 \text{ V}$ ). The devices outperform the previous p-FET stacked-NW [3] due to the introduction of compressive strain.

#### V. CONCLUSION

Vertically stacked wires MOSFETs with inner spacers and SiGe:B S/D have been successfully fabricated for the first time with a RMG process. Precession electron diffraction has been used to provide accurate deformation maps at different process steps. The benefits of epitaxially regrown SiGe:B S/D junctions is clearly evidenced, with a significant compressive strain (~1%) injected in top and bottom Si p-channels. Finally, shortchannel performances of devices are discussed for different widths, gate lengths, and transport orientations. Through this work, two major challenges facing the development of stacked wires technology are addressed: inner spacers and strain engineering in 3D integration processes.

#### ACKNOWLEDGMENT

This work was partly funded by the French Public Authorities through the NANO 2017 program. It is also partially funded by the SUPERAID7 (grant N° 688101) project.

#### REFERENCES

- [1] T. Ernst et al., IEDM, 10.1109/IEDM.2006.346955, 2006.

- [2] L.K. Bera et al., IEDM, 10.1109/IEDM.2006.346841, 2006. [3] C. Dupré et al., IEDM, 10.1109/IEDM.2008.4796805, 2008.

- [4] E. Bernard et al., VLSI Technology, pp. 16-17, 2008. [5] E. Bernard et al., IEEE EDL, vol. 30, pp. 16-17, 2009.

- [6] I. Lauer et al., VLSI Technology, pp. T140-T141, 2015.

- [7] H. Mertens et al., VLSI Technology, pp. 158-159, 2016.

- [8] S.-D. Kim et al., S3S Conference, pp. 1-3, 2015.

- [9] L. Gaben et al., SSDM Conference, 2015.

- [10] D. Cooper et al., Nano Lett., vol. 15, pp. 5289-5294, 2015.

- [11] J. M. Hartmann et al., Thin Solid Films, vol. 520, p. 3185, 2012.

- [12] J. M. Hartmann et al., Solid State Electronics, vol. 83, p. 10, 2013.

- [13] S. Reboh et al., Appl. Phys. Lett. Mater., vol. 1, p. 042117, 2013.

- [14] A. Lubk et al., Ultramicroscopy, vol. 136, pp. 42-49, 2014.

Fig. 1. Process flow of stacked wires FETs. <u>Inner spacers and SiGe:B raised-S/D</u> are used. The Ge concentration in the SiGe layers is around 30%. <u>High density Fin patterning</u> (FP=40nm) is obtained by a <u>SIT process</u>. The steps numbered '1' to '5' are specific technical requirements for stacked wires FETs (as compared to FinFET devices).

Fig. 2. TEM images and EDX spectroscopy maps of (Si/SiGe) superlattices with (a)  $\times 3$  levels of tensile strained Si layers (for *n*-FETs) and (b)  $\times 3$  levels of compressive strained SiGe layers (for *p*-FETs) stacked upon one another.

Fig. 3. XRR profiles of (Si/Si<sub>0.7</sub>Ge<sub>0.3</sub>) multilayers. Well-defined thickness fringes are present up to high incidence angles, showing a smooth surface interfaces and allowing thicknesses measurements.

Fig. 4. Cross-sectional TEM images after etching of (Si/SiGe) fins in the longitudinal and transverse directions of futures Si (or SiGe) wires). Two types of fins patterning were used: (**Left**) single-Fin process and (**Right**) dense arrays of fins with a SIT process. Our SIT-based patterning technique yields <u>40 nm-pitch fins which are 60 nm high and 20 nm wide for both Si and SiGe channels</u>.

Fig. 5. Selective etching of SiGe layers. The Si and SiGe thicknesses are 7 nm and 8 nm, respectively. (**Top**) Cross-sectional SEM image showing the <u>etch depth profile</u> realized before the integration of inner spacers. (**Bottom**) <u>SiGe etch depth *versus*</u> time for 30% and 45% of Ge.

Fig. 6. Cross-sectional SEM images of stacked-NWs FETs prior to SiN inner spacers integration. The Si and SiGe thicknesses are 7 nm and 8 nm, respectively. The etching of SiGe layers stops at the same 'x' position than the spacer/poly-Si dummy gate interface.

Fig. 7. (**Left**) Cross-sectional <u>TEM images of stacked-NWs FET after the integration of inner spacers</u>. The Si and SiGe thicknesses are 12 nm. (**Right**) 3D SEM images of stacked-NWs FETs after the source-drain epitaxy (Si<sub>0.7</sub>Ge<sub>0.3</sub>:B for *p*-FETs and Si:P for *n*-FETs). Inner spacers are well-aligned and correctly dimensioned.

Fig. 8. (a) Cross-sectional TEM images and EDX maps of stacked wires FETs (HfO<sub>2</sub>, TiN and W gate stack). Wire widths above 20 nm are used to improve the effective width  $W_{eff}$  and then enhance the drive current. An  $\Omega$ -Gate Si channel is used for the bottom wire (b) to maintain a good electrostatic integrity. The deposition of high-k dielectrics (HfO<sub>2</sub>) and metals (TiN/W) is conformal.

Fig. 9. (**Top**) Out-of-plane ( $\varepsilon_{yy}$ ) and in-plane ( $\varepsilon_{xx}$ ) PED deformation maps of (SiGe/Si) superlattices (**on blanket wafers**). Here, the growth was made on a sSOI ( $\sim$ 1.4-GPa biaxial stress) substrate in order to have  $\times$ 3 tensile strained Si channels for n-FETs. (**Bottom**)  $\varepsilon_{yy}$  and  $\varepsilon_{xx}$  profiles extracted in our sample from experiment (TEM) and simulations (FEM).

Fig. 10. (**Left**) In-plane ( $\epsilon_{xx}$ ) PED deformation maps of a (SiGe/Si) superlattices (**after Fin patterning**). The (SiGe/Si) stack is similar to that in Fig. 9. A deformation of around 0.8% in the sSi layers ( $\times$ 3) is kept corresponding to a stress of 1.4GPa after Fins patterning. (**Right**) Deformation map and profiles for  $\epsilon_{zz}$ . Strain relaxation effects are observed in this direction due to free edges.

Fig. 11. HAADF STEM images of stacked-NWs p-FETs and deformation maps acquired by PED in the ( $\epsilon_{xx}$ ) and ( $\epsilon_{yy}$ ) directions. A spatial resolution of about 1.5 nm is achieved. Strain is measured **after Si (a)** and **Si<sub>0.7</sub>Ge<sub>0.3</sub>:B (b) S/D epitaxy**. For Si S/D, no strain is generated into Si p-channels. However, recessed and epitaxially regrown Si<sub>0.7</sub>Ge<sub>0.3</sub>:B S/D junctions clearly inject a significant amount of compressive strain in top and bottom Si p-channels. A compressive strain close to 1% (in blue color) is clearly visible.

Fig. 12. TCAD simulations showing the reduction of parasitic <u>gatesource/drain capacitances with inner spacers</u>.

Fig. 13. Gate capacitance *vs* V<sub>GS</sub> for stacked-NWs *p*-FETs with W=25-45nm. Here, L<sub>G</sub>=500nm.

Fig. 14. Ion vs V<sub>T,sat</sub> for stacked-NWs p-FETs with W=25-35nm at V<sub>DD</sub>=0.9V. 25nm<L<sub>G</sub><70nm.

Fig. 15.  $V_{T,sat}$  vs W for stacked-NWs p-FETs with L<sub>G</sub>=40nm at  $V_{DD}$ =0.9V.

Fig. 16. I<sub>ON</sub>/I<sub>OFF</sub> plot of [100] and [110] stacked-NWs *p*-FETs with W=20nm-30nm at V<sub>DD</sub>=0.9V.

Fig. 17. Subthreshold slope *vs* wire width (W) for stacked-NWs *p*-FETs with 25nm≤L<sub>G</sub>≤50nm.

Fig. 18. Median DIBL *vs* gate length (L<sub>G</sub>) for stacked-NWs *p*-FETs with W=20nm-30nm.

Fig. 19. Median DIBL *vs* nanowire width (W) for stacked-NWs *p*-FETs with L<sub>G</sub>=40nm.

Fig. 20.  $I_{DS}$ - $V_{GS}$  and  $I_{DS}$ - $V_{DS}$  characteristics of stacked-NWs p-FETs with  $L_G$ =25nm. Here, W~30nm.