# Analysis of preemption costs for the stack cache

Amine Naji, Sahar Abbaspour, Florian Brandner, Mathieu Jan

### ▶ To cite this version:

Amine Naji, Sahar Abbaspour, Florian Brandner, Mathieu Jan. Analysis of preemption costs for the stack cache. Real-Time Systems, 2018, 10.1007/s11241-018-9298-7. cea-01773654

# HAL Id: cea-01773654 https://cea.hal.science/cea-01773654

Submitted on 3 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Analysis of preemption costs for the stack cache

Amine Naji¹ · Sahar Abbaspour² · Florian Brandner³ · Mathieu Jan⁴

**Abstract** The design of tailored hardware has proven a successful strategy to reduce the timing analysis overhead for (hard) real-time systems. The stack cache is an example of such a design that was shown to provide good average-case performance, while remaining easy to analyze. So far, however, the analysis of the stack cache was limited to individual tasks, ignoring aspects related to multitasking. A major drawback of the original stack cache design is that, due to its simplicity, it cannot hold the data of multiple tasks at the same time. Consequently, the *entire* cache content needs to be *saved* and *restored* when a task is preempted. We propose (a) an analysis exploiting the simplicity of the stack cache to bound the overhead induced by task preemption,

This work is an extension of the paper "Efficient Context Switching for the Stack Cache: Implementation and Analysis" by Abbaspour et al. (2015). It was partially supported by a Grant (2014-0741D) from Digiteo France: "Profiling Metrics and Techniques for the Optimization of Real-Time Programs" (PM-TOP).

✓ Amine Naji amine.naji@ensta-paristech.fr

Sahar Abbaspour sabb@dtu.dk

Florian Brandner florian.brandner@telecom-paristech.fr

Mathieu Jan mathieu.jan@cea.fr

U2IS, ENSTA ParisTech, Université Paris-Saclay, Palaiseau Cedex, France

Department of Applied Mathematics and Computer Science, Technical University of Denmark, Lyngby, Denmark

<sup>3</sup> LTCI, Télécom ParisTech, Université Paris-Saclay, Paris, France

<sup>4</sup> Embedded Real Time Systems Laboratory, CEA, LIST, Saclay, France

(b) preemption mechanisms for the stack cache exploiting the previous analysis and, finally, (c) an extension of the design that allows to (partially) hide the overhead by *virtualizing* stack caches.

**Keywords** Program analysis · Stack cache · Cache-related preemption delays · Real-time systems

#### 1 Introduction

With the rising complexity of the underlying computer hardware, the analysis of the timing behavior of real-time software is becoming more and more complex and imprecise. Tailored computer architectures thus have been proposed based on existing hardware designs (Wilhelm et al. 2009) as well as newly designed hardware components (Schoeberl et al. 2011; Rochange et al. 2014). Due to its impact on performance the memory hierarchy received considerable attention, as shown by recent work of Reineke et al. (2011) and Metzla et al. (2011).

The stack cache of the Patmos processor exploits the regular structure in the access patterns to stack data (Abbaspour et al. 2013, 2014; Abbaspour and Brandner 2014). Functions often operate exclusively on their local variables, resulting in spatial and temporal locality of stack accesses following the nesting of function calls. The cache can be implemented using a circular buffer using two pointers: the memory top pointer MT and the stack top pointer ST. The ST points to the top element of the stack and data between ST and MT is present only in the cache. The remaining data above 1 MT is available only in main memory. In contrast to traditional caches, memory accesses are guaranteed hits. The time to access stack data thus is constant, simplifying Worst-Case Execution Time (WCET) analysis. The compiler (programmer) is responsible to enforce that all stack data is present in the cache when needed using three stack cache control instructions: reserve (sres), free (sfree), and ensure (sens). The worstcase (timing) behavior of these instructions only depends on the worst-case spilling and filling of sres and sens respectively, which can be bounded by computing the maximum and minimum cache occupancy (Jordan et al. 2013), i.e., the value of **MT**—**ST**. The cache's simple design thus reduces the analysis complexity considerably.

However, the simple structure of the stack cache also has drawbacks. One problem arises when multiple tasks are executed using preemptive scheduling. The two pointers only capture the cache state of the currently running task, the state of other (preempted) tasks is *lost* once ST and MT are overwritten. The data of preempted tasks might still be in the cache. However, the hardware *cannot* ensure that this data remains unmodified. Even worse, it cannot ensure that modified cache data, not yet written back to main memory, remains coherent. As a consequence the entire stack cache content has to be *saved* to main memory when a task is preempted. In addition, the stack cache content has to be *restored* before that task is resumed. This may induce considerable overhead that has to be accounted for during the analysis of a real-time system equipped with a stack cache.

<sup>&</sup>lt;sup>1</sup> We assume that the stack grows towards lower addresses.

The two main contributions of this work are: (1) a Stack Cache Analysis (SCA) technique to bound the overhead induced by the stack cache during preemption, i.e., *cache-related preemption delays* (Lee et al. 1998), and (2) three preemption mechanisms that allow to efficiently exploit the analysis information during context switching. In addition, we propose a hardware extension to *virtualize* several stack caches in a shared memory, which allows us to quickly switch between these virtual caches. The preemption overhead can partially be hidden through this extension. This furthermore opens promising opportunities to save/restore virtual caches of preempted tasks during the execution of other tasks.

This paper is structured as follows: Sect. 2 provides background related to the stack cache as well as static program analysis. In Sect. 3, we present our approach to analyze the cache-related preemption delays (CRPD) induced by the stack cache. Three different preemption mechanisms that are able to exploit the analysis information during context switching are proposed in Sect. 4. Section 5 is dedicated to virtual stack caches, their design and the possible scheduling opportunities that they open. The analysis, its relation to the proposed preemption mechanisms, and the virtual stack cache extension are evaluated in Sect. 6 before concluding.

### 2 Background

The stack cache is implemented as a ring buffer with two hardware registers holding pointers (Abbaspour et al. 2013): stack top (ST) and memory top (MT). The top of the stack is represented by ST, which points to the address of all stack data either stored in the cache or in main memory. MT points to the top element that is stored only in main memory. The stack grows towards lower addresses. The difference  $\mathbf{MT} - \mathbf{ST}$  represents the amount of occupied space in the stack cache. This notion of occupancy is crucial for the effective analysis of the stack cache behavior. Clearly, the occupancy cannot exceed the total size of the cache's memory |SC|. The stack cache thus has to respect the following invariants:

$$ST \leq MT$$

(1)

$$0 \le \mathbf{MT} - \mathbf{ST} \le |SC| \tag{2}$$

Data that is present in the cache is accessed using dedicated stack load (1ds) and stack store (sts) instructions. The frame-relative address (FA) of such a memory access is added to ST and the sum is used to index into the ring buffer, i.e., the address within the ring buffer is given by ( $\mathbf{FA} + \mathbf{ST}$ ) mod |SC|. Recall that the stack load and store instructions are always cache hits. The compiler (or programmer) thus has to ensure that accessed data actually is available in the cache using dedicated stack cache control instructions. More formally, it has to be ensured that  $\mathbf{FA} \leq (\mathbf{MT} - \mathbf{ST}) \leq |SC|$  before every stack cache access. Note that this can easily be realized in a compiler, as explained later.

**Stack cache operations** The stack cache control instructions manipulate the two stack pointers and initiate memory transfers to/from the cache from/to main memory, while preserving Eqs. 1 and 2. Memory transfers, and thus also the updates of

the various pointers, are performed at the granularity of cache blocks, which can be parameterized in size. Depending on the configured block size, the memory transfers might be misaligned with the transfer size of the underlying memory system (e.g., the burst size of DRAMs). For brevity we do not cover this issue here and refer to previous work (Abbaspour and Brandner 2014) covering techniques to handle alignment issues.

A brief summary of the memory transfers associated with each control instruction is given below, further details are available in Abbaspour et al. (2013):

Subtract k from ST. If this violates Eq. 2, i.e., the cache size is exceeded, a memory *spill* is initiated to decrement MT until

$\mathbf{MT} - \mathbf{ST} \leq |SC|$ . Cache blocks are then transferred to main memory.

**sfreek** Add k to ST. If this violates Eq. 1, MT is set to ST. Main memory is not accessed.

Ensure that the occupancy is larger than k. If this is not the case, a memory *fill* is initiated to increment MT until  $\mathbf{MT} - \mathbf{ST} \ge \mathbf{k}$ . Cache blocks are then transferred from main memory.

The stack load and store instructions only access the stack cache's ring buffer and thus exhibit constant execution times. This is particularly true for stack store instructions, which only modify the cached value. Modifications are not immediately propagated to the backing main memory. The stack cache's policy to handle stack store instructions thus resembles traditional *write back* caches.

**Lazy pointer (LP)** An extension of the original stack cache allows to track coherent cache data (Abbaspour et al. 2014). Similar to MT and ST, LP is a pointer (realized as a hardware register) that satisfies the following equation:

ST  $\leq$  LP  $\leq$  MT. The additional pointer divides the stack cache content into two parts: (1) cache data between ST and LP is potentially incoherent with the corresponding addresses in main memory, while (2) data between LP and MT is known to have the same value in the cache and in main memory—the data is known to be coherent. Coherent data can simply be excluded from memory spill operations, i.e., it can be treated as if the data were not in the cache. We thus can refine the notion of occupancy: LP — ST denotes the *effective occupancy* of a stack cache with a lazy pointer. Accounting for the effective occupancy allows to improve the sres instruction, with only slight modifications. The sfree instruction also requires minor modifications to correctly update the LP, while the sens instruction remains unchanged. In addition, the stack store instruction (sts) has to update LP whenever coherent date may be modified (Abbaspour et al. 2014), i.e., LP is pushed upwards to ensure FA+ST  $\leq$  LP.

Compiler support The compiler manages the stack frames of functions quite similar to other architectures with exception of the ensure instructions. For brevity, we assume a simplified placement of these instructions. Stack frames are allocated upon entering a function (sres) and freed immediately before returning (sfree). A function's stack frame might be (partially) evicted from the cache during calls. Ensure instructions (sens) are thus placed immediately after each call. The evicted data is consequently reloaded into the cache if needed after each call. We also restrict functions to only access their own stack frames. Data that is shared or too large can be allocated on a *shadow stack* outside the stack cache.

The restricted placement of the stack cache control instructions can be relaxed, which allows for varying frame sizes within functions in order to pass function arguments or for optimizations. The placement merely needs to be *well-formed* (Jordan et al. 2013), which means that each sres has to be followed by matching sfree instructions on all execution paths (similar to well-formed braces).

### 2.1 Static analysis

The worst-case behavior of the stack cache control instructions is determined using static program analysis techniques. Before going into the details of the analysis, we briefly summarize some basic notions of static analysis:

**Control-flow graph (CFG)** The CFG of a function is a directed graph G = (N, E, r, t). Nodes in N represent instructions and edges in E the execution flow. Nodes r and  $t \in N$  denote unique entry and exit points respectively. Additionally, we define  $Succs(n) = \{m \mid (n, m) \in E\}$ , the set of immediate successors of n.

**Call graph (CG)** The CG C = (F, A, s) is a directed graph, where nodes in F represent functions and  $s \in F$  the program's entry point. Edges in A are call sites, i.e., a call instruction in the CFG of the calling function. Each call is represented by a separate edge, calls via function pointers even by multiple edges.

**Weighted graph** A control-flow or call graph might be associated with a function W that assigns a weight in  $\mathbb{N}$  to each node and/or edge in the graph.

**Data-flow analysis (DFA)** A DFA is defined by a tuple  $A = (\mathcal{D}, T, \sqcap)$ , where  $\mathcal{D}$  is an abstract domain (e.g., values of stack pointers), transfer functions  $T_i : \mathcal{D} \to \mathcal{D}$  in T model the impact of individual instructions i on the domain, and  $\sqcap : \mathcal{D} \times \mathcal{D} \to \mathcal{D}$  is a join operator. Together with a CFG an instance of an (*intra-procedural*) DFA can be formed, yielding a set of data-flow equations. For simplicity, we specify these equations through functions IN(i) and OUT(i), which are associated with an instruction i and return values over  $\mathcal{D}$ . The equations are finally solved by iteratively applying these functions until a fixed-point is reached (Aho et al. 2006).

*Inter-procedural* analyses can be defined by additionally considering the call relations captured by the CG. In this case, additional data-flow equations are constructed modeling function calls end returns (Aho et al. 2006). Often these analyses are *context-sensitive*, i.e., the analyses distinguish between (bounded) chains of functions calls to define calling contexts.

#### 2.2 Stack cache analysis

As all memory accesses (lds/sts) through the stack cache are guaranteed hits, the timing behavior of the stack cache only depends on the amount of data spilled or filled by sres and sens instructions respectively. In the case of the standard stack cache this amount can be bounded by analyzing the cache's maximum/minimum occupancy (Jordan et al. 2013), i.e.,  $\mathbf{MT} - \mathbf{ST}$ , while for lazy spilling the effective occupancy (Abbaspour et al. 2014), i.e.,  $\mathbf{LP} - \mathbf{ST}$ , needs to be considered. We will only present the former approach in the following paragraphs. We refer to this as the standard stack cache analysis (SCA), which proceeds in three phases:

First, the maximum/minimum displacement is computed for each function. These values indicate the largest/smallest number of cache blocks reserved during the execution of a function (including nested calls). The displacement can be used to efficiently compute the occupancy across function calls, since it allows to bound the number of blocks evicted from the stack cache. Due to the placement of stack cache control instructions, the additional amount of stack space reserved at a given point in a function, w.r.t. the function entry, is constant. In our case, it simply corresponds to the value of the parameter k of the sres instruction of the enclosing function. The problem thus can be modeled as a longest/shortest path search on a weighted call graph, where the edge weight of each call site is given by the amount of stack space allocated by the calling function. The minimum displacement is then lower-bounded by the shortest path from a node to an artificial sink node. Likewise, the maximum displacement is upper-bounded by the longest path.

Next, the maximum filling at sens instructions is bounded using a function-local data-flow analysis that propagates the *maximum* displacement from call sites to the succeeding ensure instructions. In our case every call is immediately followed by an sens, rendering this analysis trivial. The maximum filling at an sens instruction can be bounded by computing the minimum number of cache blocks in the cache after the corresponding call instruction, i.e., the minimum occupancy. The minimum occupancy *after* the call has to be smaller than the occupancy before that call, since the called functions may only evict blocks from the cache. It cannot be lower than  $\max(0, |SC| - D(f))$ , where D(f) is the maximum displacement of the called function f and |SC| the stack cache size. If this bound is smaller than k, the argument of the sens, filling may occur. The maximum amount of filling can then be computed by subtracting the computed bound from k.

Finally, the worst-case occupancy is computed for each call site within a function using a function-local data-flow analysis. This is done by assuming a full stack cache at function entry. Subsequently, an upper bound of the occupancy is propagated to all call sites in the function, while considering the effect of other function calls and sens instructions. Function calls may evict stack data and thus lower the occupancy bound, depending on the minimum displacement of the called function (since the maximum occupancy after the call needs to be computed). The worst-case occupancy after a call cannot exceed max (0, |SC| - d(f)), where d(f) indicates the minimum displacement of the called function f and |SC| the stack cache size. Ensure instructions on the other hand may increase the bound through filling, i.e., the worst-case occupancy after an sens has to be larger or equal to k, the ensure's argument. The maximum spilling at sres instructions is finally computed by propagating occupancy values through the CG, such that the maximum occupancy at the entry of a function is derived from the minimum of either (1) the maximum occupancy at the entry of its callers plus the respective sizes of the callers' stack frames (k of their sres) or (2) the worst-case occupancy bound computed by the local data-flow analysis. The latter case allows us to consider spilling of other sres instructions that may reduce the occupancy before

<sup>&</sup>lt;sup>2</sup> This applies to the restricted placement from above as well as *well-formed* programs.

**Table 1** Summary of concepts used by the traditional stack cache analysis (SCA)

| Concept           | Description                                        | Analysis         |  |

|-------------------|----------------------------------------------------|------------------|--|

| Occupancy         | Number of cache blocks occupied in the stack cache | _                |  |

| Min. Displacement | Min. number of blocks evicted during function call | Shortest CG path |  |

| Max. Displacement | Max. number of blocks evicted during function call | Longest CG path  |  |

| Worst-case Occ.   | Local bound of max. Occ. assuming full stack cache | DFA+min. Disp.   |  |

| Max. Filling      | Min. occupancy before sens instructions            | DFA+max. Disp.   |  |

| Max. Spilling     | Max. occupancy before sres instructions            | CG+wc. Occ.      |  |

reaching a call site. Since the analysis operates on the call graph, fully context-sensitive spilling bounds can be computed efficiently for all functions in a program.

Table 1 summarizes the various concepts used by the traditional SCA in order to efficiently bound the maximum filling/spilling at sens and sres respectively.

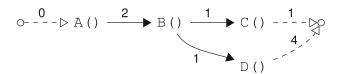

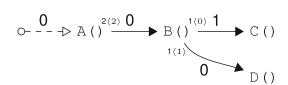

Example 1 Consider functions A, B, C, and D shown in Fig. 1 without preemption and a stack cache whose size is 4 blocks. First, the displacement computation is performed on the weighted call graph shown in Fig. 2. Function B, for instance, may call C or D. The maximum displacement thus has to account for the stack space reserved by B and by these two functions, which evaluates to either 2 = 1 + 1 (C) or 5 = 1 + 4 (D). For functions A, B, C, and D respectively the minimum/maximum displacement values evaluate to: 4/7, 2/5, 1/1, and 4/4. Then, the maximum filling of sens instructions is computed. Consider, for instance, the call from A to B  $(A_3)$ . Since the maximum displacement of B is 5, the minimum occupancy after the call evaluates to  $0 = \max(0, 4 - 5)$ . The corresponding sens instruction  $(A_4)$  consequently has to fill both of A's cache blocks (2-0), which is indicated by the bound in angle brackets (2). The displacement of C is only 1, which yields a minimum occupancy of  $3 = \max(0, 4 - 1)$  after instruction  $B_3$ . The stack cache is thus large enough to hold both stack frames of B and C and no filling is needed as indicated by the bound  $\langle 0 \rangle$  at instruction  $B_4$ . Next, the worst-case occupancy before call instructions is computed using a function-local data-flow analysis. The DFA determines that the worst-case occupancy before the call from B to D  $(B_5)$  is 3 = 4 - 1, due to the call from B to C. Before all other call instructions the worst-case occupancy is 4, since no other call may lower the maximum occupancy before reaching them. Finally, the maximum occupancy is propagated through the call graph, starting at the program's entry function A. The maximum occupancy at the entry of A consequently is 0. For the call from A to B  $(A_3)$  a maximum occupancy of 2 is computed as the minimum of the call's worst-case occupancy (4) and the maximum occupancy at the entry of A plus the size of A's stack frame (0+2). The maximum occupancy at the entry of D is similarly computed from the call's  $(B_5)$  worst-case occupancy (3) and the maximum occupancy at the entry of B plus the size of B's stack frame (2 + 1). Since the size of D's stack frame is equal to the stack cache size, all content of the stack cache has to be evicted by its reserve instruction. This results in a worst-case spilling of 3 blocks, as indicated by the bound (3) at instruction  $D_2$ . The bounds derived for the other sres and sens instructions are also indicated in angle brackets in Fig. 1.

| $(A_1)$ func $\mathbb{A}\left(  ight)$ | $(B_1)$ func ${	t B}$ ()            | $(C_1)$ func ${\tt C}$ ()           | $(D_1)$ func D()                    |

|----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $(A_2)$ sres 2 $\langle 0  angle$      | $(B_2)$ sres $1$ $\langle 0  angle$ | $(C_2)$ sres $1$ $\langle 0  angle$ | $(D_2)$ sres $4$ $\langle 3  angle$ |

| $(A_3)$ call $	exttt{B}$               | $(B_3)$ call $	exttt{C}$            | $(C_3)$ nop $m{\ell}$               | $(D_3)$ sfree $4$                   |

| $(A_4)$ sens $2$ $\langle 2  angle$    | $(B_4)$ sens $1$ $\langle 0  angle$ | $(C_4)$ sfree $1$                   |                                     |

| $(A_5)$ sfree $2$                      | $(B_5)$ call D                      |                                     |                                     |

|                                        | $(B_6)$ sens $1$ $\langle 1  angle$ |                                     |                                     |

|                                        | $(B_7)$ sfree $1$                   |                                     |                                     |

| (a)                                    | <b>(b)</b>                          | (c)                                 | (d)                                 |

**Fig. 1** Program consisting of 4 functions, reserving, freeing, and ensuring space on the stack cache (cache size: 4). The annotations in angle brackets, e.g.,  $\langle 2 \rangle$ , indicate the maximum filling/spilling behavior of stack cache control instructions. **a** code of A, **b** code of B, **c** code of C, **d** code of D

Fig. 2 A weighted call graph representing the program from Fig. 1. The edge weights indicate the amount of stack space reserved in the respective functions, and can be used to compute the minimum/maximum displacement

## 3 Analysis of preemption delays

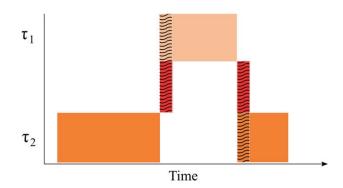

Preemptive multitasking provides better schedulability for real-time systems by allowing a running task to be preempted by another task having more critical timing requirements. Task preemption involves a *context switch*, which, with regard to the preempted task, consists of three steps: (1) *saving* the original task's execution context (registers, address space, device configurations,...), (2) running another task, and finally (3) *restoring* the original task's context. Since the traditional stack cache hardware cannot be shared by several tasks, the content of the stack cache has to be considered a part of the execution context and thus needs to be saved and restored as well. This may induce some overhead that has to be accounted for during schedulability analysis. For traditional caches (Lee et al. 1998) this overhead is known as CRPD. We will later formally define a static program analysis that allows us to bound this overhead for the stack cache for every program point where a preemption might occur. However, we will start first with a motivating example, illustrating the underlying problem:

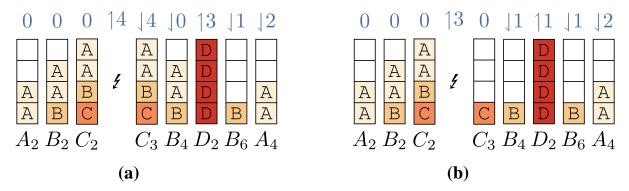

Example 2 Assume that a preemption occurs right before the sfree instruction  $C_3$  ( $\xi$ ) of the code in Fig. 1. The stack cache content then has to be saved and restored to/from main memory. A simple bound of the number of blocks that have to be transferred back and forth is given by the maximum occupancy provided by the SCA. In this example four blocks (of A, B, and C) need to be transferred, both, during context saving and restoration, as illustrated by Fig. 3a. This overhead can be reduced as illustrated by Fig. 3b. The stack data of C will be freed immediately after the preemption and thus is dead, i.e., the data can never be accessed after the preemption. This reduces the cost of context saving to a transfer of 3 cache blocks (of A and B) instead of 4. Also the context restoration costs are reduced. Actually, no cache block needs to be restored here. It thus suffices to re-reserve a single block on the stack cache for C's

Fig. 3 Cache states after executing the indicated instructions (below) and number of blocks transferred (above). a simple approach, b improved approach

dead stack data. The blocks of B are only accessed after returning from C. The sens  $B_4$  will automatically restore the necessary data. According to our initial SCA this instruction does not fill any block in the worst-case without preemption, i.e., an additional overhead to transfer B's cache block needs to be accounted for as preemption cost. The cache blocks of A are similarly restored by the corresponding sens  $A_4$ . This time, the restoration will not cause any additional costs, since the standard SCA already accounts for the filling of two cache blocks. At the same time, the occupancy before the next function call to D is reduced from 3 to 1, since only B's stack frame was actually restored. Consequently, the spilling of D's reserve instruction  $D_2$  is reduced. With preemption, actually fewer cache blocks are spilled than computed by the standard SCA—thus reducing the preemption costs. In comparison to the simple approach, transferring 14 cache blocks, the transfer costs only amount to 8 blocks.

This example illustrated that the number of cache blocks to save/restore can be reduced depending on the future use of the cached data. Our analysis, explained in the following subsections thus, is based on the notion of *liveness*—very similar to the concept of Useful Cache-Blocks (Lee et al. 1998).

Context saving analysis (CSA) Clearly, data that is present in the cache, but known to be coherent with the main memory (captured by the lazy pointer LP, see Abbaspour et al. 2014), can be excluded from context saving and thus reduce the preemption cost. Furthermore, some data might be excluded from saving depending on liveness, i.e., dead data that is not used in the future can be excluded. We will show how the analysis of dead and coherent data can be combined to reduce the number of blocks that need to be saved on a context switch.

Context restoring analysis (CRA) As for CSA, dead data can be excluded from context restoration. However, in many cases also live data can be excluded, e.g., when the data is spilled by an sres instruction before it is actually used or when an sens instruction would refill the data anyways. We will show that the underlying analysis problem is very similar to the liveness analysis required for CSA and, in particular, that the placement of sens instructions after calls simplifies the analysis problem.

### 3.1 Context saving analysis

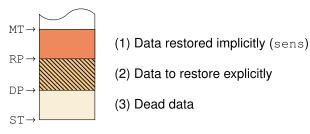

The worst-case timing of saving the stack cache's context depends on the number of cache blocks that have to be transferred to the main memory. In the simplest case, all

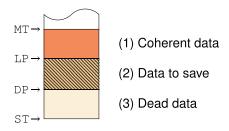

**Fig. 4** Partitioning of the stack: (1) coherent data above LP, (2) data that actually needs to be saved, and (3) dead data below DP

blocks potentially holding data need to be transferred, i.e., the maximum occupancy provided by SCA is a safe bound. However, not all data in the stack cache actually needs to be considered, as illustrated by the motivating example.

The lazy pointer (Abbaspour et al. 2014) readily allows to track coherent data that can be ignored during context saving, i.e., data known to have the same value in the cache and in main memory. Since the LP is implemented as a hardware register it can immediately be exploited by any context switching mechanism. Also the proposed analysis is immediately applicable and can be reused for the Context Saving Analysis. We thus do not provide details regarding the analysis here and simply assume that its results are available for the final cost computation of the CSA (see below).

Another class of data, that can be ignored during context saving, is dead data, i.e., data that will never be accessed by the program. Data in the stack cache may become dead starting from a given program point due to two reasons: (1) data that will be overwritten by an sts instruction (without an intermittent lds) in all executions or (2) data that is freed by an sfree (without an intermittent lds) in all executions. Inversely, data that is potentially used by a subsequent lds instruction has to be considered live.

Note that individual bytes on the stack cache might be live or dead depending on the actual usage of each individual byte, which would necessitate an analysis that is able to track individual bytes. However, due to the structure of typical stack frames generated by the compiler, we observe that dead data usually resides at the bottom of the stack, i.e., right above ST. The following analysis takes advantage of this fact in order to simplify the analysis complexity.

Inspired by the LP, we define a virtual pointer that allows us to track blocks of dead data residing right above ST. This virtual marker is only used by the analysis and is *not* realized as a hardware register. We call this virtual marker the *dead pointer* (DP):

**Definition 1** The dead pointer (DP) is a virtual marker tracking dead data, such that  $\mathbf{ST} \leq \mathbf{DP} \leq \mathbf{MT}$ . Data below DP is considered dead, while date above DP is potentially live.

The lazy pointer (LP) and the dead pointer (DP) define a partitioning of the stack cache's content into three distinct regions shown in Fig. 4. Data above LP is coherent and thus can be ignored during context saving. Similarly, data below DP is known to be dead and can safely be ignored. Only the remaining data, between DP and LP, actually needs to be transferred to main memory. Note that this model only allows to detect dead data at the bottom of the stack cache—which we observed to be the usual case in the code generated by the compiler. The obtained results are thus a conservative approximation, i.e., more dead data might actually be present in the cache, which is not detected by the analysis and thus cannot be exploited. Likewise, more coherent

data might be present below the position of the LP determined by the analysis. Both of these cases may lead to an over-estimation of the worst-case cost determined by the CSA, but do not compromise the analysis' correctness. Also note that this approach simplifies the actual context saving, since only a contiguous block of data needs to be transferred.

The analysis of the DP is based on a typical *backward* liveness analysis, i.e., a value is said to be live when it is used by a subsequent load (lds) and is considered dead immediately before a store (sts), or, in the case of the stack cache, an sfree. As for the traditional SCA, only the relative position of the DP with regard to ST needs to be known, which further simplifies the CSA. Our analysis is a function-local, backward data-flow analysis, conservatively tracking the lowest possible position of the DP relative to ST, i.e., for each program point the minimum value  $\min(\mathbf{DP} - \mathbf{ST})$  is computed over all possible executions of the analyzed program. This ensures that the analysis is conservative and only considers the least amount of dead data actually in the cache for the cost computation.

As indicated above, only three kinds of instructions may modify the position of the DP. Whenever an 1ds is encountered, it must be ensured that DP is below its framerelative address FA starting from ST, i.e.,  $\mathbf{DP} \leq \mathbf{FA}$ , since the value loaded by the instruction is known to be live. Recall that the analysis proceeds in a backward fashion, so the loaded value is live at all program points before the lds, up to a preceding sts instructions potentially overwriting the same FA. An sts, on the other hand, might push the DP upward as the overwritten data is dead immediately before the store. This is only possible when the analysis is able to show that the newly discovered dead data is right above the contiguous block of dead data, such that a new contiguous block can be formed. The sts overwrites data at a given FA in the cache, the overwritten value thus can no longer be accessed and is dead at all program points before the store instruction, up to a join (conditional branch) and/or an 1ds instruction potentially rendering the data live. Finally, with regard to a function, all its data is dead immediately before its sfree, since none of the data in the stack frame can be accessed from this point on. The DP then is at its highest possible position, i.e., the stack frame's size k. In addition to these three instructions that may directly have an impact on the DP, the analysis also needs to consider conditional branches, i.e., instructions that may have multiple successors in the CFG. Since the analysis proceeds backward, the successor's DP values might be different. The analysis thus needs to apply a join operator (Sect. 2), which selects a conservative approximation. In the case of CSA, the minimum, i.e., the least amount of dead data, is considered.

The following data-flow equations specify how individual instructions (Eq. 3) and joins (Eq. 4) may modify the relative position of the DP with regard to the stack frame of a function:

$$OUT(i) = \begin{cases} k & \text{if } i = \texttt{sfree} \ k \\ \min(IN(i), \texttt{FA}) & \text{if } i = \texttt{lds} \ \texttt{FA} \\ IN(i) + 1 & \text{if } i = \texttt{sts} \ \texttt{FA} \land \texttt{FA} = IN(i) \\ IN(i) & \text{otherwise} \end{cases}$$

$$IN(i) = \begin{cases} 0 & \text{if } i = t \\ \min_{s \in Succs(i)}(OUT(s)) & \text{otherwise} \end{cases}$$

(4)

$$IN(i) = \begin{cases} 0 & \text{if } i = t \\ \min_{s \in Succs(i)}(OUT(s)) & \text{otherwise} \end{cases}$$

(4)

The position of the DP before (and after) each instruction in the function can then be computed by applying these equations iteratively until a fixed-point is reached. The initial values assigned to IN(i) and OUT(i) for each instruction i have to be chosen such that the iterative processing actually converges and delivers a safe approximation. The above data-flow equations compute the lowest position of the DP, it thus suffices to initialize the equations with the size of the stack cache |SC| or the size of the current stack frame k - both are upper bounds on the maximum value of DP. The initialization of IN(t) to 0, where t represents the function's exit point, along with the use of the minimum as the join operator ensures that the analysis converges towards the minimum value of the DP and consequently gives a safe approximation.

Assuming a unit cost  $\hat{c}_s$  to transfer a cache block to main memory, the overhead induced by context saving before an instruction i depends on the size of the coherent area CA(i) (derived from the LP Abbaspour et al. 2014), the size of the dead area DA(i) (given by Eq. 3), and the maximum occupancy Occ(i):

$$savingCost(i) = \widehat{c}_s \max(0, Occ(i) - CA(i) - DA(i))$$

(5)

Note that the size of the coherent data as well as the maximum occupancy are potentially calling-context dependent, i.e., might change with the nesting of surrounding function calls. This is readily supported by the respective analyses and can easily be considered in the above equations. The costs would then, of course, also be contextdependent.

It would, in addition, be possible to consider the calling-context when analyzing the dead area (DA(i)). Whenever all data in a function's stack frame is dead, the size of its caller's dead area can be added to DA(i). However, this is rarely beneficial in practice, since all functions, except leaf functions not calling other functions, store the return address on the stack. Details on inter-procedural analysis are thus omitted.

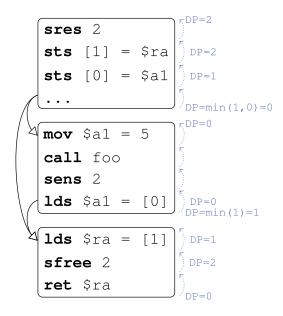

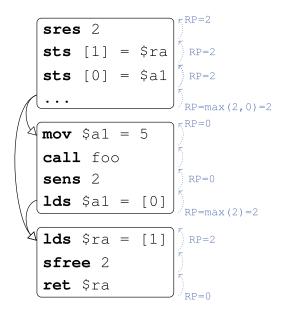

Example 3 Consider the CFG of the function shown in Fig. 5, which consists of three blocks of straight-line code. The sequence of the top most block is assumed to end with a conditional branch having the two other blocks as successors (indicated by the edges on the left). The goal of the analysis is to track the area  $\mathbf{DP} - \mathbf{ST}$  of data that is known to be dead by computing the lowest possible position of DP at each program point. The analysis processes the CFG backwards, starting at the return instruction ret at the bottom. The computation of the analysis and its results are indicated in blue to the right of the code. Since the return is the last instruction in the function, the DP is initialized to 0. All stack data is potentially live here. The DP value is then propagated to its predecessor the **sfree** instruction. All stack data is known to be dead right before this instruction, the DP is thus set to 2, the instruction's argument (k).

Fig. 5 Propagation of the DP (shown on the right in blue) within a function: stack data becomes dead right before sfree and sts instructions, while it becomes live before 1ds instructions. Other instructions do not impact the DP (Color figure online)

Next, the **lds** instruction is processed. The top most stack element of the function's stack frame is accessed (using the frame-relative address [1]) and thus becomes live, which is indicated by the new DP value of 1. The second load ([0]) in the block above is processed similarly. Here the DP drops to 0, indicating that both stack elements are live. The remaining instructions (**mov**, **call**, **sens**) in the same block have no effect on liveness. The last instruction of the top-most block has 2 successors with different DP values (1 and 0). The join operator conservatively takes the minimum to safely overapproximate the actually live stack data. The algorithm eventually processes the store instructions at the top. The first **sts** ([0]) overwrites the first stack element, whose value becomes dead. The DP thus is incremented to its new value 1. The subsequent **sts** ([1]) then overwrites the top element, rendering all stack data dead (**DP** = 2). Note, that instructions before the **sres**/after the **sfree** conceptually belong to the caller.

## 3.2 Context restoring analysis

Similar to context saving, the time required to restore a task's stack cache context depends on the number of cache blocks that need to be transferred from main memory to the cache. A simple solution would again be to transfer all the blocks potentially holding data, which is again bounded by the maximum occupancy.

However, as shown in Example 2, not all cache blocks have to be restored. We can distinguish the following cases, as illustrated by Fig. 6: (1) cache blocks containing dead data only (given by Eqs. 3 and 4), (2) blocks potentially containing live data that have to be restored, and (3) blocks that are restored by a subsequent sens. Since only a subset of the cache blocks are restored the occupancy after a preemption is usually reduced. This may reduce the spill costs of subsequent sres instructions. The analysis thus has to consider another case: (4) potential gains due to reduced spilling. Case (1) and (2) can be handled by function-local analyses explained in Sect. 3.2.1, while case (3) and (4) require inter-procedural analyses covered in Sects. 3.2.2 and 3.2.3.

**Fig. 6** Partitioning of the stack: (1) data restored by sens of the current as well as other functions, (2) data to restore, and (3) dead data

### 3.2.1 Local restore analyses

Dead data can simply be excluded from the memory transfer as explained in the previous subsection. However, in contrast to context saving where dead data is simply discarded, space has to be allocated on the stack cache in order to guarantee that subsequent memory accesses (stores in particular) succeed. The allocation is only needed when dead data exists, i.e., DA(i) is non-zero. Even then, the operation only requires an update of MT, which can be performed in constant time ( $\widehat{c}_a$ ):

$$allocationCost(i) = \begin{cases} \widehat{c}_a \text{ if DA}(i) \neq 0\\ 0 \text{ otherwise} \end{cases}$$

(6)

Blocks containing live data have to be restored and thus transferred back from main memory. This can be done explicitly during the context restoration or implicitly by an sens instruction executed later by the program. While the explicit transfer always induces additional overhead that needs to be accounted for, the implicit restoration might be for free. This happens when the maximum filling computed by the traditional SCA for the sens instruction is non-zero. The overhead associated with the explicit restoration is then, at least partially, accounted for in the program's WCET.

In order to account for the overhead of implicit and explicit transfers two quantities have to be determined: (1) the amount of data that needs to be restored explicitly and (2) the cost of implicit memory transfers performed by sens instructions. We introduce another virtual marker to model the former quantity. This pointer represents an over-approximation of the amount of *live* data in the stack cache that is *not* implicitly restored by an sens instruction before a subsequent access rendering the data live:

**Definition 2** The restore pointer (RP) is a virtual marker tracking potentially live data in the stack cache, i.e.,  $ST \le RP \le MT$ . Data below the RP is potentially live and *not* guaranteed to be restored by a subsequent sens instruction.

An interesting observation is that sens instructions are placed after every function call and that functions are assumed to only access their own stack frames. This simplifies context restoration, since only stack data of the function where the preemption occurred has to be restored. The stack frames of the calling functions are then automatically restored by their respective sens. The computation of the associated overhead is explained in Sect. 3.2.2.

The analysis of the RP is a function-local, *backward* analysis that tracks the highest possible position of the pointer relative to ST (i.e.,  $\mathbf{RP} - \mathbf{ST}$ ), which means that an over-approximation needs to be computed. The position of the RP depends on the

amount of data restored implicitly as well as the amount of live data. The analysis thus needs to consider the impact of sens instructions, which lower the position of the RP, as well as memory accesses, which may increment the RP. Whenever an sens instruction is encountered by the analysis the position of the RP is set to 0, which simply means that no data needs to be restored in case of a preemption that occurs immediately before that ensure (recall that the analysis proceeds backward). The sens simply reloads the entire stack frame when the task gets resumed. Data becomes live whenever it is accessed by an 1ds instruction, the position of the RP thus has to be larger or equal to the FA of any load instruction encountered. In order to simplify the handling of dead data, lds and sts instructions are both considered to increment the RP – despite the fact that stores do not actually render the data live. Dead data is excluded from explicit and implicit transfers anyways using the DP (as indicated above). Also note that there is no strict ordering between the DP and the RP, i.e., it might happen that DP > RP. This usually happens when dead data is present at an sens instruction, which sets the RP to 0, but has no impact on the DP. In addition to the instructions that have an immediate impact on the RP the analysis also needs to account for control-flow joins at conditional branches, which may have multiple successors with diverging RP values. The analysis always selects the maximum value and propagates this information upwards in order to ensure that the position of the RP is safely over-approximated. The following equations capture the evolution of the RP relative to ST:

$$OUT_{RP}(i) = \begin{cases} 0 & \text{if } i = \text{sens k} \\ \max(IN_{RP}(i), \text{FA}) & \text{if } i = \text{lds FA} \lor i = \text{sts FA} \\ IN_{RP}(i) & \text{otherwise} \end{cases}$$

$$IN_{RP}(i) = \begin{cases} 0 & \text{if } i = t, \\ \max_{s \in Succs(i)}(OUT_{RP}(s)) & \text{otherwise} \end{cases}$$

(8)

$$IN_{RP}(i) = \begin{cases} 0 & \text{if } i = t, \\ \max_{s \in Succs(i)}(OUT_{RP}(s)) & \text{otherwise} \end{cases}$$

(8)

Assuming unit costs  $\hat{c}_r$  to transfer a cache block from main memory, the cost of restoring the live data of the stack cache depends on the size of the dead area (DA(i),Eq. 3) and the size of the restore area (RA(i), Eq. 7):

$$transferCost(i) = \widehat{c}_r \max(0, RA(i) - DA(i))$$

(9)

Example 4 Figure 7 illustrates the propagation of the RP through the CFG from the previous example. The processing again starts at the bottom of the CFG at the return instruction. At this point all data is dead ( $\mathbf{RP} = 0$ ) and thus does not need to be restored explicitly. This changes when the first 1ds instruction ([1]) is encountered, which renders the top-most element of the stack frame and all elements below it live. This is indicated by the new RP value of 2. The RP does not change until the **sens** instruction is processed. At this point all the stack frame's data is known to be live. However, the sens instruction ensures that all stack data is filled into the cache. Thus no explicit restoration is required and the new value of RP becomes 0. The other instructions in the block above the sens do not have an impact on the RP. As before, the last instruction of the top-most block is assumed to be a conditional branch with two

**Fig. 7** Propagation of the RP (shown on the right in blue) within a function: only lds, sts, and sens instructions impact the RP, while other instructions do not modify its value value (Color figure online)

successors having different RP values. This time, the maximum value 2 is propagated upwards in order to conservatively over-approximate the amount of potentially live data. The subsequently processed instructions do not have an impact on the RP since it is already at the maximum position (2), which would indicate that the entire stack frame needs to be restored explicitly. However, since the DP was shown to be non-zero (see Example 3), the stack frame only needs to be restored partially.

It remains to account for the implicit transfer costs at sens instructions in the current function that are not already included in the program's WCET. This situation arises whenever the RP pointer is *not* at its maximum position (the size of the function's stack frame k). The function's stack frame is thus only partially restored by the explicit transfer after a preemption and some additional cache blocks need to be filled from main memory implicitly by the next sens instruction. The additional cost of this transfer depends on the size of the function's stack frame, the size of the restore area (RA(i)) from above), and the number of cache blocks that need to be transferred by the sens instruction for a regular execution without preemption, which is provided by the standard SCA in the form of an annotation to the instruction  $(\langle b \rangle)$ . The overhead is trivially upper-bounded by the function's stack frame size k. A more precise bound would be  $\mathbf{k} - \mathrm{RA}(i)$ , which reflects the reduction of the cost of the implicit transfer cost by deducting the explicitly transferred blocks. Another bound can be derived from the maximum filling bound b associated with an sens instruction. The additional costs due to the implicit restoration cannot exceed  $\mathbf{k} - b$ , which represents the maximum number of cache blocks whose transfer costs are not accounted for in the program's WCET.

The following cost function combines both of the above approaches. However, before the cost function can be defined, an intermediate step has to be performed, which propagates the maximum filling bounds associated with individual sens instructions to all program points throughout the function. This allows to determine for each instruction, also those that are not an sens, the number of cache blocks that are potentially filled by any subsequent sens instruction. This intermediate step can be implemented using a function-local, *backward* DFA, propagating the difference

between the sens's argument k and its filling bound (b) (obtained from the standard SCA) upwards through the CFG:

$$OUT_{FL}(i) = \begin{cases} \mathbf{k} - \mathbf{b} & \text{if } i = \mathbf{sens} \, \mathbf{k} \, \langle \mathbf{b} \rangle \\ IN_{FL}(i) & \text{otherwise} \end{cases}$$

(10)

$$OUT_{FL}(i) = \begin{cases} \mathbf{k} - \mathbf{b} & \text{if } i = \mathbf{sens} \ \mathbf{k} \ \langle \mathbf{b} \rangle \\ IN_{FL}(i) & \text{otherwise} \end{cases}$$

$$IN_{FL}(i) = \begin{cases} 0 & \text{if } i = t, \\ \max_{s \in Succs(i)}(OUT_{FL}(s)) & \text{otherwise} \end{cases}$$

(10)

The overhead caused by implicit memory transfers of sens instructions can then be computed from the number of cache blocks that are filled implicitly (FL(i), Eq. 10) and the number of blocks that were explicitly restored, i.e., the size of the restore area (RA(i), Eq. 7):

$$ensureCostLocal(i) = \widehat{c}_r \max(0, FL(i) - RA(i))$$

(12)

As for the analysis of the DP before, the above data-flow equations for the RP and the local filling need to be initialized properly in order to ensure that the fixed-point computation converges. Since both analyses define the join operator as the maximum over all successors, the equations have to be initialized to 0 before the resolution process starts. In the case of the RP analysis this indicates that no data needs to be restored explicitly after the function's sfree. The first access to stack data encountered by the analysis will then increment the RP value accordingly. The iterative processing then ensures that the analysis converges towards a safe upper bound. A similar argument applies to the propagation of the local filling bounds. The equations also contain an explicit initialization to 0 for the function's exit point t. This initialization is, in fact, redundant, given the fact that t cannot have any successors and that all data-flow equations are initialized to 0 anyways.

#### 3.2.2 Global ensure analysis

The analyses in the previous subsections exclusively focus on the state of the stack frame of a single function and account for additional costs related to the restoration of the stack frame of the function whose execution was interrupted by a preemption. The stack frames of other functions that are currently on the call stack are not explicitly restored. This is done via implicit memory transfers, which are performed by the sens instructions that are placed after every function call. The underlying idea is very similar to the local reserve analysis discussed before, with the main difference that no explicit memory transfer is performed whatsoever.

To analyze the costs associated with these implicit memory transfers, an overapproximation needs to be computed that considers all possible states of the call stack, i.e., all possible chains of nested function calls leading up to a call to the function under analysis. This is sufficient, since the additional overhead is only induced by the sens instructions that are executed upon returning from functions along the call stack. The program's call graph (CG) is a well-known representation capturing all chains of nested function calls that may occur during the execution of the program (see Sect. 2).

**Fig. 8** Weighted CG of the code in Fig. 1 used to bound the additional transfer costs at sens instructions of other functions

Each such chain observed during the execution of the program corresponds to a path in the call graph starting at the program's entry point (typically the main function) and leading to the graph node representing the current function. In order to compute the desired over-approximation, the analysis thus needs to consider all paths leading to the currently considered function and associate a cost with each path.

We model this problem as a longest path search on a weighted CG, considering all paths from the program's entry node to the current function. The edge weights in the graph are the number of blocks that are *not* filled by the sens associated with the corresponding call site, which is given by FL(i) (Eq. 11) of the site's call instruction. Note that this problem is very similar to the computation of the maximum displacement of the original SCA (Abbaspour et al. 2013). However, the length of the path is bounded: (1) by the maximum occupancy at the call site (which is itself bounded by the stack cache size) and (2) by the minimum amount of stack data remaining in the stack cache after returning from the function, i.e.,  $\max(0, |SC| - D(f))$ , where |SC| denotes the stack cache size and D(f) the function's maximum displacement. The latter case is particularly interesting, since no computation is required when the function's displacement is larger than or equal to the stack cache size. The length of the path and the restoration costs then simply become 0. Also note that the global ensure costs are always the same, independent of where the program is interrupted in the function. It is thus sufficient to pre-compute the costs only once for each function.

Our algorithm thus pre-computes the global ensure costs as follows. A weighted call graph is constructed beforehand, where the edge weights are provided by the local ensure analysis (Eq. 11). The algorithm then processes each function f separately. First, it is verified whether the maximum displacement D(f) of f exceeds the stack cache size. If this is the case, the global ensure costs are bounded by 0, and the algorithm simply proceeds with the next function. Otherwise, an integer linear program (ILP) is constructed, which is similarly structured as the traditional IPET approach (Li and Malik 1995). The ILP encodes all paths originating at the root node of the CG leading to the current function, such that the objective function represents the length of the path. An ILP solver then computes the longest such path, by maximizing the objective function. Note that this approach allows to handle any kind of program, including those with recursion. The original work on the SCA includes a detailed description on the handling of recursion (Abbaspour et al. 2013). Note that for programs without recursion the longest path for all functions can be computed in linear time using dynamic programming (Cormen et al. 2009). Given the length FLG(f) of such a path for function f, the costs induced at other functions is:

$$ensureCost(f) = \widehat{c}_r FLG(f)$$

(13)

Example 5 Consider the code from the initial example in Fig. 1. The algorithm begins by constructing a weighted call graph as shown in Fig. 8. Apart from the edge weight that is shown in the middle of each edge, the figure also indicates the information provided by the local ensure analysis at the respective call site. The numbers at the origin of each edge represent the argument k of the next ensure instruction following the call site as well as its filling bound in angle brackets. The edge weight simply correspond to the difference between these two values.

The edge weight for the call from B to C, for instance, evaluates to 1, since the corresponding ensure instruction may transfer an additional block, which is not accounted for by its original bound  $\langle 0 \rangle$  (1 – 0 = 1). Similarly, the edge weight of the call from A to B evaluates to 0. The corresponding sens transfers up to 2 blocks, of which both are already accounted for by the bound  $\langle 2 \rangle$  (2 – 2 = 0).

For C the longest path has a length of 1, since an additional block needs to be transferred if a preemption were to happen during the execution of C. The longest path from the program's entry to function  $\mathbf{D}$  has length 0, i.e., all cache blocks of calling functions are restored for free as they are accounted for by the original bounds. The same result could have been computed from  $\mathbf{D}$ 's maximum displacement (4), which is equal to the cache size (4).

### 3.2.3 Global reserve analysis

Lazily restoring the stack cache content not only allows us to avoid explicit memory transfers during context switches, but it may also turn out to be profitable. Even in the worst-case only the stack frame of the current function is restored, which leaves the remaining space in the stack cache free and thus effectively reduces the stack cache's occupancy. This may be beneficial for subsequent sres instructions, since the reduced occupancy may also reduce the maximum spilling. This, consequently, may reduce the running time of the program under analysis. There are two scenarios where such a gain might be observed: (1) at an sres of another function that is called from the current function and (2) at an sres of another function that is called after returning from the current function. It is important to note here, that multiple sres instructions may profit from the reduced occupancy, i.e., when several calls are nested or are performed in sequence with increasing displacement values. The analysis thus needs to be able to accumulate gains of multiple function calls, while providing a conservative under-estimation of the actual gains. We will initially focus on the first scenario and limit our attention to a single function call, and later extend this solution in order to handle the accumulation of gains as well as gains from the second scenario.

Recall that the WCET of the program under analysis already includes an estimate of the maximum spilling at sres instructions, which is computed for each function individually from the maximum occupancy before entering the function and the amount of stack space (k) reserved by the function's sres. This can be generalized to several nested function calls by considering the displacement at the outer-most function call. The maximum spilling performed by all called functions can then be bounded by considering the maximum occupancy along with the maximum displacement of the minimum occupancy along with the minimum displacement. Consequently, a conser-

vative estimation of the minimum gain can be computed by comparing the minimum spilling of a normal execution with the minimum spilling after a preemption. More formally, given a call instruction i with a minimum occupancy mOcc(i) and a minimum displacement d(i) the minimum spilling during a normal execution is given by:

$$minSpill(i) = \max(0, \operatorname{mOcc}(i) + d(i) - |SC|)$$

(14)

The minimum spilling with preemption is computed in a very similar way. However, the minimum occupancy is lower due to the lazy restoration of the stack cache's content. A simple bound of the minimum occupancy, that is sufficiently precise in practice, is the size of the current function's stack frame, i.e., the argument of the current function's stack cache control instructions k:

$$minSpillPr(i) = \max(0, \mathbf{k} + d(i) - |SC|)$$

(15)

The minimum gain from the reduced spilling at a call site i is then given by:

$$siteGain(i) = max(0, minSpill(i) - minSpillPr(i))$$

(16)

A simple solution to account for the impact of the *next* function call is to propagate the gain at call sites backward through the CFG. The following equations determine the minimal gain that is guaranteed to occur for only one of the subsequent function calls. At joins, the equations select the minimum, while the maximum is selected on straight line code:

$$OUT_{GN}(i) = \begin{cases} max(IN_{GN}(i), siteGain(i)) & \text{if } i = \textbf{call} \\ IN_{GN}(i) & \text{otherwise} \end{cases}$$

(17)

$$OUT_{GN}(i) = \begin{cases} \max(IN_{GN}(i), siteGain(i)) & \text{if } i = \textbf{call} \\ IN_{GN}(i) & \text{otherwise} \end{cases}$$

$$IN_{GN}(i) = \begin{cases} 0 & \text{if } i = t, \\ \min_{s \in Succs(i)}(OUT_{GN}(s)) & \text{otherwise} \end{cases}$$

$$(17)$$

As before, the data-flow equations have to be initialized in order to ensure that the analysis converges. The equations have to be initialized to the maximum possible gain, i.e., |SC|, the size of the stack cache, except for the function's exit node t. Since, at this moment, the analysis only considers local gains due to calls from within the current function, the gain at the end of the function evaluates to 0 for t (Eq. 18). The analysis converges towards a minimum gain, despite the fact that on straight-line code the maximum value is propagated (which initially indeed is |SC|). This is ensured by the initialization of t (0) and the fact that the minimum value is selected at joins (Eq. 18). The analysis thus will eventually reevaluate the data-flow equations of all program points reachable in the reversed CFG from the function's exit node t and converge towards a minimum.

Since we initially did not expect considerable returns from this analysis, our initial publication (Abbaspour et al. 2015) adopted this simple approach only without developing it further. Though simple to compute, this solution is conservative. The gain of subsequent calls can, in fact, be accumulated since the occupancy remains lower than in a regular execution even after returning from the called functions. Unfortunately,

this accumulation of costs cannot directly be encoded using data-flow equations. The accumulated costs in cyclic regions of the CFG would grow infinitely and thus yield wrong results.

Since then, we noticed that the underlying problem can, in fact, be seen as a shortest path problem on a weighted CFG. The edge weights in the graph represent the gain associated with individual call sites (Eq. 16), while the length of the shortest path from an instruction i to the CFG's sink node t represents the accumulation of gains for all of the visited call sites. This is possible since every call site is uniquely identified even if some function is called many times in some execution path. However, the analysis has to make sure that the gain of visited call sites is not accumulated more than once. Fortunately, this cannot occur since the only way to revisit the same call site again would be in a loop. Such a scenario is naturally avoided by the shortest path search algorithm, since revisiting the same call site would increase the path length. Given the length LSG(i) of the shortest path for instruction i, it is now possible to account for the actual gain associated with all function calls possibly executed within the current function after a preemption at i:

$$reserveGainLocal(i) = \widehat{c}_s LSG(i)$$

(19)

Note that the length of the path, and thus the local gain, is bounded. The gain can never exceed  $|SC| - \mathbf{k}$ , since the lazy restoration may in the worst-case only reload the local stack frame, whose size is given by k. This can also be seen by assuming that the minimum occupancy (mOcc(i) in Eq. 14) evaluates to |SC|. Simplifying the formulas (cf. Eq. 15 and 16) yields the same result. This bound holds for nested function calls and sequences of function calls. The nesting of function calls is conservatively modeled using the minimum displacement (d(i)) in the formulas. The effects of function calls that are performed in sequence are conservatively modeled by considering the minimum occupancy, provided by the standard SCA. Recall that the minimum occupancy can be bounded locally by considering the impact of function calls through their maximum displacement (see Sect. 2). The gain of each function call in a sequence thus is reduced by preceding calls due to the reduced minimum occupancy, which immediately depends on the calls' maximum displacements. The accumulated local gain thus cannot exceed the aforementioned bound since the gain gradually approaches 0 due to the interplay between minimum occupancy and maximum displacement of intermittent calls.

Example 6 The gain due to the reduced spilling at the function entry of B needs to be analyzed, right after its reserve instruction  $B_2$ . The function first calls C, whose minimum occupancy, provided by the standard SCA, evaluates to 3, while its displacement evaluates to 1. Spilling will never occur while executing C, since the stack frames of A, B, and C fit into the stack cache (2+1+1=3+1<=4). The local reserve gain associated with the respective call site thus is 0. Likewise, the minimum occupancy before the call to D is 3, its displacement, however, is 4. The sres instruction  $D_1$  consequently spills 3 blocks (3+4-4) during a regular execution (Eq. 14), while only a single block (1+4-4) is spilled after a preemption (Eq. 15). The call site is thus associated with a weight of 2 (3-1). Since both calls are executed in any case,

Fig. 9 Weighted CG of the code in Fig. 1 used to bound the global gain due to sres instructions of other functions

$$0 \longrightarrow B() \xrightarrow{0} B() \xrightarrow{2} C()$$

the length of the shortest path from the preemption point to the end of B evaluates to 2 (cf. Eq. 19).

The previous analysis only accounts for the gain due to function calls within the current function. In addition, it is also possible to account for potential gains after returning from the current function. Recall that the stack frames of all functions currently on the call stack are lazily restored. The occupancy after a preemption may thus also be lower for these functions compared to a regular execution without preemption. Similar to the computation of the global ensure costs, we can account for this gain through a path search on a weighted CG. The edge weights for this graph are given by the local reserve gain (Eq. 19) at the respective call sites.

The minimal gain that is guaranteed to occur for all executions has to be computed. The algorithm thus has to search for the shortest path in the CG instead of the longest. Given the length GSG(f) of the path for function f, the global gain due to sres instructions is given by:

$$reserveGain(f) = \widehat{c}_s GSG(f)$$

(20)

An interesting observation at this point is that the global reserve gain is bounded just as the local reserve gain before. As the analysis climbs upwards through the call graph (towards the program's entry function), the displacement of the functions increases. With this increase the potential gain of subsequent function calls diminishes (as before), limiting the global reserve gain to the minimum of either the minimum occupancy at the function's entry or  $|SC|-\mathbf{k}$ , where k represents the current function's stack frame size.

Example 7 Consider the code from the initial example in Fig. 1. The algorithm begins by constructing a weighted call graph as shown in Fig. 9. The edge weights correspond to the local gain associated with each call site, given by Eq. 19. For the call from B to C, for instance, the edge weight evaluates to 2. This is because a preemption that occurs in C will eventually return to its caller B with a reduced occupancy. This will lead to reduced spilling during the subsequent call to D, as explained in more detail in Example 6. The local reserve gain after the call to C at instruction  $B_4$  thus gives the above edge weight. The same applies for the call from B to D. Here, the local reserve gain at instruction  $B_6$  yields the edge weight 0, since no additional function calls appear after that instruction. The global reserve gain at C thus evaluates to 2(0+0+2), which correspond to the length of the path from the call graph's root to the node representing the function. For all other functions the global gain simply evaluates to 0.

### 3.2.4 Context restore costs

The total context restoration costs are then bounded by accumulating the individual costs for space allocation, the explicit and implicit transfer of cache blocks at sens instructions (locally and globally). In addition, the preemption costs are partially amortized by the reduced spilling at sres instructions (locally and globally). Note that f(i) denotes the function containing instruction i:

$$restoreCost(i) = allocationCost(i) (Eq.6) + transferCost(i) (Eq.9) + ensureCostLocal(i) (Eq.12) + ensureCost(f(i)) (Eq.13) - reserveGainLocal(i) (Eq.19) - reserveGain(f(i)) (Eq.20) (21)$$

Example 8 Consider again the preemption point at instruction  $C_3$  in the code shown in Fig. 1. The context restoring analysis first determines the minimal/maximal offset of the DP and RP with regard to ST respectively (Eqs. 3 and 7). The RP offset is 0, due to the absence of lds and sts instructions in the code, which are omitted for brevity. DP on the other hand, is equal to 1, since all data is dead right before the sfree instruction  $C_4$ . Therefore a single block has to be allocated to properly rebuild C's stack frame, i.e.,  $allocationCost(C_3) = 1$ . Since all data of the current stack frame is dead, neither an explicit memory transfer nor an implicit restoration by an sens instruction is necessary, i.e.,  $transferCost(C_3) = 0$  and  $ensureCostLocal(C_3) = 0$ .

After returning to its caller, the ensure instruction  $B_5$  has to restore the entire stack frame of B. The additional cost has not been considered by the bound provided by the standard SCA ( $\langle 0 \rangle$ ). The instruction thus fills an additional cache block. The sens instruction  $A_4$ , on the other hand, restores all of A's cache blocks for free ( $\langle 2 \rangle$ ). Therefore, the global ensure cost accounts for the transfer of an additional cache block (ensure Cost ( $\mathbf{C}$ ) = 1), as illustrated before by Example 5.

As  $\mathbf{C}$  does not call any other function, it cannot profit from a local reserve gain  $(reserveGainLocal(C_3) = 0)$ . However, the analysis determines the potential gain for function calls after returning from  $\mathbb{C}$ . The occupancy before the call to  $\mathbf{D}$  is reduced by 2 blocks compared to a regular execution. The local gain associated with the corresponding call site is thus 2. Since there is no other subsequent call in  $\mathbf{B}$  nor in  $\mathbf{A}$ , no further gain can be considered. The global reserve gain for function  $\mathbf{C}$  thus amounts to 2 cache blocks  $(reserveGain(\mathbb{C}) = 2)$ , as shown in Example 7.

The total cost, associated with context restoration after a preemption at the indicated program point  $C_3$ , is thus given by 1 + 0 + 0 + 1 - 0 - 2 = 0, assuming unit costs of  $\widehat{c}_a = \widehat{c}_s = \widehat{c}_r = 1$ .

### 3.3 Computational complexity

The overall complexity of the CSA and CRA depends on the various analysis steps, which consist of four classes of analysis problems: (1) function-local data-flow anal-

yses, (2) longest path searches on the CG, (3) shortest path searches on the CG, and finally (4) shortest path searches on the CFG of individual functions.

We assume that the data-flow equations of the various DFAs are solved using a traditional worklist algorithm, which iterates until a fixed point is reached. Various complexity bounds can be considered for different classes of DFAs, depending on the size of the CFG as well as on characteristics of the analysis domain.

In our case, the domains are essentially natural numbers in the range  $[0, \mathbf{k}]$  (cf. the analyses of the DP, RP, and local filling) or [0, |SC|] (local gain), where k in turn is also bounded by |SC|. The considered analyses are monotone, i.e., the analyzed values steadily increase or decrease until either the minimum or maximum value of the domain is reached. This is called the height of the domain, which can be bounded by |SC| for all considered DFAs.

The iterative worklist algorithm then propagates the domain values along the control-flow edges in the CFG. This leads to a first, conservative, complexity bound for the previously described analyses, which is in O(|E||SC|) considering the height of the domain |SC| and a CFG with |E| edges. Another bound can be derived using the loop connectedness of the reversed CFG (since all considered problems are backward problems). This parameter characterizes the nesting of loops in a CFG G with respect to a spanning tree T of G (Hecht and Ullman 1973; Kam and Ullman 1976) and usually is denoted as d(G, T). The number of iterations performed by the worklist algorithm can be bounded by this parameter when the order in which the CFG edges are processed is well chosen. The iterative processing may then process each CFG edge at most d(G, T) + 3 times, resulting in a complexity bound of O(|E|(d(G, T) + 3)), where |E| again denotes the number of CFG edges in the CFG G. The loop connectedness can be considered constant in practice (since loops tend to have a simple structure). Similarly, the size of the stack cache |SC| can be considered constant with regard to the analysis problems. The overall complexity of all the previously described DFAs is thus linear in the size of the CFGs of the individual functions in the program under analysis.

The global ensure analysis relies on longest path searches on the CG in order to bound the cost induced by implicit memory transfers of sens instructions. For programs with recursion (which are often forbidden in the context of real-time systems) this requires the construction of an ILP (similar to the well-known IPET approach by Li and Malik (1995)) for each node of the CG. The ILPs are subsequently solved by an external solver (such as CPLEX or LPSolve). While it is possible to bound the complexity of constructing an ILP in linear time with respect to the size of the CG, it is difficult to bound the solving times. Integer linear programming in general is NP-hard. However, it appears that today's solvers are able to handle the problem instances we encountered in our experiments quite well. The solvers almost instantly provide an optimal solution—even open-source solvers that do not apply sophisticated heuristics. For programs without recursion, the longest path search for all functions can be performed in O(|F| + |A|) (Cormen et al. 2009), where |F| represents the number of functions in the CG and |A| the number of call sites. Note, furthermore, that the two approaches can be combined, i.e., dynamic programming is applied to a reduced CG where cyclic regions are collapsed. The potentially expensive ILP solving can then be limited to the recursive functions only (Jordan et al. 2013).

The shortest path searches on the CG (global reserve gain) and the CFGs of individual functions (local reserve gain) can be performed in quadratic time in the size of the respective graphs using simple algorithms. More advanced algorithms allow to reduce the complexity to almost linear time, e.g., the algorithm of Thorup (2004) yields a complexity in  $O(|E| + |V| \log \log |V|)$ . The local reserve gain can thus be computed in almost linear time with regard to the size of the CFGs of individual functions. The same applies to the global reserve gain, which can be computed in almost linear time with regard to the number of functions and call sites in the program. These bounds are independent from the graphs' shape, which may well contain cycles, i.e., loops in the case of CFGs or recursion in the CG.

The complexity of the proposed CSA and CRA analyses thus is dominated by the longest/shortest path searches, whose complexity depends on the size of the program under analysis (both in terms of function size as well as the size of the CG). Lastly, the complexity of the standard SCA needs to be taken into consideration, since intermediate results of this analysis are reused in various analysis steps of the CSA and CRA. The SCA is similarly based on longest/shortest path searches that are combined with function-local DFAs. The complexity analysis for the SCA is almost identical to the discussion from above (Jordan et al. 2013). The overall complexity to compute the preemption costs is thus not impacted and is also dominated by the longest/shortest path searches.

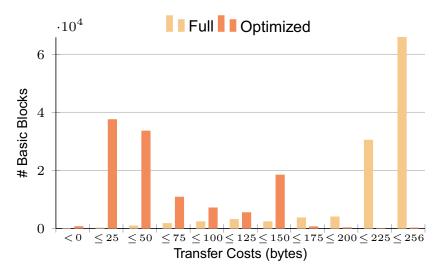

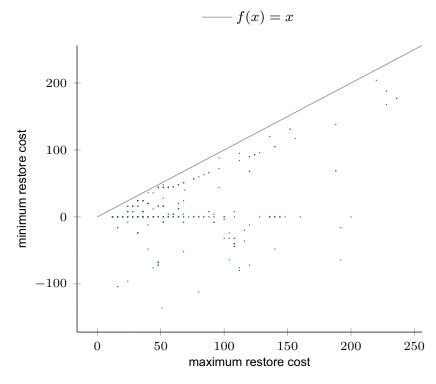

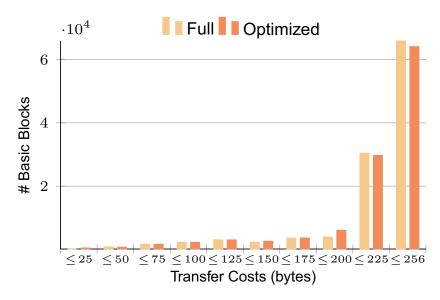

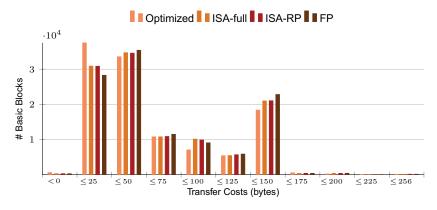

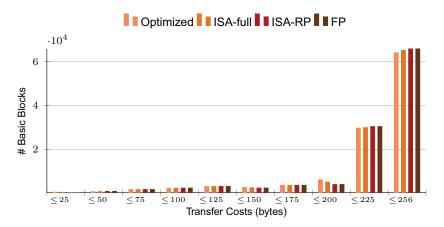

#### 3.4 Discussion