# SOS

# An innovative secure system architecture

Michel Agoyan, Bruno Robisson, Minh Huu Nguyen CEA LETI /DSIS/LCS/SAS Pirouz Bazargan-Sabe UPMC-LIP6 Guillaume Phan TRUSTED-Logic Sébastien Le Henaff VIACCESS

#### CEA-LETI/DSIS/SCME/CCS SAS Systèmes et Architectures Sécurisés

Viaccess . TV, internet, mubile. In total confidence.

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ >

leti

# Cryptarchi June 2010

michel.agoyan@cea.fr SOS An innovative secure system architecture

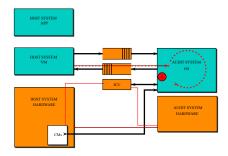

- 2 Hardware architecture

- 3 Hardware CMs

- 4 Design method

- 5 Conclusion

(I) < ((()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) <

# The project

# Purpose

- Propose an innovative secure system architecture for embedded device such as smart card and prove it.

- An innovative secure system architecture to :

- Help the design of the security strategy

- Improve the smartness of the security strategy

- Reconcile availability with security

- Improve the performance

#### The concept

michel.agoyan@cea.fr SOS An innovative secure system architecture

#### The concept

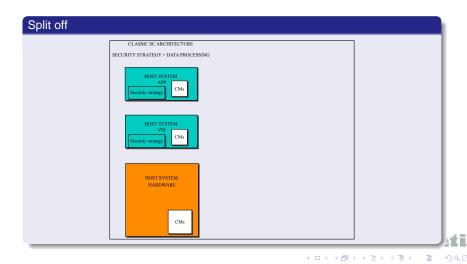

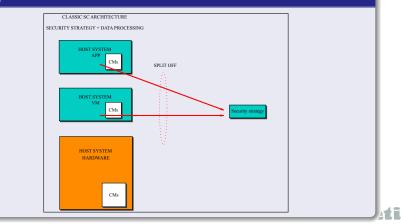

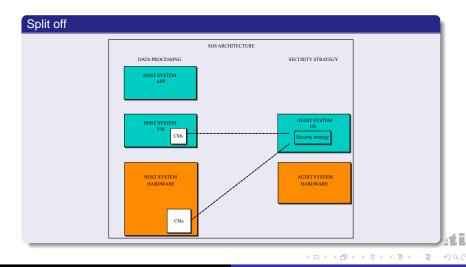

# Split off

michel.agoyan@cea.fr SOS An innovative secure system architecture

イロト イ理ト イヨト イヨト

2

#### The concept

# Split off

# Advantages

- Regroup all the security management under the responsibility of an unique entity

- Security policy more flexible, adaptable

- Opportunity to design a smarter security policy

- $\bullet\,$  Fault attacks path more complex  $\rightarrow\,$  increase the security level

- Improve the performance  $\rightarrow$  2 systems running in parallel

Fit the initial main objectives

#### Drawbacks

- Impact on the cost

- New concept  $\rightarrow$  new paths for attack?

# The model

# Why?

- Practical approach to test the concept

- Prove it

# How?

Choose an application requiring different security levels and performance → pay tv

# • Conditional Access System :

- Principle : digital audio/video stream can be unscrambled if the right is owned by the smart-card.

- 3 main classes of command are used by the CAS :

- Subscription management (keys & rights writing) : Very sensitive

- Unscrambling (generating a control word) : Sensitive

- Subscriber operations (parental control) : Not very sensitive

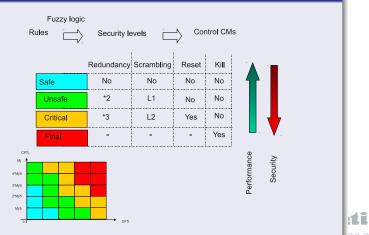

#### security policy

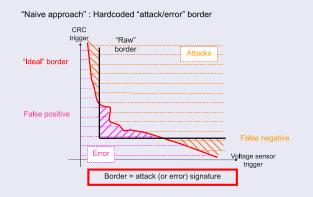

# The challenge : availability versus security

\ti

#### security policy

# Graduated reaction

michel.agoyan@cea.fr SOS An innovative secure system architecture

- 2 Hardware architecture

- 3 Hardware CMs

- 4 Design method

- 5 Conclusion

イロト イポト イヨト イヨト

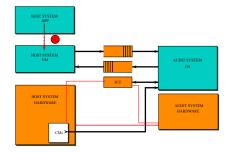

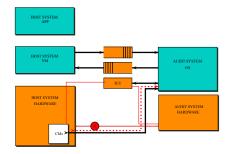

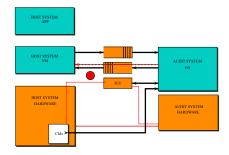

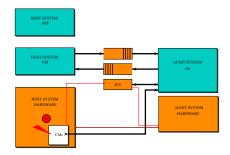

# $HS \leftrightarrow AS$ communication : normal exec

App requests to the VM a security level

michel.agoyan@cea.fr SOS An innovative secure system architecture

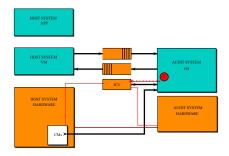

# $\text{HS} \leftrightarrow \text{AS communication}: \text{normal exec}$

App requests to the VM a security level VM forwards the request to AS

michel.agoyan@cea.fr SOS An innovative secure system architecture

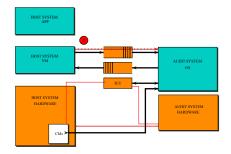

# $\text{HS} \leftrightarrow \text{AS communication}: \text{normal exec}$

michel.agoyan@cea.fr SOS An innovative secure system architecture

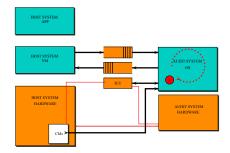

#### $HS \leftrightarrow AS$ communication : normal exec

michel.agoyan@cea.fr SOS An innovative secure system architecture

#### $HS \leftrightarrow AS$ communication : normal exec

michel.agoyan@cea.fr

#### SOS An innovative secure system architecture

#### $HS \leftrightarrow AS$ communication : normal exec

michel.agoyan@cea.fr

SOS An innovative secure system architecture

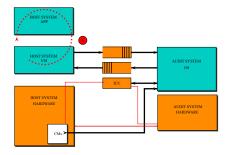

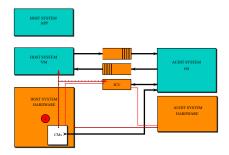

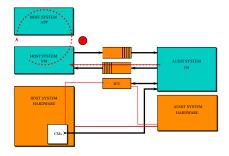

# $HS \leftrightarrow AS$ communication : sensor event

A sensor event occurs

michel.agoyan@cea.fr SOS An innovative secure system architecture

# $HS \leftrightarrow AS$ communication : sensor event

A sensor event occurs

An interruption is raised on HS and AS through the ICU

michel.agoyan@cea.fr SOS An innovative secure system architecture

# $HS \leftrightarrow AS$ communication : sensor event

A sensor event occurs

An interruption is raised on HS and AS through the ICU

Depending on current context AS computes the actions to perform.

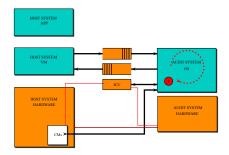

#### $HS \leftrightarrow AS$ communication : sensor event

michel.agoyan@cea.fr SOS An innovative secure system architecture

#### $HS \leftrightarrow AS$ communication : sensor event

A sensor event occurs

An interruption is raised on HS and AS through the ICU

Depending on current context AS computes the actions to perform.

AS could decide to parameter some hardware CMs

**ti**

AS waits for HS interruption ack

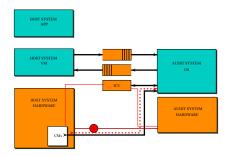

#### $HS \leftrightarrow AS$ communication : sensor event

A sensor event occurs

An interruption is raised on HS and AS through the ICU

Depending on current context AS computes the actions to perform.

AS could decide to parameter some hardware CMs

:**t**i

AS waits for HS interruption ack

AS clears the interruption

michel.agoyan@cea.fr SOS An innovative secure system architecture

# $HS \leftrightarrow AS$ communication : sensor event

A sensor event occurs

An interruption is raised on HS and AS through the ICU

Depending on current context AS computes the actions to perform.

AS could decide to parameter some hardware CMs

AS waits for HS interruption ack

AS clears the interruption

AS could also asks to VM to apply software CMs and resumes the execution

michel.agoyan@cea.fr

SOS An innovative secure system architecture

michel.agoyan@cea.fr SOS An innovative secure system architecture

イロト イポト イヨト イヨト

# Interface

# Follows the basic rule of SOS : "Split off"

- Sensitive data are processed by the Host System  $\Rightarrow$  HS embeds CMs

- Security is under the control of the Audit System ⇒ AS controls CMs

- Rem : To demonstrate SOS concept ⇒ chose hardware CMs that are parametrable, switchable, and have an impact on cpu performance

### Hardware interface

- 4KB dedicated to map CMs registers into memory space of AS

- A control register : on/off + parameter

- A status register

- Interrupts from the sensors into the Host system are routed to the Interrupt Control Unit of the Audit system

\ti

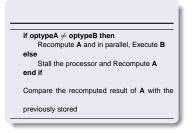

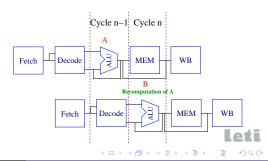

#### ALU protection against fault attacks

### Principle

Based on Idle Hardware : ALU = ∑ Functional Units (Adder, multiplier, shifter) ⇒ Time redundancy

# ALU protection against fault attacks : Results

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ >

# Hardware overhead

|                    | Number of Slices | Max Clock Period (ns) |

|--------------------|------------------|-----------------------|

| Base ALU           | 2146             | 1.050                 |

| Fault tolerant ALU | 2584             | 1.056                 |

|                    | (+20.4%)         | (+0.57%)              |

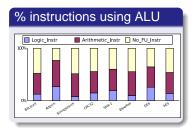

# **Random Instruction Injection**

# A command register programmable by the Audit System

- Based on : Injecting random instructions at random places during the execution [Smart Random Code Injection to Mask Power Analysis Based Side Channel Attacks, Jude Angelo Ambrose, University of New South Wales Sydney, Australia]

- Setting and clearing a flag delimit the block frame to protect

- SET\_FLAG : starts to generate random instructions

- N : the maximum number of random instructions injected between two regular instructions

- D : the maximum number of regular instructions skipped

- *RESET\_FLAG* : stops the injection of random instructions

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ >

# **Random Instruction Injection**

# A command register programmable by the Audit System

- Based on : Injecting random instructions at random places during the execution [Smart Random Code Injection to Mask Power Analysis Based Side Channel Attacks, Jude Angelo Ambrose, University of New South Wales Sydney, Australia]

- Setting and clearing a flag delimit the block frame to protect

- SET\_FLAG : starts to generate random instructions

- N : the maximum number of random instructions injected between two regular instructions

- D : the maximum number of regular instructions skipped

- *RESET\_FLAG* : stops the injection of random instructions

# Limitation of random instruction set

random register combined with zero register result written back to same random register : ADD \$3, \$3, \$0

# Random Instruction Injection : Implementation

#### Issue

• if the injected instruction uses a register containing a sensitive data  $\rightarrow$   $\nearrow$  leakage information

(I) < ((()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) < (()) <

# Random Instruction Injection : Implementation

# Issue

• if the injected instruction uses a register containing a sensitive data  $\rightarrow$   $\nearrow$  leakage information

# Solution

- Use 2 register files : the main register file **M** and the register file **R** with random values

- Inject a random instruction using operands of R

#### example

- ADD R5,R3,R0  $\rightarrow$  normal instruction

- ADD R5,R7,R8  $\rightarrow$  random instruction

### Random Instruction Injection : Results

#### Trivial DPA on VCDs with CM

#### Hardware overhead

|     | Slices reg | Slices LUT | used as logic | used as ram | Max Clock Period (ns) |

|-----|------------|------------|---------------|-------------|-----------------------|

| RII | 2367       | 4568       | 4546          | 22          | 5.6ns                 |

| RII | 3625       | 5413       | 5391          | 22          | 7 ns                  |

|     | 53%        | 18%        | 18%           | 0%          |                       |

# Plan

- 2 Hardware architecture

- 3 Hardware CMs

イロト イポト イヨト イヨト

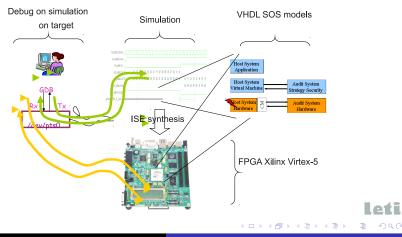

### The design flow

# **Testing SOS**

- The security policy is tested using hardware emulation for fault injection

- $\Rightarrow$  rules improvement

- 2 Hardware architecture

- 3 Hardware CMs

- 4 Design method

michel.agoyan@cea.fr SOS An innovative secure system architecture

イロト イポト イヨト イヨト

# SOS to be continued...

# Security Policy

- The project finishes at the end of 2010.

- The basic framework to build a smarter security is already available.

- Implementation for different applications is possible.

- These new implementations will help us to improve and validate the concept

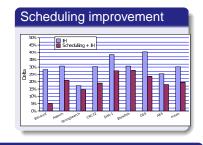

# Performance

- The main concern of the first implementation of the communication protocol is the security policy in spite of the performance

- So there are opportunities to exploit the parallelism of the architecture and to reveal the performance